## Enabling Emerging, Heterogeneous Memory Systems

#### Citation

Pentecost, Lillian. 2022. Enabling Emerging, Heterogeneous Memory Systems. Doctoral dissertation, Harvard University Graduate School of Arts and Sciences.

#### Permanent link

https://nrs.harvard.edu/URN-3:HUL.INSTREPOS:37372073

#### Terms of Use

This article was downloaded from Harvard University's DASH repository, and is made available under the terms and conditions applicable to Other Posted Material, as set forth at http://nrs.harvard.edu/urn-3:HUL.InstRepos:dash.current.terms-of-use#LAA

## **Share Your Story**

The Harvard community has made this article openly available. Please share how this access benefits you. <u>Submit a story</u>.

**Accessibility**

#### HARVARD UNIVERSITY

#### Graduate School of Arts and Sciences

#### DISSERTATION ACCEPTANCE CERTIFICATE

The undersigned, appointed by the

Harvard John A. Paulson School of Engineering and Applied Sciences have examined a dissertation entitled:

"Enabling Emerging, Heterogeneous Memory Systems"

presented by: Lillian Coston Pentecost

Signature \_

Typed name: Professor D. Brooks

Signature \_\_\_\_

Typed name: Professor G. Wei

Signature For Frosessor G. Hills

## Enabling Emerging, Heterogeneous Memory Systems

A DISSERTATION PRESENTED

BY

LILLIAN COSTON PENTECOST

TO

THE DEPARTMENT OF COMPUTER SCIENCE

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

IN THE SUBJECT OF

COMPUTER SCIENCE

Harvard University Cambridge, Massachusetts April 2022 ©2022 – LILLIAN COSTON PENTECOST ALL RIGHTS RESERVED.

## Enabling Emerging, Heterogeneous Memory Systems

#### **ABSTRACT**

Optimizing data storage and data movement remain critical roadblocks to overall computing performance and efficiency. These barriers are due to a convergence of motivating factors that begins with the memory wall and limitations of well-established memory technologies and design paradigms, and is compounded by increasingly data-intensive applications. This shift can and should be answered by many research thrusts to address the density and efficiency of memory systems, including technological heterogeneity in on-chip memory, increased specialization and cross-computing-stack choices in system and device design, and re-thinking the relationship and co-location of memory and compute resources. This thesis proposes and evaluates both specific solutions and broad design methodologies, uncovering enormous potential for increased memory system efficiency while unlocking numerous doors for further exploration and innovation.

## Contents

| Tı | TLE P                                                  | AGE                                                            | i   |

|----|--------------------------------------------------------|----------------------------------------------------------------|-----|

| Co | OPYRI                                                  | GHT                                                            | ii  |

| Аı | BSTRA                                                  | CT                                                             | iii |

| TA | ABLE C                                                 | OF CONTENTS                                                    | iv  |

| Lı | STING                                                  | of Figures                                                     | vi  |

| A  | CKNO                                                   | WLEDGMENTS                                                     | ix  |

| Pr | EVIO                                                   | us Work                                                        | хi  |

| 0  | Introduction                                           |                                                                | I   |

|    | 0.0                                                    | Publications & Research Experiences                            | 2   |

|    | 0.I                                                    | Thesis Contributions                                           | 4   |

|    | 0.2                                                    | Thesis Organization                                            | 7   |

| I  | Background: Memory Technologies & How to Leverage Them |                                                                | 9   |

|    | 1.0                                                    | Motivation: Limitations of Today's Memory Systems              | 10  |

|    | I.I                                                    | Motivation: Data-Intensive Applications                        | 17  |

|    | 1.2                                                    | Embedded, Non-Volatile Memory (eNVM) Technology Landscape      | 22  |

|    | 1.3                                                    | Identifying Cross-Stack Design Considerations                  | 32  |

| 2  | Reliability as a First-Order Design Concern            |                                                                |     |

|    | 2.0                                                    | Application-Aware Resilience Studies                           | 38  |

|    | 2.I                                                    | Fault Modeling of Multi-Level-Cell (MLC) eNVMs                 | 50  |

|    | 2.2                                                    | Customized, Iso-Accuracy MLC storage of DNN weights            | 58  |

|    | 2.3                                                    | Fault Tolerance In-the-Loop with Sparsity and Error Mitigation | 64  |

|    | 2.4                                                    | MLC FeFET Memory for DNN Inference and Graph Processing        | 71  |

| 3  | Max                                                              | NVM: Maximizing Memory Efficiency for ML Accelerators            | 87  |

|----|------------------------------------------------------------------|------------------------------------------------------------------|-----|

|    | 3.0                                                              | End-to-End, Co-Design Methodology for MLC eNVM                   | 90  |

|    | 3.I                                                              | Maximizing Storage Density and Inference Efficiency (Evaluation) | 93  |

|    | 3.2                                                              | MEMTI: Optimizing eNVM for Visual Multi-Task Inference           | 105 |

|    | 3.3                                                              | EdgeBERT: Optimizations for Multi-Task NLP Inference             | 115 |

| 4  | NVMExplorer: Cross-Stack Memory Design and Optimization          |                                                                  |     |

|    | 4.0                                                              | An Efficient, Extensible Design Space Exploration Framework      | 123 |

|    | 4.I                                                              | Supporting DNN Inference Under Varying Operating Conditions      | 138 |

|    | 4.2                                                              | Complementing and Accelerating Graph Processing                  | 143 |

|    | 4.3                                                              | Probing General-Purpose Applications: eNVM as LLC                | 147 |

|    | 4.4                                                              | Case studies in eNVM, System, and Application Co-Design          | 150 |

| 5  | Conclusion: Future Memory System Opportunities and Innovations 1 |                                                                  |     |

|    | 5.0                                                              | Themes to Unlock Future Memory Efficiency                        | 158 |

|    | 5.1                                                              | Innovations on the Horizon, and How to Leverage Them             | 162 |

|    | 5.2                                                              | Summary: Cross-Computing-Stack Memory Efficiency Opportunities   | 165 |

| Re | FERE                                                             | NCES                                                             | 193 |

## Listing of figures

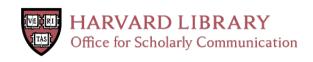

| 1.0  | Memory Technology Hierarchy (Schematic)                          | Ι2  |

|------|------------------------------------------------------------------|-----|

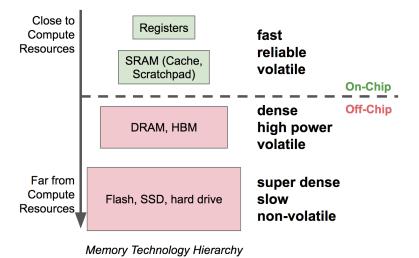

| I.I  | Example Memory Array Organization (Schematic)                    | 14  |

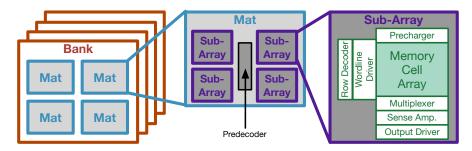

| I.2  | Energy and Latency of Memory Array Access, SRAM (Example)        | 15  |

| 1.3  | Deep Neural Network Layer Schematic (Examples)                   | 19  |

| 1.4  | eNVM Publication Survey (2016-2020) Summary                      | 28  |

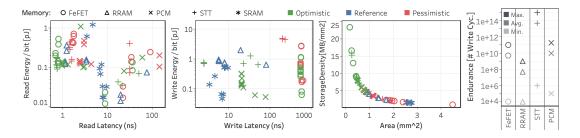

| 1.5  | eNVM Projected Array Comparison (2017)                           | 3 I |

| 1.6  | Example of Interdependent Design Choices (Schematic)             | 33  |

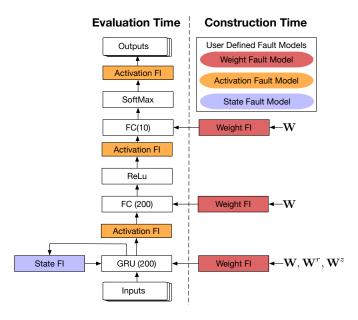

| 2.0  | Ares Method Schematic                                            | 4 I |

| 2.I  | Ares Fault Injection Schematic                                   | 42  |

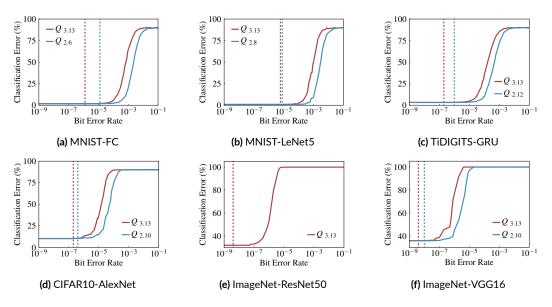

| 2.2  | Ares Per-DNN-Model Fault Tolerance Results                       | 44  |

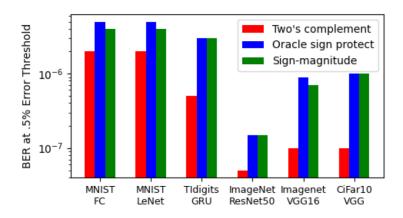

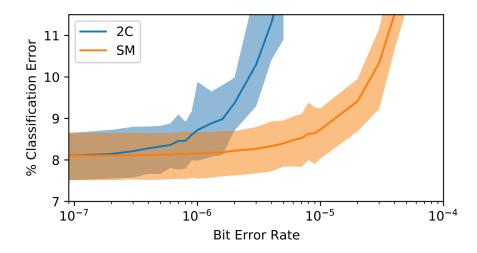

| 2.3  | Resilience of Datatype of DNN Weights                            | 47  |

| 2.4  | Fault Tolerance Across DNN Training Runs                         | 49  |

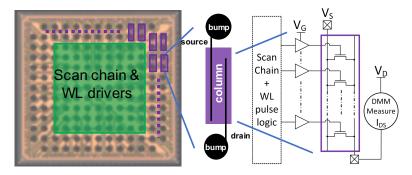

| 2.5  | Multi-Level-Cell (MLC) CTT Test Chip                             | 5 I |

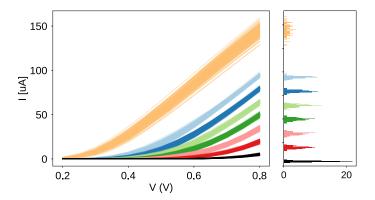

| 2.6  | Multi-Level-Cell (MLC) CTT Test Chip Measurements                | 52  |

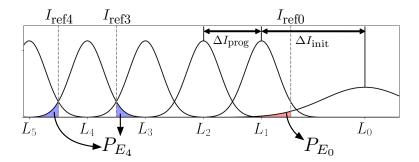

| 2.7  | Multi-Level-Cell (MLC) Programming (Cell-Level Schematic)        | 53  |

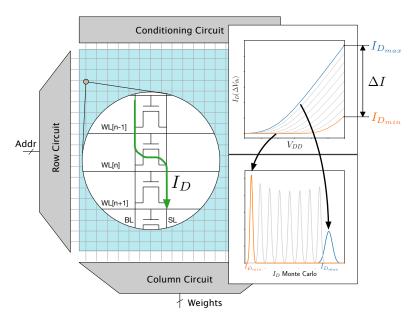

| 2.8  | Multi-Level-Cell (MLC) Programming (Array-Level Schematic)       | 55  |

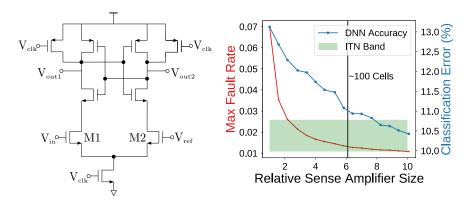

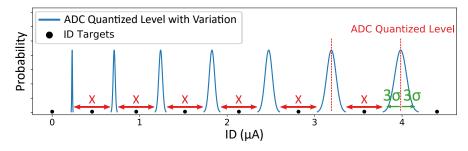

| 2.9  | Multi-Level-Cell (MLC) Programming Reliability Impact of the ADC | 56  |

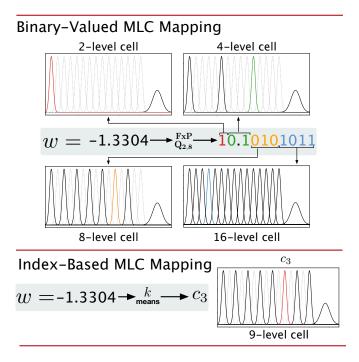

| 2.10 | Multi-Level-Cell (MLC) Programming (Schematic)                   | 59  |

| 2.II | DNN Weight Storage Results, Fixed Point Encoding                 | 60  |

| 2.12 | DNN Weight Storage Results, Clustered Encoding                   | 62  |

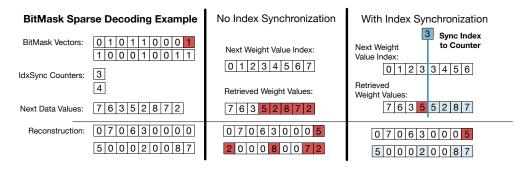

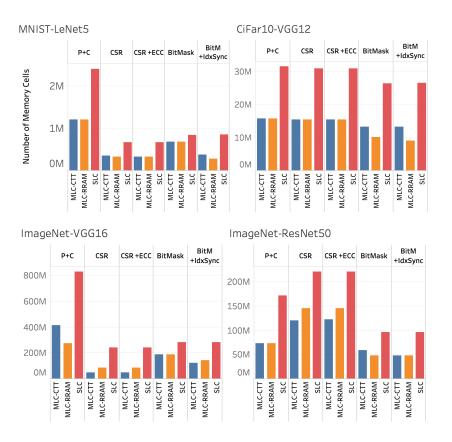

| 2.13 | Index Synchronization for Bitmask Error Mitigation               | 67  |

| 2.14 | Resilience of Sparse-Encoded Data to Faults                      | 69  |

| 2.15 | Optimal Sparse Encoding and Error Mitigation Strategies          | 70  |

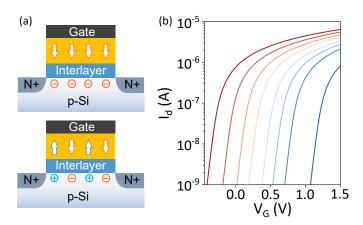

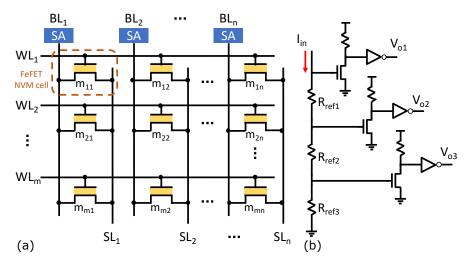

| 2.16 | FeFET Device Diagram and MLC-3 Characterization                  | 72  |

| 2.17 | FeFET Array Architecture Details                                 | 73  |

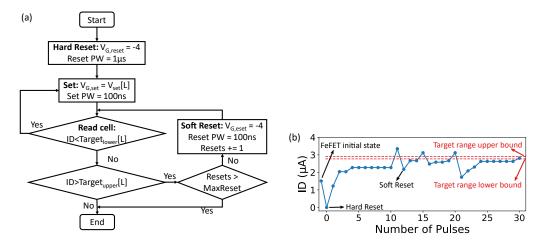

| 2.18 | FeFET MLC Programming Schematic                                  | 76  |

| 2.19 | FeFET MLC Programming Details                                    | 78  |

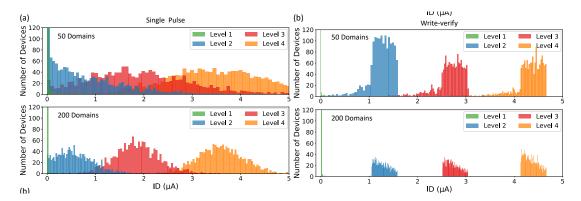

| 2.20 | FeFET MLC Programming Device Results                             | 79  |

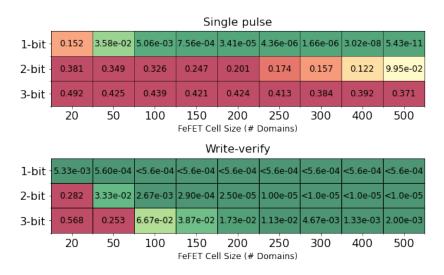

| 2.2I | FeFET Fault Rate Shmoo Plot                                      | 81  |

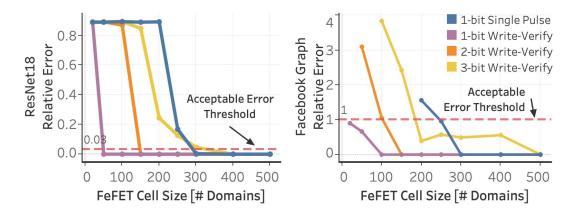

| 2.22 | FeFET Application Accuracy                                       | 82  |

| 2.23  | FeFET Co-Design ALBERT Array Details                   | 8 9   |

|-------|--------------------------------------------------------|-------|

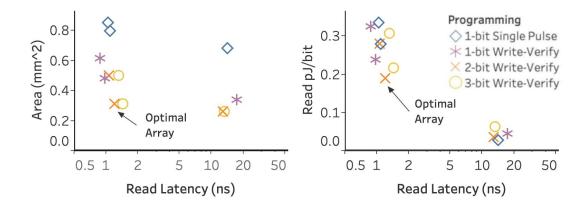

| 3.0   | MaxNVM Methodology                                     | 91    |

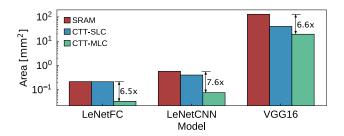

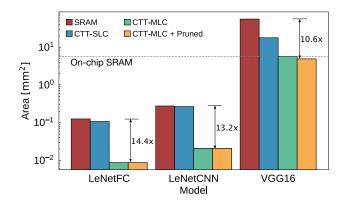

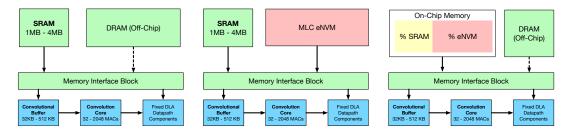

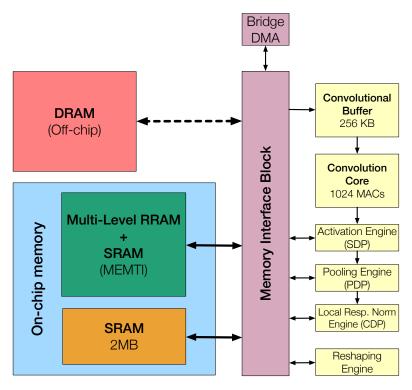

| 3.I   | MaxNVM Architecture Block Diagrams                     | 94    |

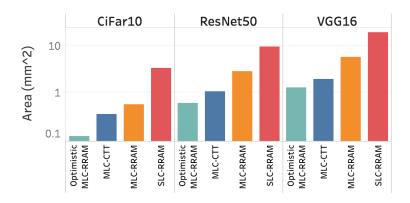

| 3.2   | MaxNVM On-Chip DNN Inference Memory Array Area         | 90    |

| 3.3   | MaxNVM On-Chip DNN Inference Memory Array Read Energy  | 97    |

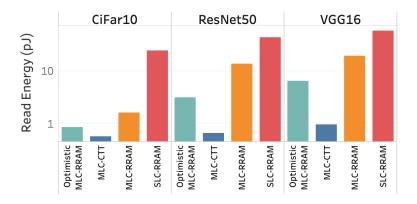

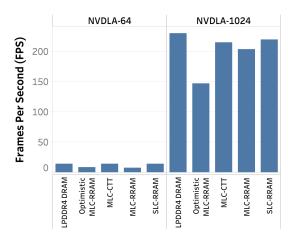

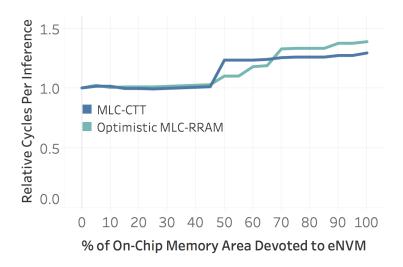

| 3.4   | MaxNVM On-Chip DNN Inference Results, Performance      | 98    |

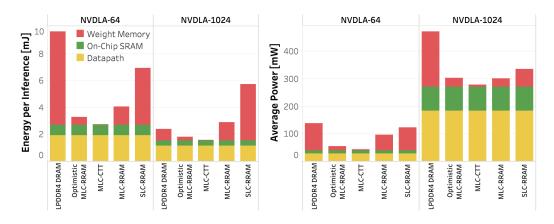

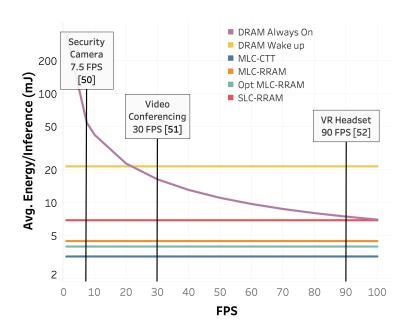

| 3.5   | MaxNVM On-Chip DNN Inference Results, Power/Energy     | 99    |

| 3.6   | MaxNVM Iso-Area Performance Results                    | 101   |

| 3.7   | MaxNVM Intermittent Operation Results                  | 103   |

| 3.8   | MEMTI Architecture Block Diagram                       | 109   |

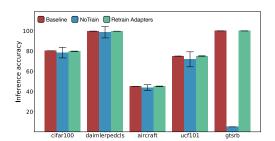

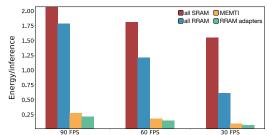

| 3.9   | MEMTI Accuracy and Energy Results                      | 113   |

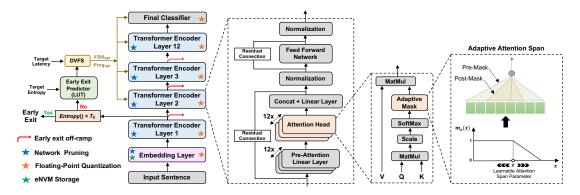

| 3.10  | EdgeBERT Design Elements, Optimizations                | 119   |

| 3.11  | EdgeBERT Memory Optimization Results                   | 118   |

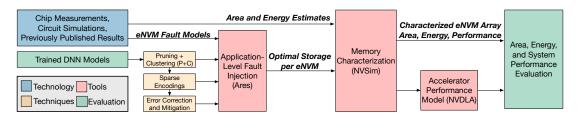

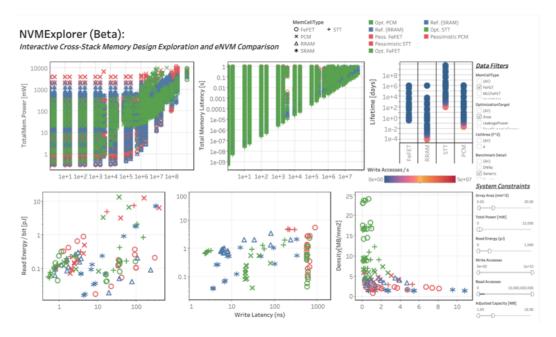

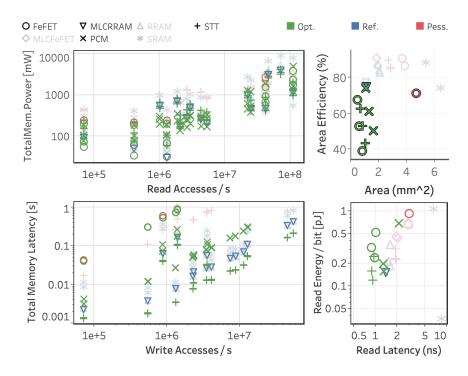

| 4.0   | NVMExplorer Methodology Overview                       | 123   |

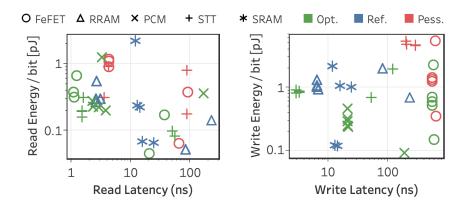

| 4.I   | NVMExplorer Example Array Characterization             | 127   |

| 4.2   | NVMExplorer Data Dashboard Snapshot                    | 129   |

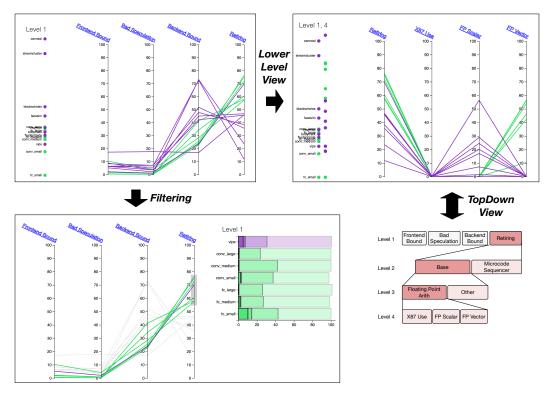

| 4.3   | CHAMPVis Data Dashboard                                | 131   |

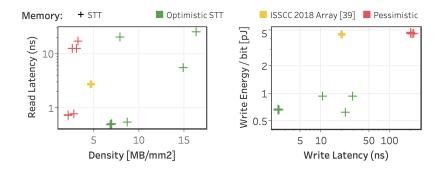

| 4.4   | NVMExplorer Array-Level Validation                     | 137   |

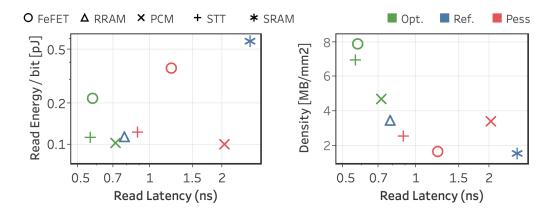

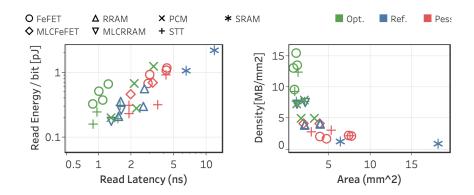

| 4.5   | NVMExplorer DNN Array-Level Metrics                    | 139   |

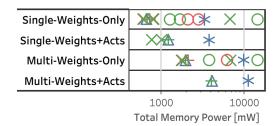

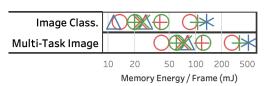

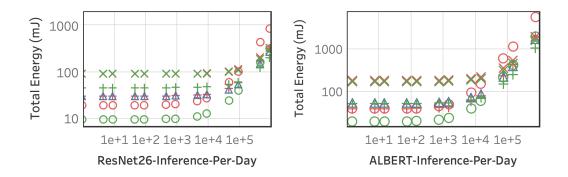

| 4.6   | NVMExplorer DNN Power, Energy-per-Inference            | 140   |

| 4.7   | NVMExplorer Intermittent DNN Operation                 | 142   |

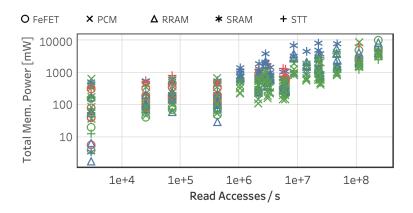

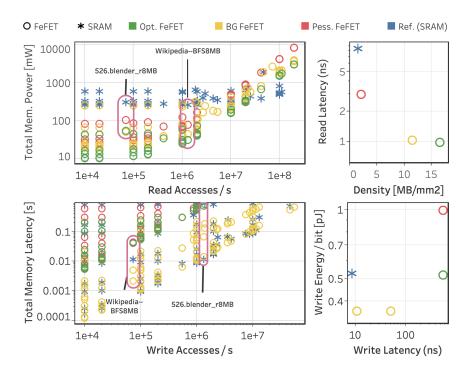

| 4.8   | NVMExplorer Graph Processing Results Power             | 144   |

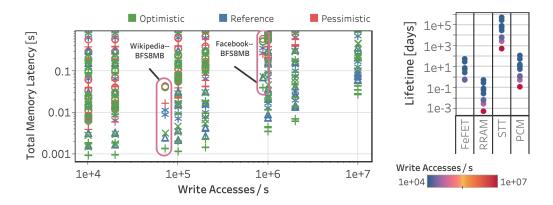

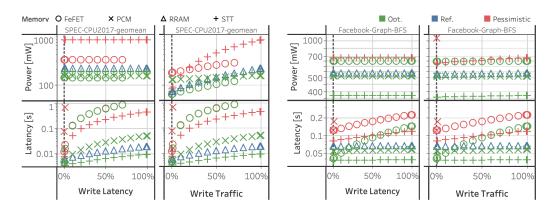

| 4.9   | NVMExplorer Graph Processing Results Latency, Lifetime | 149   |

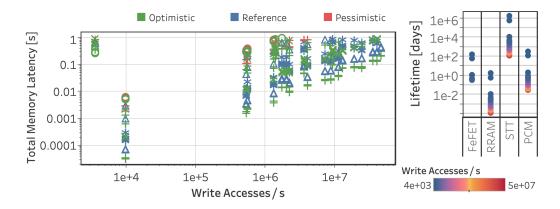

| 4.10  | NVMExplorer LLC Array-Level Metrics                    | 148   |

| 4.I I | NVMExplorer LLC Case Study Power                       | 149   |

| 4.12  | NVMExplorer LLC Case Study Latency, Lifetime           | 150   |

| 4.13  | NVMExplorer BEOL FeFET Comparison                      | 151   |

| 4.14  | NVMExplorer Area Efficiency Trade-Off                  | 153   |

| 4.15  | NVMExplorer Write Buffer Study                         | 154   |

| 1 16  |                                                        | T = 1 |

I dedicate this work to my endlessly supportive family and friends.

## Acknowledgments

I HAVE MANY PEOPLE to thank who have supported me over the past six years and who have help shaped me as a researcher and a scientist.

First, thank you to my advisors, David and Gu, who have been champions of my research and helped me build confidence and perspective throughout my PhD. You've given me space, time, and guidance to explore my many interests in and out of computer architecture and encouraged me in dabbling across research areas and projects, which has made my time as a PhD student immensely enjoyable and made the kind of research I do uniquely possible. It has been a pleasure to work with you both as the research group has grown and changed in exciting ways over the years.

Next, I'd like to thank Professor Gage Hills for sitting on my dissertation committee. It has been such a treat to hear your thoughts on my work and see your success at Harvard, and I appreciate the time and energy you bring to group meetings and research discussions. I'd also like to thank Professors Sasha Rush and James Mickens for serving on my qualification committee and providing feedback and encouragement at a time when I was awash in paper rejections. I've felt very fortunate to be surrounded by knowledgeable and thoughtful researchers throughout my time at Harvard.

Next, I'd like to thank my fellow graduate students and close collaborators at Harvard who have made my work possible and (crucially) kept me engaged, excited, and accountable in project collaborations over the years. To my favorite sounding-board and close friend Udit Gupta, it has been such a joy to grow as researchers and figure out our goals alongside each other. Thanks for being such a steadfast and creative collaborator, delightful co-worker, and, of course, diligent email-proofreader as we have organized events and coordinated projects together over the years. A special thank you also to other mentors I've been fortunate to cross paths with, namely Brandon Reagen for teaching me how to be a grad student and how to have a conversation with David and Gu, and Akshitha Sriraman for sitting me down and asking me to think critically about my research style and my research goals. Thank you to Marco Donato for working closely with me on many, many projects. I continue to learn a ton from you, and I'm very glad to know you as a mentor, a collaborator, and a peer. Thank you also to the many other graduate students and friends who made my time at Harvard productive and fun, to Thierry Tambe for being constantly impressive and generous with time and effort, to Siming Ma for sharing expertise (and data!), to Abdulrahman Mahmoud for refreshing and relatable perspectives and insights, to Brian Plancher for mind-melding about teaching and career goals, and many, many others who I won't list but who have shaped my last six years. I've also

had the pleasure of working with numerous undergraduate researchers over the years, and I continue to be so impressed and refreshed by the perspectives they bring. And, a special thank you to Glenn Holloway for many patient emails and direct support making this research possible.

Thank you to research collaborators across institutions as well, including the many wonderful and insightful folks I've met through the ADA center. A special thank you to my co-first-author buddies on some favorite collaborations over the years, namely Mehdi Sharifi at Notre Dame and Alexander Hankin at Tufts. I'd like to especially thank Alex for all your patience and effort putting together NVMExplorer. I appreciate your focus and your enthusiasm (the much-needed optimism to my skepticism at times) and look forward to our continued collaboration.

I've been fortunate to do several research internships, from which I've collected skills, great experiences, and awesome mentors. Thank you to the memory systems research team at IBM, to the AI, Silicon, and Performance team at MSR, and to NVIDIA research for incredible exposure to new research ideas, as well as memorable summer experiences. I'd like to especially thank the team of mentors and collaborators who I've grown close with in the architecture research group at NVIDIA – Aamer Jaleel, Po-An Tsai, Angshuman Parashar, Joel Emer, and Bill Dally, who continue to push me to be a better scientist and a more thoughtful researcher through our conversations.

I would not have been nudged towards computer systems research and, more fundamentally, would not be the person I am today if not for the foundation and the incredible mentors I had as an undergraduate in physics and computer science at Colgate University. A special thank you to John Stratton, who took time to teach me how to read a research paper and how to frame a question. Our work together helped me realize the impact that the right mentor at the right time can have on someone's whole trajectory, and I'm very grateful. Thank you also to Ken Segall and to Elodie Fourquet, whose confidence in me as a student and as a scientist bolstered me in difficult times, and who let me wrestle and have real ownership of research projects as an undergraduate.

Thank you to the Bok Center for Teaching and Learning for support, guidance, and collaboration throughout my experience as a pedagogy fellow. My participation in seminars and critical discussions over the years has been so influential and informative as an academic, a researcher, and an educator and the many ways those roles intersect. A special thank you to John Girash, a wonderful and thoughtful mentor who was a real source of constancy and joy working and teaching together throughout an otherwise challenging and isolating year.

A huge thank you to my family, to my parents who have supported me in every way and been loving and patient throughout. Thanks to Joe and Linda for trivia nights and fun dinners, supplying plenty of beer and good times over the years. Thanks also to my close friends who have been such a special part of my life for so long. There are too many more important people to name, but I'll lastly thank my friend Allison for being a constant companion and great ranting-partner over the years of our PhD programs, and my best friend and concert-buddy Emily for our breakfasts and cake-baking and travels and many fun times together.

Finally, I thank my partner, Sean, for every laugh, every cup of coffee, every proofread and debug session, and for making me so happy, inspired, and thankful through these years of hard work. Also, I thank our precious dog, Mipha, for getting me out of the house every day, and for being the most beautiful, energetic, and talented creature on the planet.

## Previous Work

Portions of this dissertation appeared in the following works:

- L. Pentecost\*, A. Hankin\*, M. Donato, M. Hempstead, G. Wei, D. Brooks. "NVMExplorer: A Framework for Cross-Stack Comparisons of Embedded Non-Volatile Memories" IEEE International Symposium on High-Performance Computer Architecture (HPCA) Proceedings, April 2022. \*Authors contributed equally.

- L. Pentecost\*, M. Sharifi\*, R. Rajaei, A. Kazemi, Q. Lou, G. Wei, D. Brooks, K. Ni, X. Hu, M. Niemier, M. Donato. "Application-Driven Design Exploration for Dense Ferroelectric Embedded Non-Volatile Memories (eNVMs)" ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED 2021), July 2021. \*Authors contributed equally.

- T. Tambe, C. Hooper, L. Pentecost, T. Jia, E. Yang, M. Donato, V. Sanh, P. Whatmough, A. Rush, D. Brooks, G. Wei. "EdgeBERT: Sentence-Level Energy Optimizations for Latency-Aware Multi-Task Natural Language Processing Inference" MICRO-54: 54th Annual IEEE/ACM International Symposium on Microarchitecture, October 2021.

- E. Pyne\*, **L. Pentecost**, U. Gupta, G. Wei, D. Brooks. "Quantifying the impact of data encoding on DNN fault tolerance" Workshop on Performance Analysis of Machine Learning Systems (FastPath at ISPASS 2020), August 2020. \**Undergraduate Mentee*.

- **L. Pentecost**\*, U. Gupta\*, E. Ngan\*, G. Wei, D. Brooks, J. Beyer, M. Behrisch. "CHAMPVis: Comparative Hierarchical Analysis of Microarchitectual Performance Visualization" Workshop on Programming and Performance Visualization Tools at Supercomputing 2019 (ProTools at SC19), November 2019. \**Authors contributed equally*.

- M. Donato, L. Pentecost, D. Brooks, G. Wei. "MEMTI: Optimizing On-Chip Nonvolatile Storage (eNVM) for Visual Multi-task Inference at the Edge" EEE Micro, Vol. 39, Issue 6, November 2019.

- L. Pentecost, M. Donato, B. Reagen, U. Gupta, S. Ma, G. Wei, D. Brooks. "MaxNVM: Maximizing DNN Storage Density and Inference Efficiency with Sparse Encoding and Error Mitigation" 52nd IEEE/ACM International Symposium on Microarchitecture (MICRO-52), October 2019.

B. Reagen, U. Gupta, L. Pentecost, G. Wei, and D. Brooks. "Ares: A Framework for Quantifying the Resilience of Deep Neural Networks" Design Automation Conference (DAC) 2018, June 2018.

M. Donato, B. Reagen, L. Pentecost, U. Gupta, D. Brooks, G. Wei. "On-Chip Deep Neural Network Storage with Multi-Level eNVM" Design Automation Conference (DAC) 2018, June 2018.

I was excited at something new, always liked something new, but give credit to everybody who helped. I didn't do anything alone.

Katherine Johnson, 2017

Introduction

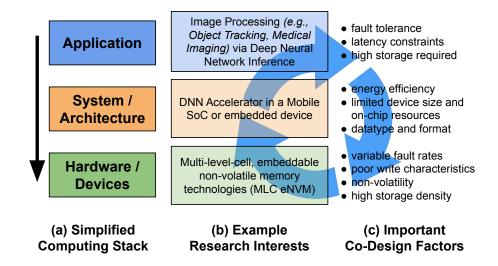

Data movement and data storage remain a critical roadblock to overall computing performance and efficiency. Data-intensive workloads, often running on increasingly heterogeneous systems (i.e., computers that comprise more than one type of processing unit or more than just a general-purpose CPU), would particularly benefit from drastic increases to on-chip memory capacity and storage density, as well as the energy efficiency and performance of memory access, as

discussed in detail in Chapter 1.

This thesis identifies and explores game-changing design choices that could enable substantial gains in future memory systems, and also provides far-reaching approaches to identify additional design choices and optimizations. In a variety of application and system settings, my work reveals that exposing and co-optimizing design choices at different levels of the computing stack (for example, algorithmic optimizations alongside architecture and device-level choices) is the bedrock of future efficiency gains and effective future memory system design. For example, several works presented in this dissertation identify embedded, non-volatile memory (eNVM) technologies as a compelling opportunity to address on-chip memory efficiency, but the design space is complex and each memory cell configuration has unique characteristics that can and should be calibrated to system needs. This work has the dual contribution of proposing and evaluating specific memory system solutions, often specifically designing towards optimal on-chip memory for machine learning hardware accelerators, as well as providing reusable and extensible methods, tools, and takeaways to inform a broader class of future memory systems.

#### 0.0 Publications & Research Experiences

Throughout this dissertation, I will present specific system designs and evaluations and the accompanying methodologies and tools that enable efficient, effective future memory system design and optimization. Much of this work is underpinned and informed by experiences early in my PhD contributing to the design, fabrication, and testing of specialized accelerators for deep neural network (DNN) inference, consistently in tandem with application-level optimizations <sup>243,81</sup>. I was also fortunate to complete research internships in the first half of my PhD that honed deep skills in workload characterization and hardware profiling at IBM (2016) and Microsoft Research (2018). Additionally, I contributed in the nascent stages of MLPerf, a benchmarking effort to standardize

and democratize expectations and conditions for measuring and reporting machine learning performance, in the form of discussions for benchmark selection and responsibilities in benchmark and dataset testing and validation <sup>159</sup>.

Through my development and study of various machine learning algorithms, and particularly in managing the training and optimization of different DNNs, the resilience of DNN parameters and execution to various forms of normalization and value manipulation inspired the development of Ares, an application-level framework for quantifying the resilience of DNNs<sup>193</sup>. Ares proved extensible and expressive for a variety of application and fault-mode pairings, and I collaborated and advised projects leveraging Ares to study resilience of different number representations and data formats <sup>191</sup>, sensitivity to hyperparameters and bit-flip errors during training <sup>191</sup> and DNN resilience to approximate multiplication techniques <sup>186</sup>. Crucially, I also spent time early in my PhD understanding and developing fault models for multi-level-cell (MLC) programmed embedded non-volatile memory technologies. Specific programming choices (e.g., number and spacing of programmed values into a memory cell) could be customized according to the number formats and encoding strategies I was already studying deeply to optimize DNN weight storage <sup>60</sup>, and Ares was once again leveraged and extended to represent and quantify application-level impacts of different DNN parameter storage schemes.

After observing that cross-computing-stack interdependent design factors and sensitivities to cell-level settings were clear determinants of potential memory solution efficiency <sup>60</sup>, it became clear that a system-level evaluation and more comprehensive design study could unlock the huge potential of MLC eNVMs, which led to the MaxNVM project <sup>183</sup>. The building blocks of MaxNVM, in turn, were sufficiently modular and robust, and I applied similar co-design strategies to exciting new application spaces and system contexts (e.g., multi-task DNN inference <sup>59</sup>, graph processing kernels <sup>204</sup>, hybrid SRAM-eNVM memory systems, and natural language processing <sup>226</sup>).

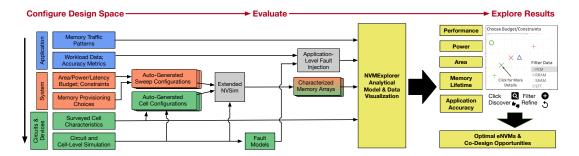

I continually developed and applied these building blocks, including a memory-fault-centric im-

plementation of the PyTorch Ares interface, in new contexts, revealing open research questions and complex design considerations along the way. I realized that the versatility and efficacy of a first-order design guidance tool could be an invaluable framework for a broader set of design studies. This realization spurred the formalization and development of NVMExplorer <sup>185</sup>. My background and experiences in data visualization platforms, including a web-based tool for visualizing microarchitectural performance counters <sup>184</sup>, made it clear that the wide adoption and accessibility of such a design space exploration framework would be boosted by providing the users from different backgrounds and expertise with comprehensive and interactive ways to explore, filter, and refine their memory system design solutions. The resulting framework, NVMExplorer, in turn quickly and effectively spurred additional collaborative efforts in optimizing device and circuit design choices towards application-level and system-level constraints and goals <sup>204,226</sup>.

#### O.1 THESIS CONTRIBUTIONS

Several key themes and takeaways for the broader discipline of memory systems architecture and computer architecture will emerge and recur throughout the discussion of my PhD work:

- Reliability: Careful consideration of hardware reliability must be a first-order design consideration in future memory systems, owing both to the unique properties of emerging technology solutions and application-level definitions of program accuracy and resilience.

- Designing towards heterogeneity: Specialized hardware components communicating and coordinating to form a single, efficient system presents unique challenges and opportunities to the computer architect and system designer.

- Flexibility: In customizing a memory architecture towards emerging technologies, system requirements, and application properties, the extreme efficiency made possible by specializa-

tion must be balanced by a sense of sufficient flexibility and generality to support application changes and broader use-cases.

- Technology-aware principles and design methodologies: Numerous emerging technology

solutions hold promise for improving the efficiency of computing systems at every scale,

particularly in the context of memory solutions, but integrating them effectively will require

exposing and balancing their properties with creativity and collaboration.

- First-order design space exploration to inform and shape further study: Probing design considerations and quantifying their impacts at many layers of the computing stack is an intensive, complex task, demanding tools and methods to effectively and efficiently explore such trade-offs at a high level to guide further investigation or investment.

Through the course of my PhD, I've unearthed and evaluated a selection of promising architecture solutions garnering appreciable potential benefits and takeaways compared with competitive baseline systems, a few examples of which include:

- Fault-prone, highly dense emerging memory technologies can be effectively employed to store sparse-encoded deep neural network weights for image classification. However, there is a tension between the two: sparse encoding increases fault vulnerability, limiting the efficacy of a fault-prone dense memory. Employing a proposed, lightweight error mitigation scheme with faulty, dense memory and sparse encoding can provide higher storage density than any of the techniques in isolation, providing up to 29× memory area reduction compared to less-faulty memory solutions <sup>183</sup> (Chapter 2.3).

- Work presented in this thesis also probes the viability of a specific, even-less-mature memory technology solution in multiple application contexts (image classification, natural language processing, social network graph search) and identifies device- and circuit-level opportunities

for innovation and co-design for efficient future memory systems  $^{204}$ . For example, memory area can be reduced by over  $12 \times$  and energy-per-memory-access by  $2.6 \times$  relative to a competitive baseline without degrading accuracy for a natural language processing task as a result of customizing memory device properties and programming schemes (Chapter 2.4).

- A proposed and evaluated new memory system for NVDLA<sup>212</sup>, an industry-grade convolutional neural network (CNN) accelerator, used co-designed emerging memory technologies to unlock up to 3.5× lower energy per image classification task and 3.2× lower system power, enabling entirely on-chip ResNet50 inference in about 2mm<sup>2</sup> of total system area <sup>183</sup> (Chapter 3.1).

- System-level performance and energy efficiency of embedded, multi-task image processing improves dramatically by integrating a hybrid memory system of both emerging and traditional memory technologies, again made possible by tuning application optimizations and system settings for compression and data format <sup>59</sup>. For example, energy per input image frame reduces by over 10× while reducing the memory area by about 3× (Chapter 3.2).

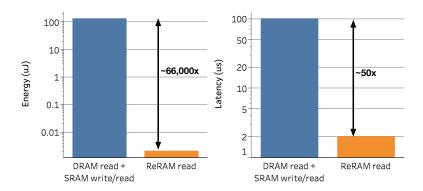

- Applying fault-prone, dense memory technologies towards other applications, such as natural language processing, similarly achieves significant efficiency benefits (e.g., reducing energy-per-input-sentence due to memory access by 66, 000×)<sup>226</sup>, while showing that the intuitions and infrastructure developed in this thesis and used to evaluate emerging technologies can be effectively generalized and empower efficient future studies (Chapter 3.3).

These evaluations are made possible by a selection of software tools, simulation frameworks, and benchmarking efforts I've built or contributed to over the course of my PhD, which are described and cited throughout this thesis. Many of these contributions and evaluation efforts culminated in the development of NVMExplorer <sup>185</sup>, a unified platform to explore the viability of emerging

memory technologies in specific application and system settings. The NVMExplorer approach reveals cross-stack dependencies and optimization opportunities, in addition to reproducing and expanding previous published studies, (e.g., <sup>183</sup>, <sup>84</sup>, <sup>204</sup>). NVMExplorer similarly enables co-design studies of application properties, system constraints, and devices in order to bridge the gap between architects and device designers for future memory solutions. Example co-design studies in Chapter 4 reveal both opportunities and potential disconnects among current research efforts <sup>185</sup>.

#### 0.2 THESIS ORGANIZATION

In Chapter 1, I present background on the fundamental costs and limitations of current on-chip memory solutions, as well as introducing the properties and potential of a selection of eNVMs that can be considered to address memory limitations in a variety of computing systems. Next, Chapter 2 introduces reliability as a key design consideration for the next generation of memory systems, describing the tools and modeling efforts I have contributed to throughout my PhD to quantify memory reliability in application-specific contexts and presenting results from several publications that highlight interdependent choices in data format, number representation, circuit- and device-level design choices, and algorithmic optimizations. Each of the studies in Sections 2.2-2.4 apply application-aware reliability analysis to improve memory system efficiency.

Chapter 3 deepens the findings of Chapter 2 by carefully co-designing specific system solutions for deep neural network inference across different application domains, optimization goals, and operating conditions. Together with Chapter 4, Chapter 3 details system evaluations that reveal significant energy/power benefits and increased storage density via comprehensive and technology-aware cross-computing-stack co-design. Chapter 4 goes above and beyond the evaluation of specific solutions by proposing and describing an open-source, modular design space exploration framework (NVMExplorer) to empower future collaborations and effective memory systems research

where application experts and device designers can similarly identify and contextualize different optimizations and system, algorithm, and technology choices. Chapter 5 revisits several key themes and takeaways, and proposes potential future contributions and research directions informed and enabled by the work presented in this dissertation.

1

# Background: Memory Technologies & How to Leverage Them

EFFICIENCY AND INNOVATION in future computer systems is increasingly bound by the capabilities of the memory system. The convergence of fundamental scaling limitations, increasing hardware specialization and system heterogeneity, and a broad set of essential computing applications

that are voraciously data-intensive prompt consideration and investment in new memory design strategies and technologies. In this chapter, I motivate the need for fundamental breakthroughs and fresh approaches in improving memory systems, as well as introduce several compelling research directions for addressing the memory needs of modern and future computing systems.

#### 1.0 Motivation: Limitations of Today's Memory Systems

Even before Moore's Law waned and ended, the slowing of scaling trends has been disproportionate in favoring the efficiency of compute vs. memory <sup>249</sup>. Namely, the improvement in microprocessor speed was observed to exceed the improvement in DRAM memory speed year-over-year. In blunt terms, the inevitable conclusion of this trend is that the fastest, most efficient possible processing unit will result in no system-level performance benefit because it will be stalled, waiting on interactions with memory. The disproportionate scaling in terms of achievable power efficiency, data delivery, and cost-effective density is sometimes referred to as the 'memory wall' problem, and it motivates much need for reinvention and careful consideration of memory system design choices.

The memory subsystem has remained a crucial performance bottleneck in the intervening years of innovation in computing at different scales (e.g., the emerging prominence and diversity of mobile phones and embedded technology, as well as datacenter-scale computing), with critical applications facing limits in terms of both the availability and utilization of memory bandwidth. The quantity of data required by applications often out-paces the power, energy, and physical distance to store sufficient data capacity. As such, there are broad classes of applications that can be identified by whether their end-to-end performance is limited by the availability and utilization of compute resources (compute-bound) versus those limited by the availability and utilization of memory resources (memory-bound). The identification of compute-bound vs. memory-bound application behavior on a given system is sometimes visualized via the Roofline Model <sup>90</sup>, and analysis is typi-

cally conducted via microarchitectural performance analysis (described in Chapter 4.0.5).

In response to the explosive number and variety of data-intensive, often memory-bound applications that are critical in computing today (from facial recognition and image processing on mobile phones, to recommendation systems and graph processing in the datacenter, to a variety of scientific computing applications), this thesis focuses on innovating and intervening in the design of memory systems, with a particular eye towards heterogeneity in two senses: (1) the integration of technological heterogeneity on-chip, that is, emerging and alternative memory device technologies, and (2) customizing memory systems towards hardware accelerators and heterogeneous systems. To understand these trends further and to motivate the solutions and methods put forth in Chapters 2-4, I next provide some discussion and key terms in memory architecture and organization, then dive into the strengths and limitations of today's most pervasive memory technologies (SRAM and DRAM). Then, I describe the area, latency, and energy costs of memory access with a simple example and identify cell-level and memory architecture design trade-offs that will recur in later design studies. Finally, this section will touch upon some compelling research and industry efforts to address the memory wall that are outside the scope of this thesis.

#### 1.0.0 SRAM, DRAM, AND THEIR LIMITATIONS

Different memory technologies find use in different parts of a traditional memory hierarchy due to their varying characteristics and varying system requirements. What are the most common memory technologies used in computing systems today, and how are they typically employed in memory hierarchies? Answering these two questions will motivate and inform what the research goals are for augmenting, replacing, or improving these technologies in future designs.

In Figure 1.0, different memory technologies and key terms are organized by their typical relative capacity and proximity to compute units, with some relevant characteristics listed on the right going from top to bottom. In most modern computing systems, the memory resources physically closest

Figure 1.0: A majority of modern computing systems rely on SRAM for fast on-chip memory resources physically close to compute resources (green), rely on additional off-chip (red) memory resources with increased density (e.g., DRAM) during computation, and also incorporate higher-capacity, non-volatile memory sources for permanent storage, as described in Section 1.0.0.

to compute resources is implemented using SRAM, and is integrated directly on the same chip as compute resources for fast, efficient data access (shown in green in Figure 1.0). Higher-capacity memory resources are accessed via an interface to another fabricated component (e.g., a DRAM chip or Flash memory), referred to throughout this thesis as "off-chip" (shown in pink/red in Figure 1.0). SRAM and DRAM are volatile technologies, meaning they must constantly receive power to retain stored data values, while Flash is a non-volatile memory technology, meaning it retains data values in memory when powered off. While the relative capacities and protocols applied to each memory technology may vary depending on system context, the broad organization of on-chip SRAM resources for performant memory, off-chip DRAM for density, and a more physically distant, slower, non-volatile resource for permanent storage is visible in mobile phones, laptops, and datacenters alike.

SRAM provides reliable, fast on-chip memory, used as cache memory in a vast majority of mod-

ern systems of varying scales. However, one can only provision so much SRAM on-chip, and there are power and efficiency trade-offs when doing so. When data needs outstrip the capacity of on-chip memory, higher-capacity, off-chip resources repopulate the on-chip resources with the more frequently used or otherwise critical data for use by compute resources. An enormous amount of microarchitectural design effort and system-level innovation is poured into retaining, rejecting, or fetching the right data from off-chip at the right time in order to minimize data movement and/or maximize overall system efficiency due to the costs (energy, time or otherwise) associated with off-chip access. This is true both historically, in continued development of cache protocols for general-purpose systems at varying scales, and in specialized hardware, where energy and power due to data movement remains a key limitation to system efficiency.

The memory wall has already forced system designers to think beyond the memory technology hierarchy in Figure 1.0, and current and future generations of computing systems will require different tools, methods, and technologies to make meaningful breakthroughs. To achieve fundamental future improvements, particularly for applications that are heavily memory-bound and for specialized systems with unique data needs, system designers must bring denser, more efficient memory resources closer to compute resources.

#### 1.0.1 MEMORY ORGANIZATION AND MEMORY ARRAY ARCHITECTURE

This section summarizes some fundamental costs of storing and retrieving data. With SRAM properties and limitations as context, we can zoom in on an example of the costs associated with data storage and data movement in a memory array architecture. What are the area, energy, and latency trade-offs when memory devices are organized into subarrays, banks, and arrays? This discussion will introduce architectural design choices and trade-offs that are unique to each proposed physical mechanism for storing bits. As alternative memory technologies for on-chip storage solutions are introduced and evaluated in future chapters, some array architecture characteristics introduced here

**Figure 1.1:** A memory array is comprised of a set of banks (left), each of which in turn may exhibit a hierarchical organization into mats and sub-arrays. Within each sub-array, there is additional periphery circuitry to read and write data in and out of a set of memory cells (right), adapted from <sup>60,62</sup>.

will be revisited and innovated in the context of optimizations that consider memory-device-level attributes, all the way up to practical, application-level impacts.

There are a variety of architectural choices when organizing memory cells and sub-arrays into larger blocks of accessible memory, some of which are evident in observing a basic memory array organization in Figure 1.1. An array of individual memory devices with corresponding circuitry to read and write data values is labeled as a sub-array, and those sub-arrays are, in turn, hierarchically organized into mats and banks. Large cell arrays can consume significantly more power and take more time to read/write to, so provisioning a block of memory using many smaller sub-arrays with a network of multiplexing and routing to determine when and how to fetch data can reduce the average energy and latency per access. Hierarchical organization choices can also enable simultaneous parallel access to multiple columns of data, sub-arrays, mats, or banks, improving the bandwidth of the overall memory. Sub-array dimensions, column muxing and complexity of selection circuitry, and hierarchical organization into mats and banks are just a sampling of design choices that impact the area efficiency, latency, and energy of access to the memory array. These trade-offs will vary per-technology, and can be tuned according to the system setting and use case. Figure 1.1 shows a schematic example of the memory organization considered by a previously-validated memory array simulation tool 62, applicable both in the context of an SRAM array and for embedded, non-volatile

**Figure 1.2:** For a small (8KB) SRAM array under two different organization choices (simulated using NVSim <sup>62</sup>), different memory organization choices impact the area efficiency, latency, and energy of access. Organizing the 8KB array as a single bank (Area-optimal) requires less area, while using 16 smaller sub-arrays (the read-energy-delay-product-optimal (ReadEDP) choice) drastically reduces energy and latency of access at the cost of additional periphery circuitry and routing from sub-array to port. The energy and latency per access can be further broken down into the contributions from individual architecture components, as labeled in Figure 1.1.

#### memory technologies (eNVMs).

Figure 1.2 presents a simple example of how the components of a memory array contribute to the access energy and latency for a simple example under two different architectural organizations. An area-optimal array organization uses a single bank; the resulting read latency and energy-per-access are then dominated by the subarray components. In constrast, a read-energy-delay-product-optimal organization will drastically reduce the latency and energy of access by fracturing the array into multiple banks and subarrays. As a result, the area slightly increases due to duplicated sensing circuitry and network overhead to route data from subarray to port, and non-subarray energy and latency comprises a larger portion of total access costs. Thus, memory architecture choices and optimization goals heavily determine the performance and efficiency of memory resources, and application performance and efficiency, in turn, can be sharply impacted by these choices. The precise trade-offs and optimal memory architectures will vary significantly depending on array capacity and optimization goals. These design considerations are made even more complex by how periphery overheads and cell characteristics differ for alternative, emerging memory technologies discussed in Section 1.2.

#### 1.0.2 3-D Integrated Memory Solutions

Another key innovation that has been deployed in several contexts is using the third dimension (e.g., stacking chips on top of one another and connecting them vertically) to improve the effective density and potential bandwidth of memory systems. This is a well-established technique in the context of stacked DRAM using through-silicon-vias (e.g., Hybrid Memory Cube<sup>75</sup>) or the proliferation of High-Bandwidth-Memory (HBM) for increased bandwidth in GPU systems (graphics processing units, e.g., <sup>158</sup>). The radical increase in effective density and bandwidth provided by 3D-stacked memory solutions has also been applied towards specialized systems for deep neural networks (e.g., <sup>73</sup>). However, these performant, high-density solutions remain power-intensive, suffer efficiency limitations, and many, being DRAM-based, are volatile memory solutions.

3D-integration techniques have also been demonstrated as compatible with several of the technologies presented in Section 1.2<sup>247,41</sup>. Though the studies presented in this thesis do not consider 3D-integrated memory solutions, typically due to the energy and power constraints of edge and embedded computing contexts considered, there are many compelling memory system design directions left for future work described in Chapter 5.

#### 1.0.3 Processing-In-Memory, Processing-Near-Memory Architectures

For several of the technologies leveraged in this thesis, their analog device properties allow them to be used effectively as processing elements <sup>222,50,105,89</sup>, as discussed in Section 1.2. For example, researchers have crafted circuit and array architectures to add or multiple input currents as values, and applied such systems towards neural network inference and training <sup>42,8,201</sup>. Additionally, there is a long history of investigation towards near-data processing (i.e., co-locating compute resources or performing computation in a memory process like DRAM to bridge the distance and unlock efficiency for data-intensive tasks <sup>140</sup>). While these approaches are exciting disruptions of the traditional

memory hierarchy (e.g., Figure 1.0) and have seen application in some targeted settings, they are accompanied by distinct manufacturing and scaling challenges.

Processing-in-memory and near-memory will remain important and exciting paradigms in the future, but the challenges to their scalability, capacity, and density are somewhat orthogonal to the study of emerging materials innovations and devices as memory cells. Though understanding and methodologies for design space exploration at the device and circuit level of emerging memory devices, such as are presented in the following chapters, could be incredibly informative towards in-/near-memory architectures in the future, specific evaluations fall outside the scope of the work presented in this thesis. As the next section will highlight, the size and data-intensiveness of mission-critical applications necessitates sheer density and energy efficiency of on-chip memory and data delivery more broadly. Thus, the scope of this thesis aims to be creative in augmenting and improving memory systems, while keeping them distinct from compute elements, to best complement the enormous diversity of modern heterogeneous computing systems.

#### I.I MOTIVATION: DATA-INTENSIVE APPLICATIONS

In response to the end of Moore's Law, architects and system designers have gravitated towards specialized hardware solutions and increasingly heterogeneous computing systems in order to achieve the next generation of performance and power advantages over previous systems. The past decade has seen an explosion of investment and interest in specialized hardware and heterogeneous computing platforms. As this trend continues, customized memory system support will continue to be essential. In this Section, I will begin by briefly reviewing examples of heterogeneous systems and the importance of hardware accelerators (Section 1.1.0). Next, I describe the specific needs and ongoing architectural innovations around two broad classes of data-intensive workloads that are the target of studies presented in this dissertation: Deep Neural Networks (DNNs, Section 1.1.1) and

the processing and analytics performed on very large graphs (Section 1.1.2).

#### 1.1.0 HARDWARE ACCELERATORS, HETEROGENEOUS SYSTEMS

Specialization allows for significant gains in compute efficiency. Identifying applications that will benefit from specialization and whose acceleration will provide benefits to the overall system setting has become a touchstone of computer architecture research and future system efficiency. For example, datacenter architectures now rely on a huge mix of server-class CPUs, GPUs, FP-GAs, other accelerators, and various network and memory interfaces to serve user requests, and high-performance-computing has similarly benefited from the integration of hardware accelerators <sup>87,111,114</sup>. Alternatively, resource-constrained and battery-powered devices (e.g., mobile phones, deployed sensor nodes, drones, self-driving cars) have similarly shifted towards a model of many accelerator blocks and integrated components, for example in a system-on-chip (SoC). In fact, the number of identifiable, specialized IP blocks in Apple iPhone SoCs has increased dramatically over the last decade, from fewer than 10 in the A4 to over 40 in the A11 (iPhone X), comprising a majority of on-chip area <sup>203</sup>. These blocks need to maintain and access data, as well as communicate with one another, and data transfer and data management become even more critical (e.g., <sup>155,182</sup>).

These specialization efforts at varying scales of computing power and complexity require customizing computing blocks (i.e., accelerators) and end-to-end systems to the needs and characteristics of the most pervasive or otherwise bottlenecked pieces of software that will execute on these systems. The efficiency and effectiveness of specialized hardware accelerator blocks rely on their understanding of application-level properties (i.e., which patterns of computation, memory access, and individual operations to support), as well as sufficient programmability and flexibility (i.e., if the target application changes slightly in terms of size or pattern, is the accelerator still useful?). Thus, cross-computing-stack design considerations and first-order understandings of application-level impacts of system designs become necessary tools in the face of heterogeneous system design and

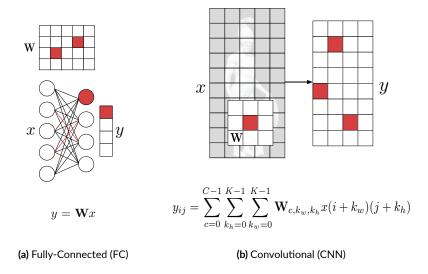

**Figure 1.3:** Two common types of neural network layers, either fully-connected (left) or convolutional (right) can be summarized as operations on an input (x) using trained parameters referred to as weights (W) to produce a transformed output (y), adapted from (y), adapted from (y), adapted from (y), and (y), and

optimization.

The rise of heterogeneous computing platforms is similarly reflected in the sheer volume of academic publications, silicon-based start-ups, and industry investment in hardware accelerators for a range of target applications (indisputably dominated by innovations and investment in machine learning) 192,159. In these myriad proposals, dense data storage, efficient data movement, and minimizing reliance on off-chip memory resources remain essential challenges. Thus, innovation and improved efficiency in on-chip memory would provide drastic improvement to systems with different target applications, different design constraints, and different scales of operation.

#### 1.1.1 DEEP NEURAL NETWORKS

Deep learning is a field of machine learning that leverages large neural networks (often referred to as Deep Neural Networks or DNNs) to tackle challenging classification and regression tasks. In recent years, DNNs have become essential to a huge breadth of application domains, including

image recognition and detection, language processing, and translation. DNNs have two operating modes: training and inference. Training is the process of fitting neural network parameters (weights) to labeled data. Inference is the process of using a previously trained DNN to predict labels for new input data. Figure 1.3 provides highlighted examples of the inputs, weights, and outputs, as well as the equations describing the basic operations of two common types of neural network layers.

Perhaps the most prominent example of the co-development of data-intensive applications and specialized hardware solution has been the seismic rise of acceleration of tensor operations in machine learning algorithms and in DNNs in particular. Machine learning researchers and engineers over the past two decades realized that the computation underlying their algorithms was often deployable and exhibited enormous performance benefits when offloaded to a graphics processing unit (GPU). Where neural-network based solutions were previously impractical due to their intensity and runtime, neural network algorithms trained using GPUs began outstripping state-of-the-art metrics in classification and prediction tasks 197,88. GPU manufacturers like NVIDIA responded in force by building out support and tailoring GPUs to the needs of such algorithms, leading to a proliferation of GPU-based machine learning acceleration. This increase in popularity, together with the continued proliferation of low-power embedded devices, has similarly motivated the design of DNN-specific hardware accelerators <sup>192,111</sup>. While many energy-efficient DNN hardware implementations have been proposed, a major challenge remains: the large memory requirement to store DNN parameters. Although entirely on-chip or on-device storage would guarantee better inference efficiency, limited on-chip SRAM capacity inevitably leads to reliance on costly off-chip memory accesses to DRAM or cloud-based execution of tasks like speech recognition.

An incredible body of work and many continued research efforts over the past decade have targeted reducing the computational complexity and memory requirements of DNNs. These techniques include innovations in data format (such as reduced precision even down to binarized DNNs), model architectures (such as reducing depth, or removing trained parameters), and training

techniques (such as transfer learning, adaptive techniques) <sup>192</sup>. However, the overarching trend of state-of-the-art proposals is a staggering increase in memory requirements to push the boundaries of machine intelligence, as well as sometimes unforeseeable changes in data flow and data access that complicate deployment to existing, fixed neural network accelerators <sup>126</sup>, <sup>226</sup>. Thus, the continued development and specialization of systems to support and accelerate DNNs and related, data-intensive applications must balance flexibility in the face of future trends with the persistent need for increased memory capacity and efficiency. Careful consideration of algorithmic advancements and memory-reducing optimizations play a key role in maximizing the effectiveness of system and architecture decisions, as explored in detail in future chapters.

The myriad proposals for reducing DNN size and complexity often degrade the achievable application-level accuracy (e.g., reducing the likelihood of correctly classifying input images by up to 10% while reducing storage requirements by an order of magnitude <sup>94</sup>). While many efforts have considered trading accuracy for efficiency in deep learning systems, the most convincing demonstration of a new technique for a practical system must address and preserve a DNN's baseline model accuracy. One proposal for quantifying and bounding acceptable variation in the inherently stochastic baseline performance of DNN's on a given task is **Iso-Training Noise (ITN)** <sup>192</sup>, which is employed in several studies presented in this dissertation (e.g., <sup>193,183</sup>). The intuition for this method is that accuracy varies for DNNs repeatedly trained with identical hyperparameters. The resulting variance in the accuracy can be used as a bound for final classification error. As long as model alterations do not result in error exceeding this bound, they are said to be indistinguishable from ITN and therefore iso-accuracy. Examples of ITN for different DNNs and application of ITN as a reasonable bound on acceptable model accuracy are found in Chapters 2.0, 2.3, 2.4, and 3.1.

#### 1.1.2 GRAPH PROCESSING

Analytics and processing tasks on very large graph structures underlie a variety of important and emerging applications today, including social network analysis, data mining, computational chemistry, and, perhaps most recently and prominently, COVID-19 drug discovery <sup>17,13,135,262</sup>. There has been a recent rash of interest and exploration of graph processing acceleration and optimization in the systems research community <sup>55,83,265,39,11,54,54,13</sup>. These works span system settings, from FPGA-based acceleration of graph kernels <sup>11</sup> to hardware accelerators <sup>54</sup> to general-purpose cache replacement policies <sup>13</sup>. Each of these works highlights and designs towards the large memory capacity and bandwidth required for efficient execution of graph processing <sup>17,83</sup>.

The challenges of customizing the memory architecture to support graph processing in a variety of system settings are similar to deep neural networks purely in that they are both data-intensive in terms of bandwidth and capacity. Otherwise, at least in broad strokes, the challenges of graph processing are quite distinct. Namely, memory access patterns exhibit much more randomness than the embarrassingly predictable patterns when operating on a fixed neural network model architecture, and graph-related kernels (e.g., search, extracting graph properties) tend to require a more balanced mix of read-write traffic than DNN use cases considered in this thesis. Additionally, the resilience of graph processing to different value manipulations and fault models is less thoroughly studied than for DNNs, as discussed and probed in Chapters 2.4 and 4.2.

#### 1.2 EMBEDDED, NON-VOLATILE MEMORY (ENVM) TECHNOLOGY LANDSCAPE

This section briefly reviews the device physics and relevant low-level details of various embeddable, non-volatile memory technologies. Each technology offers unique design challenges and opportunities as a storage device, and are at widely varying stages of development and investment across industry and academic efforts. More detailed surveys and comparisons of subsets of these technologies

are helpful resources (e.g., <sup>31</sup>) in understanding the capabilities and physical mechanisms for each eNVM proposal. The following sections will briefly describe each technology, with an emphasis on both promising and limiting characteristics of each technology. For more established technologies (i.e., RRAM, PCM, and STT), I reference compelling recent examples and mention their broad characteristics, while for more emerging solutions (i.e., FeFET, CTT), I provide some discussion of their physical design and operation. Finally, this section also discusses the eNVM landscape as a whole, including contextualizing the potential benefits and limitations of different technologies and describing multi-level-cell programming.

## 1.2.0 RESISTIVE RAM (RRAM, RERAM)

Resistive RAM (RRAM) encompasses a wide variety of cell-design implementations that all encode data via the variable resistance of a thin layer of material 92,121,190,109,79, most frequently a metal oxide 254,255,49,128,29. RRAM is particularly compelling and relatively mature among eNVM proposals, having been demonstrated by major industry fabrication facilities at relatively mature technology nodes 48,77,104. Previous and contemporary work has also employed RRAM to neural network acceleration 239,95,183, including leveraging the variable resistance readout for analog compute capabilities in neuromorphic and compute-in-memory architectures 247,235,38,261,162,215,141,42,201. Such processing-in-memory implementations for deep neural networks are part of a broader class of research probing the analog computation capabilities of RRAM cells 147,252,68,222,36,246,50,149,21.

There are compelling RRAM solutions using either diode access for crossbars or CMOS access for more traditional memory array architectures. Crossbar arrays offer the best cell area (as low as 4F<sup>2</sup>), but they are subject to higher access times than using a dedicated CMOS transistor to access the RRAM cell <sup>258,120,12,148</sup>. The larger cell area can be overcome by increasing storage density via multi-level-cell (MLC) programming <sup>209,33,251,37,189,146,269,268,53</sup>. RRAM arrays have also been demonstrated in 3D-integrated settings (e.g., 3D-stacked dies of RRAM, vertical integration of

RRAM) <sup>236,153,23,96,139,138,250</sup>. However, RRAM device and array design is still an area of active development and innovation, with constantly evolving studies of reliability and endurance <sup>171</sup>, in addition to alternative cell configurations and array architectures <sup>45,18,263,180,4,154,15,145,150,143,156,241,151</sup>.

## 1.2.1 Phase-Change Memory (PCM, PCRAM)

Phase-Change Memory (PCM), like RRAM, relies on a variable resistance in a material to encode a value. However, PCM relies on the transition between two phases of the target material, namely crystalline (low resistance) or amorphous (high resistance). PCM arrays have been the subject of study and demonstration for a longer period of time than most other eNVMs considered, and have been demonstrated in 20nm-90nm technology nodes <sup>248,47,46,10,218</sup>. PCM similarly requires careful study of reliability, endurance, and cell structure and fabrication variations <sup>40,43,152,118</sup>, and has been recently probed as compatible with 3D-integration <sup>41</sup>, processing-in-memory architectures <sup>74</sup>, and multi-level-cell-programmed implementations <sup>78,119,221,52</sup>.

# 1.2.2 FERROELECTRIC-BASED MEMORY CELLS (FERAM, FEFET)

While Ferroelectric RAM (FeRAM) is a more mature memory solution with a DRAM-like structure relying on a ferroelectric capacitor <sup>179,259</sup>, FeFET-based eNVM is an emerging, embeddable technology that achieves much higher density by modifying a FET with a layer of ferroelectric material <sup>161,58,174,166,196,175,108,231</sup>. More precisely, the FeFET device is made by replacing the normal gate dielectric in a MOSFET with a ferroelectric layer <sup>108</sup>. For this reason, FeFET devices can be easily integrated in existing CMOS processes, especially when high-*k* dielectrics such as hafnium oxide can be used as the ferroelectric layer <sup>161</sup>.

FeFET devices can be programmed to different values through partial polarization switching of the ferroelectric layer, and have been demonstrated as CMOS-compatible memory devices down to 14nm <sup>205,27,227,64,124,131,132,122,70,206</sup>. This is achieved by tuning the portions of the switched ferroelectric domains in a multi-domain FeFET, and this mechanism can be leveraged to program a single FeFET as a multi-level-cell memory device <sup>5,58</sup>, for analog compute capabilities <sup>6,223,168,107</sup>, and 3D integration <sup>69</sup>, though these are recent efforts under active research development. Recent works <sup>5,166,168,64</sup> use FeFETs for ultra-dense, low-leakage, and fast memories.

## 1.2.3 Magnetoresistive RAM (Spin-Transfer, Spin-Orbit Torque)

Two popular implementations of magnetoresistive RAM (MRAM)<sup>65,169,76</sup> rely on different physical mechanisms to encode data via the spin of electrons in a magnetic tunneling junction (MTJ) element <sup>214,142,16,110</sup>. Spin-Transfer-Torque (STT) is the more mature of the two, with compelling applications for last-level-cache <sup>170,98,7,229,177,176,106</sup>, other embedded and storage-class demonstrations <sup>133,3,173,57,113,25,51,230,32</sup>, and explorations into their applicability in near-memory-computing contexts <sup>30,105,89</sup>. By contrast, Spin-Orbit Torque (SOT) is an emerging solution with exciting potential for dense, performant storage rivaling STT characteristics and capabilities, though current implementations tend to be less dense and their scalability is not as proven <sup>172,93,71</sup>. Over the past six years, the studies in this thesis have focused on STT as a promising eNVM solution in multiple system contexts, though future work should incorporate SOT more centrally in the design space of eNVM options. STT-RAM is under active development to verify and improve reliability <sup>238,44,72,256,237,217,207</sup> and scalability <sup>164,22,240,129,61,130,134,216,211,198</sup>, as well as probing the possibility of different device and array architectures and MLC-programming via vertically stacked MTIs <sup>208,199,97,228,19,267,266</sup>.

## 1.2.4 Charge-Trap Transistors (CTT)

Previous work has shown that a single, standard-sized NMOS device can be used as a cost-effective embedded non-volatile memory cell 117,116,115,165, including multi-level-cell 157 and process-in-memory capabilities. Data is stored in the resulting memories, often referred to as charge trap transistors (CTTs), by trapping charge in the gate oxide using hot-carrier injection, which alters the threshold voltage of the device. Charge trapping impacting the threshold voltage is itself a well-studied effect typically indicative of device aging 165.

As a result, a single transistor can be programmed to exhibit different saturation currents, which are read out and decoded as distinct stored values, as discussed in Section 1.2.6 and studied in detail in Chapter 2.1. In this way, CTT-based memory arrays can be fabricated in industrial-grade, cutting-edge standard CMOS technologies with zero added manufacturing cost. In addition to low cost, CTT has many other desirable properties: the memory arrays are analogous to programmable NOR ROM arrays and have similar-scale read latency; devices display very low leakage currents, as stored information is preserved in the transistor's threshold voltage with high retention independent of the applied voltage; and as each cell consists of only a single NMOS transistor, density can be extremely high.

The benefits of CTTs come at the expense of two undesirable properties, limiting their deployment and rendering them ineffective for many general-purpose compute tasks: (1) extremely long write-latencies and (2) potential for high cell fault rates. Writes involve changing the physical device properties, which takes 100ms or more. Write latency is long because CTTs are programmed by iteratively injecting increments of charge and reading until a desired shift is achieved. This is an imperfect process – charge injection is a random process that inevitably leads to a spread in current distribution, and this spread translates to increasing likelihood of misreading the stored value. Work presented in Chapters 2 and 3 demonstrate how CTT may yet be useful for on-chip MLC weight

## 1.2.5 OTHER MEMORY TECHNOLOGIES (EDRAM, ROM, ETC.)

There are additional alternative memory technologies with varying advantages and limitations. For example, the storage requirements for the DNN architecture for deeply embedded inference, where weights need not be re-written, could be met by read-only memories (ROM) as well. ROMs ensure the best density for storing read-only parameters. However, ROMs also require configuring the network at fabrication time, which makes the design less scalable and cost-effective. One-time programmable (OTP) memories such as anti-fuse, while being amenable to post-fabrication configuration, are far less dense than other memory solutions, even when compared to SRAM.

Embedded DRAM (eDRAM) is another compelling response to the need for dense and performant on-chip memory, and over the past 10-15 years eDRAM has seen deployment in industry products (e.g., the XBox 360°) and, more recently, in accelerator systems for data-intensive applications 35,83. While eDRAM continues to be developed, optimized, and deployed, issues of technology scaling persist, and the complexity and power-intensiveness of DRAM refresh preclude its use in energy-constrained devices and environments. In contrast, embedded non-volatile memories typically have extremely low leakage and can be powered off without losing data, while still offering increased density, adequate performance, and CMOS-compatibility. In fact, several of the eNVMs discussed require few to no CMOS process changes compared with the complexity and potential fabrication issues of embedding DRAM.

It is also possible to embed traditional flash memory (eFlash), which is provided as a production-grade on-chip memory solution by top industry foundries (e.g., for IoT settings from TSMC <sup>232</sup>) despite known issues and large overheads due to reliability of eFlash technology <sup>210,253</sup>. eFlash has been deployed as a compelling solution for increased on-chip density in IoT and automotive applications, but has several key limitations to wider adoption and future development <sup>144</sup>. Most promi-

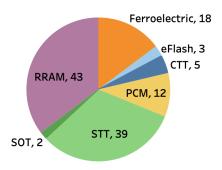

**Figure 1.4:** Number of ISSCC, VLSI, and IEDM papers published per eNVM technology, 2016-2020, showing sustained interest in RRAM, STT, and emerging interest in ferroelectric-based devices, taken from <sup>185</sup>.

nently, eFlash has not proved compatible with advanced technology nodes, and it exhibits markedly higher power consumption and typically worse read/write performance than RRAM, MRAM, and other eNVMs considered in this work.

## 1.2.6 MULTI-LEVEL NVM STORAGE

Storing multiple bits in a single memory cell (multi-level-cell, MLC) is desirable for increasing storage density, and has been demonstrated using many eNVM devices, including resistive random access memories (ReRAM), phase change memories (PCMs), charge-trap transistors (CTT), and FeFETs<sup>31,115,183</sup>. In order to discriminate among the different programmed levels, the memory sensing circuit needs to perform an analog to digital conversion (ADC), decoding each detected level of current or resistance from the memory cell to the corresponding binary word <sup>53</sup>. However, the relatively high area and power overhead of the ADC can limit the relative benefits of MLC implementations compared to single-level-cell (SLC) storage. Thus, MLC NVM storage, while offering exciting opportunities for increased density, introduces performance/power/area trade-offs and may be accompanied by reliability issues, as studied in detail for several technologies in Chapter 2.

#### 1.2.7 DISCUSSION: OPPORTUNITIES AND LIMITATIONS

In evaluating the varied landscape of non-volatile memory devices, we are interested in identifying implementations that achieve low read latency, high storage density, and proven ability to scale to advanced process nodes. Figure 1.4 summarizes the number of publications pertaining to each flavor of eNVM over 5 years of the top device and circuit conference venues, including both academic and industry demonstrations and manufactured examples. There is clear variety and active research in the design, optimization, and application of eNVM solutions, but there is a severe imbalance of available data and detail across these technologies according to device maturity, corporate transparency, and the potentially limited scope of demonstration in each published example.

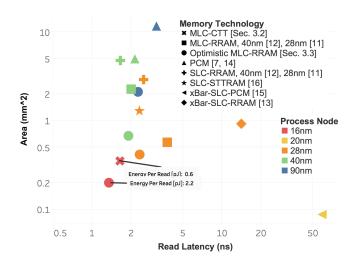

For a sampling of memory-array-level capabilities of eNVMs, Table 1.0 shows several published and validated examples, spanning different technology nodes (90nm to 20nm) and architectures (crossbar vs. CMOS-access), taken from 183. Several RRAM solutions have been demonstrated in relatively advanced technology nodes, and CMOS-access architectures for embedded applications indicate compelling storage density and read characteristics (i.e., lower area and comparable read latency compared to iso-capacity SRAM). STT strictly improves storage density and read/write performance compared to RRAM and PCM owing to demonstration in a more advanced technology node (28nm) and higher area efficiency despite larger cell footprint. The advantages of PCM are less uniform; though 40nm PCM appears to exhibit lower write latency than similar-capacity RRAM examples, the publication lacks sufficient data to contextualize this with the achievable density and read characteristics. This incomplete context and inconclusive comparison at the device or array level is representative of a key research challenge in trying to identify and evaluate the most relevant and most compelling memory solutions for a particular use case.

To better contextualize and more precisely evaluate the trade-offs among eNVM proposals, Figure 1.5 shows simulated, iso-capacity 4MB memory array characteristics derived from pub-

| Reference | eNVM type | Tech. Node | Access | Cell Area         | Capacity | Array Area            | Read latency | Write latency         |

|-----------|-----------|------------|--------|-------------------|----------|-----------------------|--------------|-----------------------|

| 29        | RRAM      | 28nm       | CMOS   | 39 F <sup>2</sup> | ıМb      | 0.56 mm <sup>2</sup>  | 6.8ns        | 500ns - 100 <i>µs</i> |

| 128       | RRAM      | 40nm       | CMOS   | 53 F <sup>2</sup> | 1.4Mb    | 0.28 mm <sup>2</sup>  | ions         | _                     |

| 2.3       | RRAM      | 24nm       | diode  | 4 F <sup>2</sup>  | 32Gb     | 130.7 mm <sup>2</sup> | 40µs         | 230µs                 |

| 52        | MLC PCM   | 90nm       | CMOS   | 25 F <sup>2</sup> | 256Mb    | 120 mm <sup>2</sup>   | 320ns        | _                     |

| 47        | PCM       | 40nm       | CMOS   | _                 | ıМb      | _                     | _            | 12ons                 |

| 46        | PCM       | 20nm PRAM  | diode  | 4 F <sup>2</sup>  | 8Gb      | 59.4 mm <sup>2</sup>  | 1 20ns       | 150ns - 100 <i>µs</i> |