# Atomic Layer Deposited Zinc Tin Oxide Channel for Amorphous Oxide Thin Film Transistors

#### Citation

Heo, Jaeyeong, Sang Bok Kim, and Roy G. Gordon. 2012. Atomic layer deposited zinc tin oxide channel for amorphous oxide thin film transistors. Applied Physics Letters 101(11): 113507.

#### **Published Version**

doi:10.1063/1.4752727

#### Permanent link

http://nrs.harvard.edu/urn-3:HUL.InstRepos:9961225

### Terms of Use

This article was downloaded from Harvard University's DASH repository, and is made available under the terms and conditions applicable to Open Access Policy Articles, as set forth at http://nrs.harvard.edu/urn-3:HUL.InstRepos:dash.current.terms-of-use#OAP

# **Share Your Story**

The Harvard community has made this article openly available. Please share how this access benefits you. <u>Submit a story</u>.

**Accessibility**

Atomic Layer Deposited Zinc Tin Oxide Channel for

Amorphous Oxide Thin Film Transistors

Jaeyeong Heo, <sup>1,2</sup> Sang Bok Kim, <sup>1</sup> and Roy G. Gordon <sup>1,a)</sup>

<sup>1</sup>Department of Chemistry and Chemical Biology, Harvard University,

Cambridge, Massachusetts 02138, USA

<sup>2</sup>Department of Materials Science and Engineering, Chonnam National University, Gwangju

500-757. Korea

Bottom-gate thin film transistors with amorphous zinc tin oxide channels were grown by atomic layer

deposition (ALD). The films maintained their amorphous character up to temperatures over 500 °C. The

highest field effect mobility was ~13 cm<sup>2</sup>/V·s with on-to-off ratios of drain current ~10<sup>9</sup>-10<sup>10</sup>. The

lowest subthreshold swing of 0.27 V/decade was observed with thermal oxide as a gate insulator. The

channel layers grown at 170 °C showed better transistor properties than those grown at 120 °C.

Channels with higher zinc to tin ratio ( $\sim$ 3-4) also performed better than ones with lower ratios ( $\sim$ 1-3).

a) Electronic mail: gordon@chemistry.harvard.edu

1

Amorphous metal oxide semiconductors have been extensively studied over the past ten years as promising channel materials for thin film transistors (TFTs) for organic light-emitting diodes (OLEDs) and liquid crystal displays (LCDs). The large demand for low power consumption with better performance of such devices requires a new semiconductor material exhibiting better transistor properties, *i.e.* higher mobility, smaller subthreshold swing (SS), higher ratio of on-to-off drain current (I<sub>ON</sub>/I<sub>OFF</sub>). The demonstration of amorphous indium gallium zinc oxide (a-IGZO) transistors by Nomura *et al.* drew huge attention to ZnO-based materials. It showed large mobility of 6-9 cm<sup>2</sup>/V·s with good stability. Their amorphous nature enables excellent stability and uniformity over large area devices unlike poly-silicon-based devices. Zinc tin oxide (ZTO) is one of the ZnO-based oxides which has been highlighted recently due to its high stability with reasonable mobility up to 15 cm<sup>2</sup>/V·s. Also, ZTO does not contain indium or gallium so it is free of toxic, expensive and scarce elements.

Generally, sputtering has been used for the growth of ZTO channel layers with its easy control on carrier concentrations by adjusting operating conditions.<sup>5-9</sup> Other growth methods, such as pulsed laser deposition<sup>10</sup>, solution deposition<sup>11</sup>, inkjet printing<sup>12</sup>, and combustion<sup>13</sup>, have been reported. However, growth of ZTO by atomic layer deposition (ALD) and detailed study of its performance in devices have remained largely unexplored up to now. Growth with exceptional controllability over the elemental composition and thickness is one of the advantages of ALD.<sup>14</sup> Uniform composition and thickness are also maintained in ALD films over rough surfaces and inside narrow holes, which conventional sputtering cannot provide easily for possible three-dimensional device structures. ALD offers the possibility of selective deposition only on some areas while avoiding deposition on other areas that are deactivated, for example, by imprint lithography.<sup>15, 16</sup> Thus films can be patterned without any etching step. This patterning process is superior to conventional etching or lift-off in that no coating material is wasted, and no toxic liquid waste (etchant or photo-resist solvent) is created. In addition, ALD is suitable for deposition on the increasingly large display panels planned for the next generation. In order to achieve these highly desirable properties for ALD of multicomponent amorphous oxides, the ALD

temperature windows of the different components must overlap. For example, diethyl zinc, the most popular zinc precursor in ZnO-ALD, exhibits an ALD window from roughly 120 to 170 °C. Therefore, an ALD process for SnO<sub>2</sub> showing an overlapping ALD temperature window should be used to realize ideal ALD of ZTO. Recently the authors have demonstrated low-temperature (60-250 °C) ALD of tin dioxide, SnO<sub>2</sub>, using a cyclic amide of Sn(II) (1,3-bis(1,1-dimethylethyl)-4,5-dimethyl-(4R,5R)-1,3,2-diazastannolidin-2-ylidene) as the tin precursor. <sup>17</sup> By combining well-established ZnO ALD with this SnO<sub>2</sub> process, fabrication of ZTO-based transistors with good properties is demonstrated in this letter.

Diethylzinc (Sigma Aldrich) and a cyclic amide of Sn(II) were used as the zinc and tin precursors, respectively. As a common oxidant, 50 wt.% hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>, Sigma Aldrich) was used. ALD-SnO<sub>2</sub> growth behavior with the Sn(II) precursor is reported elsewhere. To Instead of stop-flow ALD injection scheme, conventional constant flow scheme was employed in this study to obtain more uniform tin concentration profile along the long substrate holder (~30 cm). The observed saturation growth rate was ~1.2-1.3 Å/cycle. Although its growth rate was somewhat lower than that from stop-flow scheme, similar electrical properties were obtained. Growth temperature was mainly 170 °C, which is the upper-bound temperature for ZTO ALD. The ZTO growth was done by repeating a supercycle, x-times subcycle of ZnO (diethyl zinc/purge/H<sub>2</sub>O<sub>2</sub>/purge) followed by y-times subcycle of SnO<sub>2</sub> (Sn precursor/purge/H<sub>2</sub>O<sub>2</sub>/purge). Purge time was set to be 30s. Following notation of xZyT is used here. For example, 3Z1T means 3 subcycles of ZnO and 1 subcycle of SnO<sub>2</sub>. To study how the film composition influences transistor properties, the following zinc-rich films were prepared: 3Z1T, 2.5Z1T, 2Z1T, 1Z1T, and 1Z2T. Here, 2.5Z1T is a modified recipe (3ZnO/1SnO<sub>2</sub>/2ZnO/1SnO<sub>2</sub>), which performed the best as a channel for transistors.

Bottom-gate transistors were fabricated for the evaluation of ZTO channel layers grown on thermal oxide ( $\sim$ 120 nm)/highly-doped p-Si (0.001 ohm·cm) substrates. Channel thickness was  $\sim$ 10 nm by varying the total number of supercycles based on the observed growth rate. Channel patterning was done by conventional photolithography and reactive ion etching with Ar/CH<sub>4</sub> mixed gas. Annealing in

air was followed for one hour at 450 °C. A transistor without high-temperature annealing was not turned off at zero bias of  $V_{GS}$  and exhibited worse  $I_{ON}/I_{OFF}$  ratio of ~ $10^2$ . E-beam evaporation was used for aluminum deposition on pre-defined source and drain areas, followed by liftoff. Twenty devices with various channel widths (W, 250-1000  $\mu$ m) and lengths (L, 50-600  $\mu$ m) were made on one substrate to investigate fringing electric field/ sidewall effects. Transmission line model (TLM) patterns were also included for contract resistance measurements. The channel overlap with the source and drain was 150  $\mu$ m. After annealing at 100 °C for 20 min in hot oven to remove residual hydrocarbon and moisture, indium back contacts were made. Agilent 4156C and 41501B were used for electrical analysis of the transistors. The measurements were done at room temperature in air under dark conditions. Field effect mobility was derived with  $V_G$  at 20 V and  $V_{DS}$  at 100 mV.

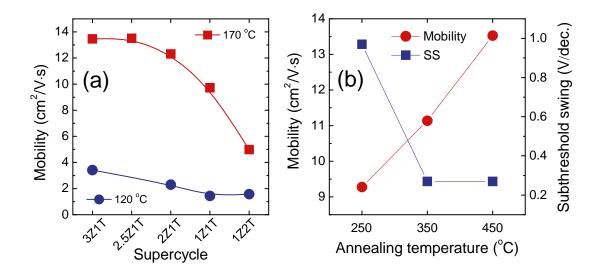

Basic film properties were studied first. Film densities and compositions of ZTOs were measured by using X-ray reflectivity (PANalytical, X'Pert Pro) and Rutherford backscattering spectroscopy (RBS). Figure 1a shows representative reflectivity spectra of ~30 nm-thick 2.5Z1T grown on thermal oxide. Film densities of ZTO layers grown at 170 °C were in the rage of 5.0-5.3 g/cm<sup>3</sup>. No obvious change in film density, thickness, and roughness was observed after the 450°C-annealing, which indicates dense and stable films were grown. Figure 1b shows a representative RBS spectrum of a 2.5Z1T layer grown on a glassy carbon substrate (Ted Pella). Zinc to tin ratios (Zn/Sn) were measured to be 4.7, 3.9, 3.3, 2.2, and 0.9 for 3Z1T, 2.5Z1T, 2Z1T, 1Z1T, and 1Z2T, respectively. No other elements except Zn, Sn, and O were detected. Optical transmission was measured by a spectrophotometer (Hitachi, U-4100). The average transmittance for wavelengths from 400 to 700 nm was measured for 2.5Z1T films with thicknesses of 10, 30 and 50 nm to be about 98, 90, and 82 %, respectively, compared to an uncoated quartz reference.

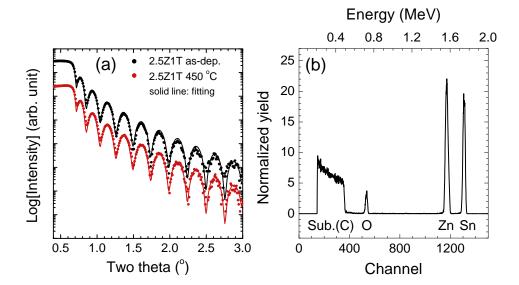

The change in microstructure of ~30 nm-thick ZTOs grown on thermal oxide as a function of annealing temperature in air was studied by using glancing-angle X-ray diffraction (incidence angle: 0.4°). Figure 2a shows representative spectra of 2.5Z1T. Broad peaks at around 34° are observed for as-

deposited and annealed films up to 650 °C, which is characteristic of amorphous ZTO.<sup>5, 23</sup> Crystallization occurred at 750 °C and the observed spectrum matched with cubic spinel Zn<sub>2</sub>SnO<sub>4</sub>.<sup>23</sup> When the surface morphology of ZTO films was examined by atomic force microscopy (AFM, Asylum, MFP-3D), phase separation was observed at an annealing temperature lower than the crystallization temperature. As shown in the inset of Fig. 2b, particles (size: 200-500 nm, height: 60-80 nm, distance: 1-4 μm) were detected on the film surface. The phase separation temperature was dependent on Zn/Sn ratio as summarized in Fig. 2b. The temperature for phase separation increased with tin content. The sample with highest tin content, 1Z1T, did not show any sign of phase separation up to its crystallization temperature of 650 °C, which may be due to its having stoichiometry (Zn/Sn: 2.2) close to that of the Zn<sub>2</sub>SnO<sub>4</sub> phase. Higher Zn concentration of this particle was revealed by energy dispersive X-ray spectroscopy (EDX), as shown in the elemental line profile of Fig. 2c. Raman analysis confirmed that Zn-O bonding is the dominant chemical nature of the particle (data not shown). Annealing for transistor fabrication was limited to 450 °C based on these analyses.

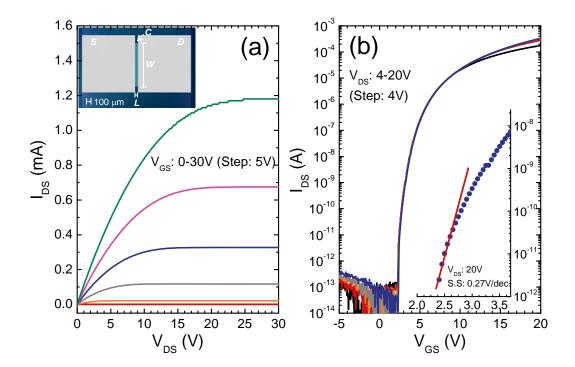

Figure 3 shows the representative output ( $I_{DS}$ - $V_{DS}$ ) and transfer ( $log(I_{DS})$ - $V_{GS}$ ) curves for 10 nm-thick 2.5Z1T channel (L: 70  $\mu$ m, W: 1000  $\mu$ m). Inset of Fig. 3a is an optical microscope image of the fabricated device. Hard saturation is clearly seen from the output curve, which suggests that the device behaves similarly to the conventional metal-oxide-semiconductor field effect transistor.<sup>5, 24</sup> The shape of the curve near  $V_{GS}$  at 0 V is also convex, which indicates minimal current crowding at the source and drain contacts.<sup>1, 6, 12</sup> The measured specific contact resistance from the TLM pattern on this device was ~0.6 ohm·cm<sup>2</sup>. Considering its low carrier concentration of ~10<sup>15</sup>/cm<sup>3</sup> after annealing at 450 °C (based on Hall measurements and sheet resistance from TLM), this value is in line with other ZnO-based oxides with similar carrier concentrations.<sup>25, 26</sup> The transfer length was calculated to be ~24-27  $\mu$ m for the 2.5Z1T transistor.

It is noted from the transfer curve of Fig. 3b that ZTO transistor operates in enhancement mode. The  $I_{ON}/I_{OFF}$  ratio was as high as ~10<sup>9</sup>-10<sup>10</sup>, which is comparable to or better than other reports for well-

behaved transistors.<sup>9,11</sup> The  $I_{ON}/I_{OFF}$  ratio derived from the transfer curve for  $V_{DS}$  of 20 V showed clear decreasing trend with decreasing Zn/Sn ratio; it was ~ $10^9$  - $10^{10}$  for 3Z1T, 2.5Z1T, and 2Z1T and it decreased to ~ $10^7$ - $10^8$  and further to ~ $10^6$  for 1Z1T and 1Z2T, respectively. Turn-on voltage,<sup>5</sup> the gate voltage at the onset of the initial sharp increase in a transfer curve, was mainly at 0 - 3 V except 1Z2T transistor, which was largely negative-shifted (-9 V). The SS value was as low as 0.27 V/decade for 2.5Z1T channel as shown in inset of Fig. 3b and this value is comparable or better than other reports for ZTO transistors<sup>8, 9, 11</sup> The minimum off-current was generally in the range of  $10^{-13}$ - $10^{-14}$  A, which is below the maximum level of  $10^{-12}$  A for flat-panel displays.<sup>1</sup>

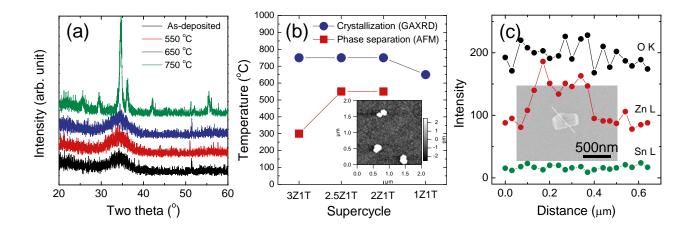

The Zn/Sn ratio clearly influenced the mobility of the transistors. The highest field effect mobility of  $\sim 12-13 \text{ cm}^2/\text{V} \cdot \text{s}$  was obtained for 3Z1T, 2.5Z1T and 2Z1T channels as plotted in Fig. 4a. Here, the mobility was derived from the transfer curve for  $V_{DS}$  of 0.1 V. As the Zn/Sn ratio decreases, mobility drops to  $\sim 10$  and  $\sim 5 \text{ cm}^2/\text{V} \cdot \text{s}$  for 1Z1T and 1Z2T transistors, respectively. McDowell *et al.* reported similar decreasing trend of mobility with decreasing Zn/Sn ratio from  $\sim 4$  to 1 by the sputtering method.<sup>8</sup>

When ZTO layers were grown at 120 °C, which is near the lower end of the ALD window, lower mobilities of at most ~3.4 cm²/V·s were obtained. Still, a similar trend of decrease with decreasing Zn/Sn ratio was observed. The I<sub>ON</sub>/I<sub>OFF</sub> ratio decreased to ~10<sup>7</sup> in addition to increased SS for Zn/Sn ratio of ~3. Overall drastic worsening of transistor parameters was observed for 120 °C-grown 1Z2T as well. Based on these observations, it is concluded that higher Zn content leads to higher mobility when the Zn/Sn ratio is larger than 1. It should be mentioned that although phase separation occurred for 3Z1T after annealing at 450 °C, comparable transistor properties to 2.5Z1T and 2Z1T channels are obtained. It appears that the influence of phase-separated ZnO particles on transistor operation is minimal as the current flow is close to semiconductor/insulator interface. No increase of field effect mobility with decreasing W/L from 20 to 1.67 was observed, which also indicates that the effect of fringing electric fields is negligible in our ZTO transistors.<sup>21</sup>

The channel mobility was influenced by annealing temperature. The change in mobility of 2.5Z1T channel for different annealing temperatures from 250 to 450 °C is plotted in Fig. 4b. As the annealing temperature increases, higher mobility was obtained. This effect could be due to favorable rearrangement of channel materials. All three transistors exhibited similar I<sub>ON</sub>/I<sub>OFF</sub> parameters of ~10<sup>9</sup>-10<sup>10</sup>; however, SS of 250°C-annealed transistor was higher (0.97 V/decade) than that of the other two transistors (0.27 V/decade). This result suggests that fabrication of ALD-based ZTO transistors is compatible with most electronic device applications including some polymer substrates. Further improvement in the mobility of the transistors may be achieved by using a zinc precursor, such as zinc acetate (Zn(CH<sub>3</sub>COO)<sub>2</sub>), that is thermally stable at higher growth temperatures above 170 °C. <sup>27</sup>

The drive current density per unit width could be increased by depositing the transistors conformally over highly patterned substrates, such as arrays of parallel narrow trenches. Conformal ALD and CVD techniques are available to make the required insulator films, as well as conformal metal gates and contacts. This approach could boost the effective drive current by a large factor equal to the trench depth divided by the trench width.

In summary, transistors were demonstrated with amorphous zinc tin oxide as a channel layer grown by atomic layer deposition. The optimized composition was stable against phase separation and crystallization up to temperatures over 500 °C. Transistor parameters were highly dependent on film composition and both growth and annealing temperatures. The highest electron mobility and drain current on-to-off ratio of ~13 cm²/V·s and ~109-1010, respectively, were obtained for 450 °C-annealed zinc-rich zinc tin oxides. The lowest subthreshold swing was 0.27 V/decade. Even for channels with lower annealing temperature of 350 °C, mobility as high as ~11 cm²/V·s with good subthreshold swing of 0.27 V/decade was obtained. The ALD method can provide highly uniform thickness and composition scalable over large areas, even on rough or structured substrates. Patterned films can potentially be grown using simple printing of inhibitors that prevent growth on undesired areas, without the need for any etching process.

This work was performed in part at the Center for Nanoscale Systems (CNS) at Harvard University, a member of the National Nanotechnology Infrastructure Network (NNIN), which is supported by the National Science Foundation under NSF award no. ECS-0335765. J. Heo acknowledges Dr. Jeong Hwan Kim (Forschungszentrum Jülich) for his fruitful advice and Dr. Jiangdong Deng (CNS) for his help on Raman analysis.

## References

- 1. T. Kamiya, K. Nomura and H. Hosono, Sci. Technol. Adv. Mater. **11** (4), 044305 (2010).

- 2. J. K. Jeong, Semicond. Sci. Technol. **26** (3), 034008 (2011).

- 3. J. S. Park, W.-J. Maeng, H.-S. Kim and J.-S. Park, Thin Solid Films **520** (6), 1679-1693 (2012).

- 4. K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano and H. Hosono, Nature **432** (7016), 488-492 (2004).

- 5. H. Q. Chiang, J. F. Wager, R. L. Hoffman, J. Jeong and D. A. Keszler, Appl. Phys. Lett. **86** (1), 013503 (2005).

- 6. W. B. Jackson, R. L. Hoffman and G. S. Herman, Appl. Phys. Lett. **87** (19), 193503 (2005).

- 7. R. L. Hoffman, Solid-State Electron. **50** (5), 784-787 (2006).

- 8. M. G. McDowell, R. J. Sanderson and I. G. Hill, Appl. Phys. Lett. **92** (1), 013502 (2008).

- B. S. Yang, S. Park, S. Oh, Y. J. Kim, J. K. Jeong, C. S. Hwang and H. J. Kim, J. Mater. Chem.

22 (22), 10994-10998 (2012).

- 10. P. Görrn, M. Sander, J. Meyer, M. Kröger, E. Becker, H. H. Johannes, W. Kowalsky and T. Riedl, Adv. Mater. **18** (6), 738-741 (2006).

- 11. S.-J. Seo, C. G. Choi, Y. H. Hwang and B.-S. Bae, J. Phys. D: Appl. Phys. 42 (3), 035106 (2009).

- 12. D. Kim, Y. Jeong, K. Song, S.-K. Park, G. Cao and J. Moon, Langmuir **25** (18), 11149-11154 (2009).

- 13. M.-G. Kim, M. G. Kanatzidis, A. Facchetti and T. J. Marks, Nat. Mater. **10** (5), 382-388 (2011).

- 14. S. M. George, Chem. Rev. **110** (1), 111-131 (2010).

- 15. W. Lee and F. B. Prinz, J. Electrochem. Soc. **156** (9), G125-G128 (2009).

- 16. X. Jiang and S. F. Bent, J. Phys. Chem. C 113 (41), 17613-17625 (2009).

- 17. J. Heo, A. S. Hock and R. G. Gordon, Chem. Mater. **22** (17), 4964-4973 (2010).

- J. Heo, Y. Liu, P. Sinsermsuksakul, Z. Li, L. Sun, W. Noh and R. G. Gordon, J. Phys. Chem. C

115 (20), 10277-10283 (2011).

- 19. J. Heo, S. B. Kim and R. G. Gordon, J. Mater. Chem. **22** (11), 4599-4602 (2012).

- S. K. Karuturi, L. Liu, L. T. Su, Y. Zhao, H. J. Fan, X. Ge, S. He and A. T. I. Yoong, J. Phys. Chem. C 114 (35), 14843-14848 (2010).

- 21. E. M. C. Fortunato, P. M. C. Barquinha, A. C. M. B. G. Pimentel, A. M. F. Gonçalves, A. J. S. Marques, L. M. N. Pereira and R. F. P. Martins, Adv. Mater. 17 (5), 590-594 (2005).

- 22. S. Lee, H. Park and D. C. Paine, J Appl Phys **109** (6), 063702 (2011).

- 23. D. L. Young, H. Moutinho, Y. Yan and T. J. Coutts, J. Appl. Phys **92** (1), 310-319 (2002).

- 24. P. Haifeng, L. Guifeng, F. Jiahan, L. Baoying and Z. Qun, Semicond. Sci. Technol. 26 (9), 095004 (2011).

- 25. W. Lim, D. P. Norton, J. H. Jang, V. Craciun, S. J. Pearton and F. Ren, Appl. Phys. Lett. **92** (12), 122102 (2008).

- Y. Shimura, K. Nomura, H. Yanagi, T. Kamiya, M. Hirano and H. Hosono, Thin Solid Films

516 (17), 5899-5902 (2008).

- M. Tammenmaa, T. Koskinen, L. Hiltunen, L. Niinistö and M. Leskelä, Thin Solid Films 124

(2), 125-128 (1985).

#### **Figure Captions**

**Figure 1.** (a) Representative X-ray reflectivity spectra for as-deposited and 450°C-annealed 2.5Z1T ZTO on thermal oxide/Si substrate. Here, film thickness is ~30 nm and the growth temperature is 170 °C. No significant change was observed after the annealing. The density was ~5.3 g/cm<sup>3</sup> and RMS roughness was ~0.8 nm. (b) RBS spectrum for as-deposited 2.5Z1T on a carbon substrate. The Zn/Sn ratio was estimated to be 3.9.

**Figure 2.** (a) Glancing-angle X-ray diffraction of as-deposited and annealed 2.5Z1T ZTO films grown on thermal oxide/Si substrates (incidence angle: 0.4°). Crystallization occurred at 750 °C. (b) The crystallization (circles) and phase separation (squares) temperatures for ZTO layers with different compositions. Inset: An AFM image of a 550 °C-annealed 2.5Z1T ZTO film. No phase separation was observed for 1Z1T up to 650 °C. (c) EDX O, Zn, and Sn line profiles of the phase separated particle (inset image), which was analyzed as Zn-rich phase.

**Figure 3.** (a) Representative  $I_{DS}$ - $V_{DS}$  output characteristics of a transistor with 450 °C-annealed 2.5Z1T ZTO channel (L: 70 μm, W: 1000 μm). An optical microscope image of the fabricated transistor is shown as an inset. (b)  $Log(I_{DS})$ - $V_{GS}$  transfer curve for the transistor. Inset is the enlargement for subthreshold swing determination at  $V_{DS}$  of 20 V. Here, sweep is 50 mV step. Subthreshold swing was 0.27 V/decade.

**Figure 4.** (a) Field effect mobility for ZTO channels with various Zn/Sn ratios. Here, two different growth temperatures of 120 and 170 °C were compared. (b) Field effect mobility and subthreshold swing of transistors with 2.5Z1T channel as a function of annealing temperature.

Figure 1.

Figure 2.

Figure 3.

Figure 4.