# Inversion-mode GaAs wave-shaped field-effect transistor on GaAs (100) substrate

### Citation

Zhang, Jingyun, Xiabing Lou, Mengwei Si, Heng Wu, Jiayi Shao, Michael J. Manfra, Roy G. Gordon, and Peide D. Ye. 2015. "Inversion-Mode GaAs Wave-Shaped Field-Effect Transistor on GaAs (100) Substrate." Appl. Phys. Lett. 106 (7) (February 16): 073506. Portico. doi:10.1063/1.4913431.

## **Published Version**

doi:10.1063/1.4913431

# Permanent link

http://nrs.harvard.edu/urn-3:HUL.InstRepos:14117006

#### Terms of Use

This article was downloaded from Harvard University's DASH repository, and is made available under the terms and conditions applicable to Open Access Policy Articles, as set forth at http://nrs.harvard.edu/urn-3:HUL.InstRepos:dash.current.terms-of-use#OAP

# **Share Your Story**

The Harvard community has made this article openly available. Please share how this access benefits you. <u>Submit a story</u>.

Accessibility

# Inversion-mode GaAs Wave-Shaped Field-Effect Transistor on GaAs (100) Substrate

- Jingyun Zhang <sup>1)</sup>, Xiabing Lou <sup>2)</sup>, Mengwei Si <sup>1)</sup>, Heng Wu <sup>1)</sup>, Jiayi Shao <sup>3)</sup>, Michael J.

Manfra <sup>1) 3) 4)</sup>, Roy G. Gordon <sup>2)</sup>, and Peide D. Ye <sup>1) a)</sup>

- 1) School of Electrical and Computer Engineering and Birck Nanotechnology Center,

Purdue University, West Lafayette, IN 47907, U.S.A.

- 2) Department of Chemistry and Chemical Biology, Harvard University, Cambridge, MA

02138, U.S.A.

- 3) Department of Physics, Purdue University, West Lafayette, IN 47907, U.S.A.

- 4) School of Materials Engineering, Purdue University, West Lafayette, IN 47907, U.S.A.

Inversion-mode GaAs wave-shaped metal-oxide-semiconductor field-effect transistors (WaveFETs) are demonstrated using atomic-layer epitaxy of La<sub>2</sub>O<sub>3</sub> as gate dielectric on (111)A nano-facets formed on a GaAs (100) substrate. The wave-shaped nano-facets, which are desirable for the device on-state and off-state performance, are realized by lithographic patterning and anisotropic wet etching with optimized geometry. A well-behaved 1 μm gate length GaAs WaveFET shows a maximum drain current of 64 mA/mm, a subthreshold swing of 135 mV/dec, and an I<sub>ON</sub>/I<sub>OFF</sub> ratio of greater than 10<sup>7</sup>.

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed; electronic mail: <a href="mailto:yep@purdue.edu">yep@purdue.edu</a>

GaAs has been considered to replace Si in logic applications for decades due to its high electron mobility [1]. To achieve high on-current surface-channel inversion-mode nchannel metal-oxide-semiconductor field-effect transistors (MOSFETs) on GaAs (100) substrate is a long-time challenge. The main obstacle is the lack of high-quality, thermodynamically stable dielectric on GaAs that can match the device criteria as SiO<sub>2</sub> on Si such as a mid-gap interface trap density (D<sub>it</sub>) around 10<sup>10</sup> cm<sup>-2</sup> eV<sup>-1</sup>. During the past decades, tremendous efforts have been made to improve the oxide/GaAs interface with most of focus on different types of oxides and formation methods [2-10]. Recent work finds that the oxide/GaAs interface quality is strongly dependent on semiconductor surface orientations. GaAs MOSFETs fabricated on (111)A surface exhibit much higher on-state current (I<sub>ON</sub>) than other surface-orientations such as (100) and (111)B even with the same atomic-layer-deposited (ALD) oxide [11]. More interestingly, much larger I<sub>ON</sub> can be achieved on GaAs (111)A substrate with single crystalline La-based oxide dielectrics by atomic-layer-epitaxy (ALE) [12]. Mid-gap D<sub>it</sub> or Fermi-level-pinning problem is significantly reduced with epitaxial La<sub>2</sub>O<sub>3</sub> on GaAs (111)A surface [13,14], because the number of dangling bonds are dramatically reduced due to the nature of epitaxial oxide/semiconductor interface. However, GaAs (111)A substrate is technologically less important than the widely available GaAs (100) substrate, in particular, for the development of a manufacturable device technology.

In this letter, we demonstrate GaAs wave-shaped MOSFETs (WaveFETs) on a GaAs (100) substrate by nano-engineering to form ALE La<sub>2</sub>O<sub>3</sub> on (111)A nano-facets. GaAs (111)A surface is achieved on a GaAs (100) substrate by the development of an

well-controlled anisotropic wet etching process. GaAs MOSFETs are formed on wave-shaped (111)A surface channels with epitaxial La<sub>2</sub>O<sub>3</sub> as dielectric. But all devices are fabricated on GaAs (100) substrates. These devices have on-state current (I<sub>ON</sub>) of 64 mA/mm and transconductance (g<sub>m</sub>) of 32 mS/mm with sub-threshold swing (SS) around 135 mV/dec. This work opens a new route to realize high-performance GaAs MOSFETs on (100) substrates potentially. The process development and deep understanding of surface chemistry on these nano-facets could also be very important for the emerging 3D III-V devices. [15-23]

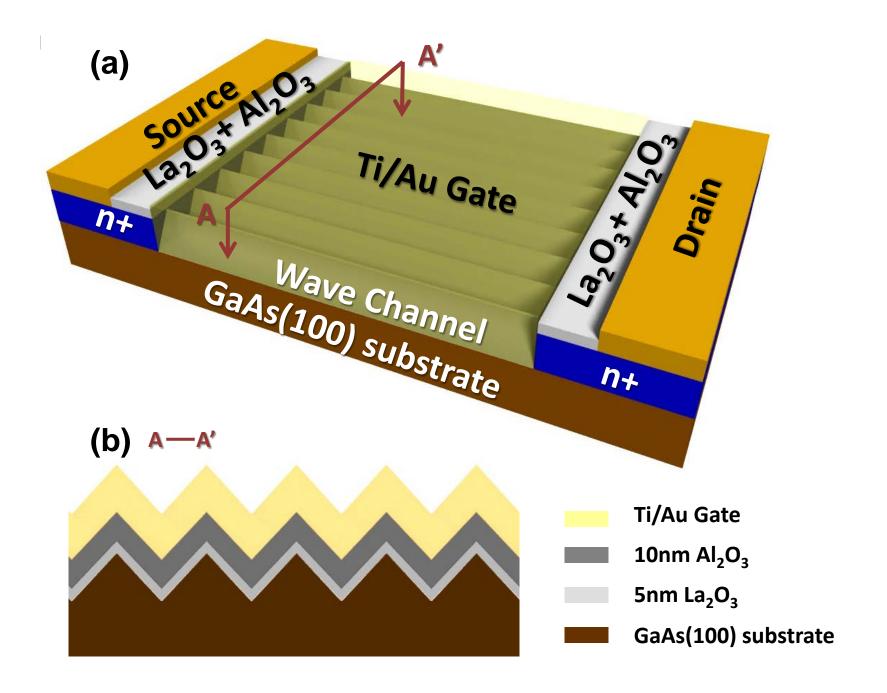

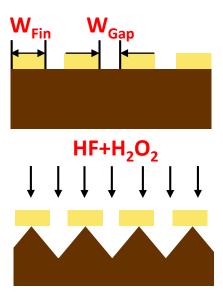

Figure 1(a) and 1(b) show the schematic view and cross-sectional view of a GaAs WaveFET in this work fabricated on a semi-insulating GaAs (100) substrate with an ALE high-k dielectric. The detailed process flow is described in Figure 2(a). An HF and H<sub>2</sub>O<sub>2</sub> based anisotropic wet etching process <sup>[24]</sup> was applied to form the wave structure with Ti/Au as hard mask illustrated in Figure 2(b). MOSFET fabrication starts with 2-inch semi-insulating GaAs (100) substrates. As-received wafers were first degreased by acetone, methanol and isopropanol, then wave patterns were defined by electron beam lithography and Ti/Au were deposited by electron beam evaporator. After lift-off process, periodically patterned Ti/Au strip hard masks were formed as illustrated in Figure 2(b). Then, the wafers were dipped into HF (49%): H<sub>2</sub>O<sub>2</sub> (30%) (10:129) based solution to form the wave-shaped channels. (111)A surface was obtained due to the anisotropic property of the wet etching process <sup>[25]</sup>. The realization of (111)A other than (111)B is further confirmed by the electrical properties of the fabricated devices since the Fermi level on (111)B is expected to be pinned <sup>[111]</sup>. After removal of Ti/Au hard mask by KI

solution, the wafers were dipped into buffered oxide etch (BOE) for 30s and then soaked in 10% (NH<sub>4</sub>)<sub>2</sub>S for 15min for surface passivation. After deionized water rinse, the wafers were quickly transferred into ALD deposition chamber. 5 nm epitaxial La<sub>2</sub>O<sub>3</sub> and 10 nm amorphous Al<sub>2</sub>O<sub>3</sub> were then deposited by ALE/ALD. GaAs WaveFETs with 8 nm amorphous Al<sub>2</sub>O<sub>3</sub> only as gate dielectric were also fabricated as the control sample. The epitaxial La<sub>2</sub>O<sub>3</sub> thin films employed here were deposited from the precursors lanthanum tris(N,N'-diisopropylformamidinate) and H<sub>2</sub>O at 385 °C, while the amorphous Al<sub>2</sub>O<sub>3</sub> oxide capping layer was deposited with precursors of trimethylalumnum (TMA) and H<sub>2</sub>O at 300 °C. The purpose of Al<sub>2</sub>O<sub>3</sub> capping layer is to prevent the reaction between La<sub>2</sub>O<sub>3</sub> and moisture in air and water during the process. Source and drain (S/D) regions were formed by a two-step Si implantation with dose of  $1 \times 10^{14}$  cm<sup>-2</sup> at 30 keV and  $1 \times$  $10^{14}~\text{cm}^{-2}$  at 80 keV, followed by an 850 °C rapid thermal annealing (RTA) in  $N_2$  for 15 s. S/D ohmic contact area was first defined by e-beam lithography, and then BCl<sub>3</sub>/Ar inductively coupled plasma (ICP) dry etching was applied to remove the Al<sub>2</sub>O<sub>3</sub> and HCl wet etching was applied to remove the La<sub>2</sub>O<sub>3</sub> above metal contact area. GeNiAu contact was then formed followed by a 420 °C RTA in  $N_2$  for 15 s. Then, Ti/Au were deposited as gate electrodes and test pads. All patterns were defined by a Vistec UHR electron beam lithography system. The fabricated devices have gate lengths (L<sub>g</sub>) of 1 μm, 2 μm and 4 µm.

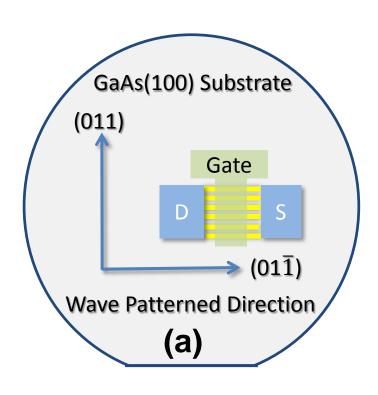

The illustration of anisotropic wet etch process (HF and  $H_2O_2$ ) is shown in Fig. 3. In this process, the wave patterned direction is critical. The wave structure has to be patterned along ( $\mathbf{0}\mathbf{1}\mathbf{\overline{1}}$ ) other than ( $\mathbf{0}\mathbf{1}\mathbf{1}$ ) as shown in Figure 3(a). The effect of wave

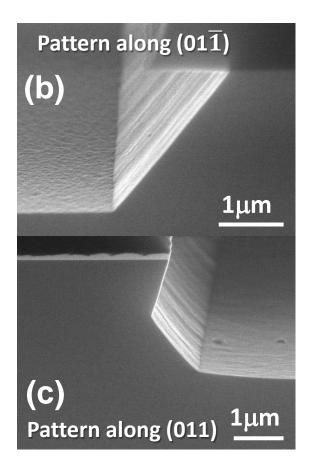

pattern direction is shown by cross-sectional scanning electron microscopy (SEM) pictures in Figure 3(b) and 3(c). Hard mask strips were patterned along  $(01\overline{1})$  in Figure 3(b) and along (011) in Figure 3(c). Clear (111) surface is shown in Figure 3(b) but irregular structures are formed if hard mask strips were patterned along (011). Meanwhile, optimized W<sub>Fin</sub> and W<sub>Gap</sub> are also important to form compact wave structure with sharp corners so that the maximum channel width with (111)A surface can be realized within the fixed channel pitch from the top. Figure 4(a) shows the transmission electron microscopy (TEM) picture of the cross section of the wave channel. A highresolution TEM image of the epitaxial interface, taken from a sample with 5 nm La<sub>2</sub>O<sub>3</sub>/10 nm Al<sub>2</sub>O<sub>3</sub> as gate dielectric, is also shown in Figure 4(b). The lattice mismatch of La<sub>2</sub>O<sub>3</sub> on GaAs (111)A is ~0.04%. It is evident that a flat and sharp interface is formed even on fabricated (111)A nano-facet. It has been proved by C-V measurement that the epitaxial La<sub>2</sub>O<sub>3</sub>/GaAs (111)A interface exhibits D<sub>it</sub> on the order of 10<sup>11</sup> cm<sup>-2</sup> eV<sup>-1</sup>, which is far below the D<sub>it</sub> level of traditional amorphous oxide on GaAs (111)A surface. [12,13] Figure 4(c) depicts the top view SEM image of one finished GaAs WaveFET with a gate length of  $2 \mu m$ .

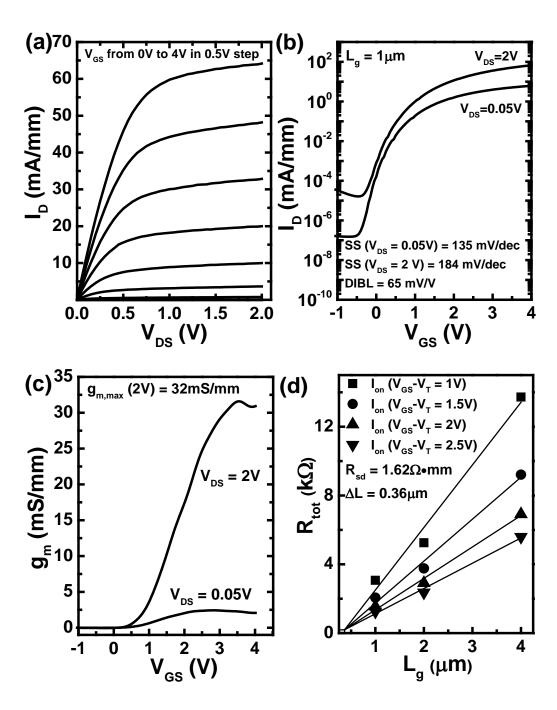

Well-behaved output, transfer and trans-conductance characteristics of a 1  $\mu$ m-gate-length inversion-mode GaAs WaveFET are plotted in Figure 5, showing a maximum drain current ( $I_{D,max}$ ) of 64 mA/mm at a gate bias ( $V_{GS}$ ) of 4 V and a drain bias ( $V_{DS}$ ) of 2 V, a maximum  $g_m$  of 32 mS/mm at  $V_{DS}$  = 2 V and threshold voltage ( $V_T$ ) of 1.32 V. SS of ~135 mV/dec is obtained with an equivalent oxide thickness (EOT) of ~6 nm, indicating a mid-gap interface trap density of 4.5 ×  $10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup> which is simply estimated from

equation SS  $\sim 60 \times (1+qD_{it}/C_{ox})$  mV/dec. SS could be further improved by optimizing fabrication process and reducing EOT. It will also improve the extrinsic drain current and trans-conductance by reducing the EOT of the dielectric and improving interface quality. Devices with different gate length  $L_{g}\ (1,\ 2$  and 4  $\mu m)$  show similar SS and  $V_{T}$  (not shown), indicating these devices are weakly affected by short channel effects. It is also expected that these GaAs devices with a large bandgap and 3D wave structures must have better immunity to short channel effects. The GaAs WaveFET with epitaxial La<sub>2</sub>O<sub>3</sub> demonstrated here has  $I_{D,max}$  about 1,000 × larger than that of the reference GaAs sample with amorphous  $Al_2O_3$  dielectric (not shown) and about  $10,000 \times larger$  than that of GaAs planar MOSFET on GaAs (100) substrate with amorphous Al<sub>2</sub>O<sub>3</sub> [11]. GaAs planar MOSFETs on GaAs (100) substrate with La<sub>2</sub>O<sub>3</sub> as gate dielectric were also fabricated. Without the special surface orientation to form (111) hexagonal template, poor quality La<sub>2</sub>O<sub>3</sub> dielectric was formed on GaAs (100) surface showing a weak gate modulation and minuscule I<sub>D,max</sub>. Figure 5(d) summarizes the effective gate length L<sub>eff</sub> and the series resistance ( $R_{SD}$ ) extracted by plotting  $R_{tot}$  versus  $L_g$ , where  $R_{tot}$  represents the total channel resistance measured from devices with various gate lengths under V<sub>GS</sub>-V<sub>T</sub> from 1 to 2.5 V. R<sub>SD</sub> is determined to be 1.62 Ω·mm, which is reasonable for implanted S/D on GaAs and can be further reduced by optimizing the processes of ion implantation and activation during S/D contact fabrication. Contact resistance (R<sub>C</sub>) of 0.27 Ω·mm is extracted from transmission line method. Two third of R<sub>SD</sub> is from the access resistance between Ohmic contacts to the channel underneath the gate.  $\Delta L$ , defined as the difference between the mask gate length  $L_{g}$  and  $L_{eff}$ , is estimated to be  $\sim 0.36~\mu m$ , due to

the lateral dopant diffusion caused by high-temperature activation and/or the lithographic misalignment.

In conclusion, by realizing (111)A nano-facets on (100) surface by anisotropic wet etching and a high-quality epitaxial La<sub>2</sub>O<sub>3</sub>/GaAs (111)A interface by ALE, we demonstrate inversion-mode GaAs WaveFETs on GaAs (100) substrates with much larger drain currents than those formed on planar GaAs (100) surface using the same dielectric process. The work opens up a new way to improve the III-V device performance by nano-engineering semiconductor 3D structures and interfaces with high-k dielectric.

The authors would like to thank Robert M. Wallace, Andrew Kummel and John Robertson for the valuable discussions. The work at Purdue University was supported by the Air Force Office for Scientific Research, monitored by Dr. Kenneth Goretta. The work at Harvard University was performed at the Center for Nanoscale Systems, a member of the National Nanotechnology Infrastructure Network.

#### References

<sup>1</sup> H. Becke, R. Hall, and J. White, Solid-State Electronics 8 (10), 813 (1965).

<sup>2</sup> M. Hong, J. Kwo, A.R. Kortan, J.P. Mannaerts, and A.M. Sergent, Science 283 (5409), 1897 (1999).

<sup>3</sup> M. Passlack, M. Hong, J.P. Mannaerts, J.R. Kwo, and L.W. Tu, Appl. Phys. Lett. 68, 3605 (1996).

<sup>4</sup> P.D. Ye, G.D. Wilk, J. Kwo, B. Yang, H.-J. L. Gossmann, M. Frei, S.N.G. Chu, J.P. Mannaerts, M. Sergent, and M. Hong, IEEE Electron Devices Lett. 24, 209 (2003).

<sup>5</sup> S.J. Koester, E.W. Kiewra, Y. Sun, D.A. Neumayer, J.A. Ott, M. Copel, D.K. Sadana, D.J. Webb, J. Fompeyrine, and J.P. Locquet, Appl. Phys. Lett. 89, 042104 (2006).

<sup>6</sup> D. Shahrjerdi, M. M. Oye, A. L. Holmes Jr, and S. K. Banerjee, Appl. Phys. Lett. 89, 043501 (2006).

<sup>7</sup> InJo Ok, H. Kim, M. Zhang, T. Lee, F. Zhu, L. Yu, S. Koveshnikov, W. Tsai, V. Tokranov, and M. Yakimov, in IEEE International Electron Devices Meeting (IEDM), December 2006.

<sup>8</sup> C. H.-C. Chin, M. Zhu, Z.-C. Lee, X. Liu, K.-M. Tan, H. K. Lee, L. Shi, L.-J. Tang, C.-H. Tung, and G.-Q. Lo, in IEEE International Electron Devices Meeting (IEDM), December 2008.

<sup>9</sup> R.J.W. Hill, D.A.J. Moran, X. Li, H.P. Zhou, D. Macintyre, S. Thoms, A. Asenov, P. Zurcher, K. Rajagopalan, and J. Abrokwah, IEEE Electron Devices Lett. 28, 1080 (2007).

<sup>10</sup> Y.C. Chang, W.H. Chang, C. Merckling, J. Kwo, and M. Hong, Appl. Phys. Lett. 102, 093506 (2013).

<sup>11</sup> M. Xu, K. Xu, R. Contreras, M. Milojevic, T. Shen, O Koybasi, Y.Q. Wu, R.M. Wallace, and P.D. Ye, in IEEE International Electron Devices Meeting (IEDM), December 2009.

<sup>12</sup> X.W. Wang, L. Dong, J.Y. Zhang, Y.Q. Liu, P. D. Ye, and R.G. Gordon, Nano Lett. 13 (2), 594 (2013).

<sup>13</sup> L. Dong, X.W. Wang, J.Y. Zhang, X.F. Li, R.G. Gordon, and P.D. Ye, IEEE Electron Devices Lett. 34, 487 (2013).

<sup>14</sup> L. Dong, X.W. Wang, J.Y. Zhang, X.F. Li, X.B. Lou, N. Conrad, H. Wu, R.G. Gordon, and P.D. Ye, in 2014 Symposia on VLSI Technology and Circuits (VLSI), 2014.

<sup>15</sup> Y.Q. Wu, R. S. Wang, T. Shen, J. J. Gu, and P. D. Ye, in IEEE International Electron Devices Meeting (IEDM), December 2009.

<sup>16</sup> M. Radosavljevic, G. Dewey, J. M. Fastenau, J. Kavalieros, R. Kotlyar, B. Chu-Kung, W. K. Liu D. Lubyshev, M. Metz, K. Millard, N. Mukherjee, L. Pan, R. Pillarisetty, W. Rachmady, U. Shah, and R. Chau, in IEEE International Electron Devices Meeting (IEDM), December 2010.

<sup>17</sup> F. Xue, A. Jiang, Y.-T. Chen, Y. Wang, F. Zhou, Y.-F. Chang, and J. Lee, in IEEE International Electron Devices Meeting (IEDM), December 2012.

<sup>18</sup> M. Radosavljevic, G. Dewey, D. Basu, J. Boardman, B. Chu-Kung, J. M. Fastenau, S. Kabehie, J. Kavalieros, V. Le, W. K. Liu, D. Lubyshev, M. Metz, K. Millard, N. Mukherjee, L. Pan, R. Pillarisetty, W. Rachmady, U. Shah, H. W. Then and R. Chau, in IEEE International Electron Devices Meeting (IEDM), December 2011.

<sup>19</sup> J. J. Gu, X. W. Wang, J. Shao, A. T. Neal, M. J. Manfra, R. G. Gordon, and P. D. Ye, in IEEE International Electron Devices Meeting (IEDM), December 2012.

<sup>&</sup>lt;sup>20</sup> A.V. Thathachary, N. Agrawal, L. Liu, and S. Datta, Nano Lett. 14, 2 (2014).

N. Waldron, C. Merckling, L. Teugels, P. Ong, S. A. U. Ibrahim, F. Sebaai, A. Pourghaderi, K. Barla, N. Collaert, and A. V. Y. Thean, IEEE Electron Devices Lett. 35, 1097(2014).

<sup>23</sup> T.W. Kim, D.H. Kim, D.H. Koh, H.M. Kwon, R.H. Baek, D. Veksler, C. Huffman, K. Matthews, S. Oktyabrsky, A. Greene, Y. Ohsawa, A. Ko, H.Nakajima, M. Takahashi, T. Nishizuka, H. Ohtake, S. K. Banerjee1, S.H. Shin, D.H. Ko, C. Kang, D. Gilmer, R.J.W. Hill, W. Maszara, C. Hobbs and P.D. Kirsch, in IEEE International Electron Devices Meeting (IEDM), December 2013.

<sup>&</sup>lt;sup>22</sup> C. Zota, L. Wernersson, and E. Lind, IEEE Electron Devices Lett. 35, 342 (2014).

<sup>&</sup>lt;sup>24</sup> W.T. Tsang and A.Y. Cho, Appl. Phys. Lett. 30, 293 (1977).

<sup>&</sup>lt;sup>25</sup> W.T. Tsang and S. Wang, Appl. Phys. Lett. 28, 44 (1976).

### **Figure Captions**

Figure 1 (a) Schematic and (b) Cross-sectional view of an inversion-mode GaAs (100) WaveFET with ALE La<sub>2</sub>O<sub>3</sub>.

Figure 2 (a) Fabrication process flow for inversion-mode GaAs (100) WaveFET with ALE high-k La<sub>2</sub>O<sub>3</sub>. (b) Illustration of wave channel formation by anisotropic wet etching. GaAs (111)A surface on these nano-facets is achieved by anisotropic wet etching of GaAs using HF solution.

Figure 3 (a) Schematic diagram of wave patterned orientation. (b) and (c) Cross-sectional SEM images of wave structures patterning along  $(01\overline{1})$  and (011) orientations.

Figure 4 (a) Cross-sectional STEM image of GaAs WaveFET structure covered with  $La_2O_3$  and  $Al_2O_3$ . (b) HRTEM image of  $La_2O_3$ /GaAs interface. Epitaxial  $La_2O_3$  forms a flat and sharp interface on wave surface. (c) SEM image of a GaAs (100) WaveFET device top view with  $L_g = 2\mu m$ . Parallel wave structures are clearly shown as device channel.

Figure 5 (a) Output and (b) transfer (c)  $g_m$  characteristics of a GaAs WaveFET with  $L_g = 1~\mu m$ . The device shows maximum drain current of 64 mA/mm, a subthreshold swing of 135 mV/dec, a peak trans-conductance of 32 mS/mm, and an  $I_{ON}/I_{OFF}$  greater than  $10^7$ . (d) Measured total resistance versus different mask gate lengths as a function of gate bias.  $R_{SD}$  of  $1.62~\Omega\cdot mm$  and  $\Delta L$  of  $\sim 0.36~\mu m$  are determined from the fitting lines.

(a) ◆ Semi-Insulating GaAs(100) Substrate

- **♦** Wave Channel Formation

- <1> Hard Mask Deposition (Ti/Au)

- <2> Wave Channel Etching (HF+H<sub>2</sub>O<sub>2</sub>)

- <3> Gold Removal (KI solution)

- ◆ Gate Dielectric Deposition

(BOE 30s and (NH₄)₂S Surface Passivation)

- 5nm La<sub>2</sub>O<sub>3</sub>/10nm Al<sub>2</sub>O<sub>3</sub>

- 8nm Al<sub>2</sub>O<sub>3</sub>

- **♦** Si-Implantation (Two-step: 30KeV/1x10<sup>14</sup>cm<sup>-2</sup>/80KeV/1x10<sup>14</sup>cm<sup>-2</sup>)

- ◆ Dopant Activation (850°C, 15s in N₂)

- **♦** S/D Contact Formation

- <1> Oxide Etching

(BCl<sub>3</sub>/Ar Dry Etch for Al<sub>2</sub>O<sub>3</sub>/HCl Wet Etch for La<sub>2</sub>O<sub>3</sub>)

- <2> Metal Deposition (GeNiAu)

- <3> Ohmic Anneal (420°C, 15s in N<sub>2</sub>)

- Gate Electrode Formation (Ti/Au)

(b)