# Automated Translation: Generating a Code Generator

#### Citation

Feigenbaum, Lee D. 2001. Automated Translation: Generating a Code Generator. Harvard Computer Science Technical Report TR-12-01.

#### Permanent link

http://nrs.harvard.edu/urn-3:HUL.InstRepos:25104998

#### Terms of Use

This article was downloaded from Harvard University's DASH repository, and is made available under the terms and conditions applicable to Other Posted Material, as set forth at http://nrs.harvard.edu/urn-3:HUL.InstRepos:dash.current.terms-of-use#LAA

### **Share Your Story**

The Harvard community has made this article openly available. Please share how this access benefits you. <u>Submit a story</u>.

**Accessibility**

### Automated translation: generating a code generator

A Thesis presented

by

Lee D. Feigenbaum

to

Computer Science

in partial fulfillment of the honors requirement

for the degree of

Bachelor of Arts

Harvard College

Cambridge, Massachusetts

April 2, 2001

#### Abstract

A key problem in retargeting a compiler is to map the compiler's intermediate representation to the target machine's instruction set.

One method to write such a mapping is to use grammar-like rules to relate a tree-based intermediate representation with an instruction set. A dynamic-programming algorithm finds the least costly instructions to cover a given tree. Work in this family includes Burg, BEG, and twig. The other method, utilized by gcc and VPO, uses a hand-written "code expander" which expands intermediate representation into naïve code. The naïve code is improved via machine-independent optimizations while maintaining it as a sequence of machine instructions. Because they are inextricably linked to a compiler's intermediate representation, neither of these mappings can be reused for anything other than retargeting one specific compiler.

$\lambda$ -RTL is a language for specifying the semantics of an instruction set independent of any particular intermediate representation. We analyze the properties of a machine from its  $\lambda$ -RTL description, then automatically derive the necessary mapping to a target architecture. By separating such analysis from compilers' intermediate representations,  $\lambda$ -RTL in conjunction with our work allows a single machine description to be used to build multiple compilers, along with other tools such as debuggers or emulators.

Our analysis categorizes a machine's storage locations as special registers, general-purpose registers, or memory. We construct a data-movement graph by determining the most efficient way to move arbitrary values between locations. We use this information at compile time to determine which temporary locations to use for intermediate results of large computations.

To derive a mapping from an intermediate representation to a target machine, we first assume a compiler-dependent translation from the intermediate representation to register-transfer lists. We discover at compile-compile time how to translate these register-transfer lists to machine code and also which register-transfer lists we can translate. To do this, we observe that values are either constants, fetched from locations, or the results of applying operators to values. Our data-movement graph covers constants and fetched values, while operators require an appropriate instruction to perform the effect of the operator. We search through an instruction set discovering instructions to implement operators via the use of algebraic identities, inverses, and rewrite laws and the introduction of unwanted side effects.

# Contents

| 1  | Introduction and Overview                                                                                                                        | 5                          |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2  | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                             | 13<br>13<br>13<br>16<br>17 |

| 3  | Spaces and Location Sets3.1 Motivation3.2 Spaces: Analysis3.3 Spaces: Implementation3.4 Location Sets: Analysis3.5 Location Sets: Implementation | 19<br>20<br>24<br>25<br>29 |

| 4  | Choosing Locations for Variables 4.1 Motivation                                                                                                  | 31<br>32<br>34<br>39       |

| 5  | From RTL to Machine Code  5.1 Motivation                                                                                                         | 41<br>42<br>47<br>57<br>65 |

| 6  | Related Work                                                                                                                                     | 69                         |

| 7  | Summary and Conclusions7.1Summary7.2Reduction of Full RTLs7.3Questions Raised7.4Conclusions                                                      | <b>73</b> 73 73 75 76      |

| Re | eferences                                                                                                                                        | 81                         |

# Chapter 1

### Introduction and Overview

A vast array of commercial and academic low-level tools involve the semantics of instruction sets. Emulators, debuggers, profilers, and binary translators are but a few examples of tools involving machine-independent algorithms that must be able to operate on machine-level and often machine-specific code. Perhaps the most basic and widespread of tools in this category is the compiler, charged with generating machine instructions for a particular architecture from a high-level source language.

Particularly in academia, where compilers are used to study many engineering and algorithmic problems and where new hypothetical architectures are continually devised, the ability to quickly and easily retarget an existing compiler to a new architecture is necessary. We seek to automate the creation of code generators from compiler-independent machine descriptions. A look at the stages involved in a typical compiler will help us determine the main problems involved in retargeting a compiler.

The first responsibilities of a compiler are the lexing and parsing of the input language, from which an abstract-syntax tree is created. This process is independent of the target machine, and nothing need change when the compiler is retargeted. Similarly, the compiler may perform static-semantic checking without affecting retargeting. At this point, the code is usually translated into a compiler-specific intermediate representation.

One of the first machine-dependent issues handled by the compiler involves the target architecture's calling conventions. The compiler must arrange for the inputs to and outputs from procedures to be placed in the appropriate locations for the

target machine. The Calling Convention Language, part of the Zephyr Compiler Infrastructure, may be used to describe these conventions in a machine-independent fashion (Bailey and Davidson 1995). We do not deal with calling conventions in the rest of our work, assuming that the inputs and outputs to a procedure have already been moved to the appropriate locations.

At this point, the compiler must choose machine instructions to implement the intermediate representation. If registers are used, the compiler must somehow handle the limited supply of registers that the hardware provides. This is done via the introduction of temporary locations to stand for registers. The use of temporaries allows the compiler to act as if it has an infinite supply of registers to work with, rather than being limited by hardware constraints. Which classes of temporary locations are available depends upon the particular registers available on the target machine, and hence this step is machine-dependent. Following instruction selection, hardware registers are allocated to replace the temporaries. We do not take up register allocation in this paper, but machine-independent register-allocation algorithms have been available for years (Chaitin 1982, Briggs, Cooper, and Torczon 1994, George and Appel 1996, Poletto and Sarkar 1999).

In addition to the above stages, compilers may perform optimizations throughout the entire process. High-level optimizations may be applied to abstract-syntax trees as well as to the intermediate representation. Further optimizations can take place following instruction selection or even after register allocation. Some optimizations may be machine independent, while others may depend on properties of the target architecture.

We see that the major areas that must be addressed in retargeting a compiler are optimizations and the generation of machine code from an intermediate representation. These two areas represent the last barrier towards automating compiler retargeting. Both are usually done by hand, yet there are currently two families of work devoted to aiding the instruction selection and optimization phases of retargeting a compiler.

The Backend Generator (BEG), Burg, iburg, and Twig are all systems based on bottom-up tree rewriting system (BURS) theory. They produce code generators with guarantees of local optimality (Fraser, Hanson, and Proebsting 1992). All are driven

by a set of grammar-like tree-matching rules. These rules specify which computations may develop values into temporary locations, at what cost. Based on these rules, each tool in this family uses a dynamic-programming algorithm to discover sequences of instructions that implement larger computations. Given a tree representing a source language statement, the algorithm finds the tree cover with the lowest cost, based on the rules used.

This approach guarantees local optimality, but says nothing of the overall quality of the code it generates. A different approach is taken by software including the GNU C Compiler (gcc) and Very Portable Optimizer (VPO). This family attempts to gain efficiency via the use of machine-independent optimizations performed on a machine-independent and yet machine-level intermediate representation (Davidson and Fraser 1984, Benitez and Davidson 1988). This strategy encourages handwritten "code expanders" to produce naïve code that can then undergo various code-improving transformations. Typically, software in this category requires three components: a naïve code expander, a set of semantics-preserving optimizations, and a recognizer. The code expander is required to emit a sequence of statements, each representable as a single instruction on the target machine. This property is known as the machine invariant. The recognizer tests whether a given statement satisfies the machine invariant. The optimizer repeatedly applies optimizations, using the recognizer after each to ensure that the machine invariant has not been violated. If at any point the invariant does not hold, the offending optimization is undone.

While both of these families are designed to aid in producing an easily retargeted compiler, they both require a compiler author to create a new mapping from an intermediate representation to an instruction set for every new target machine. Such a mapping would also be a part, of course, of creating a new back end for any compiler not explicitly designed for retargetability. Because each such mapping is linked not only to the target architecture but also to a compiler's particular intermediate representation, the mappings cannot be reused, whether it be in another compiler or in other tools altogether. Under the current state of the art, then, every compiler author must write a mapping for every desired target machine—an  $O(m \times n)$  situation.

$\lambda$ -RTL is a language for specifying the semantics of machines' instructions in a manner independent of any particular intermediate representation (Ramsey and

Davidson 1998).  $\lambda$ -RTL allows the effect on the state of a machine of every instruction in an instruction set to be specified using register-transfer lists (RTLs). Our work demonstrates how the mappings described above can be automatically derived from  $\lambda$ -RTL machine descriptions, instead of written by hand.

If this goal is reached, the  $O(m \times n)$  problem from above is reduced to an O(m+n) problem: a compiler author need only write by hand a mapping from the compiler's intermediate representation to our RTLs *once*, and, similarly, a  $\lambda$ -RTL description for any given target machine need only be composed *once*. Moreover, our analyses our sufficiently general to be used to generate other tools, such as emulators, debuggers, or binary translators.

The main challenge in deriving this mapping from a machine description can be stated succinctly as discovering how to use the instruction set to place the results of arbitrary computations into arbitrary locations. We approach this challenge via an analysis of the locations and operators involved in a given target architecture.

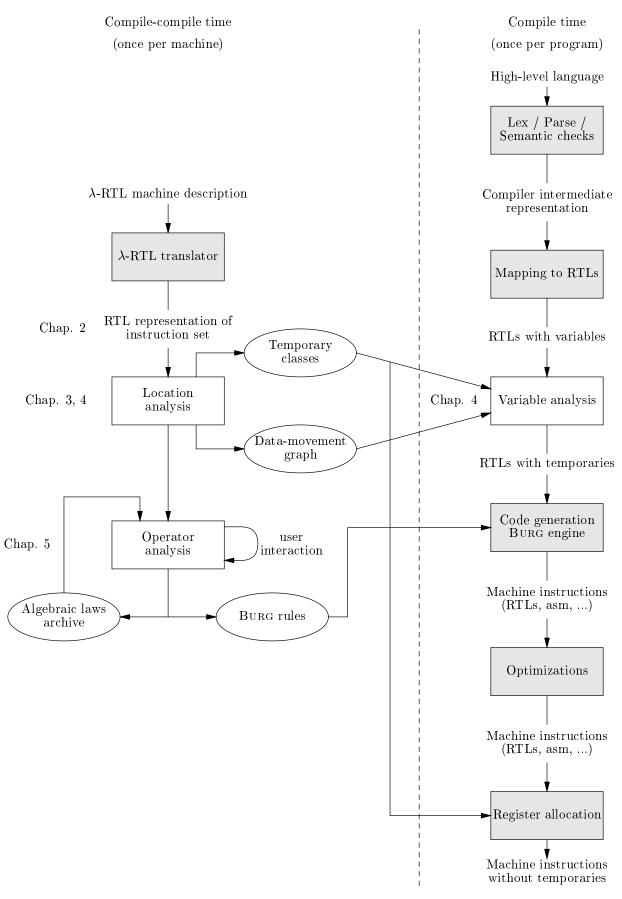

Figure 1.1 depicts the entire process, including both what happens at compile-compile time<sup>1</sup> and also the compile-time components of a compiler that we discuss above. The white regions represent the work that we present in this paper. The process begins at compile-compile time with a  $\lambda$ -RTL description of a target machine's instructions' semantics. Our analysis begins once the  $\lambda$ -RTL translator has produced RTLs for the entire instruction set from the machine description. We first perform a location-driven analysis. We classify the target machine's locations via an examination of their use within the instruction set. From this classification we determine the classes of temporaries that will be used throughout the compiler. We also construct a data-movement graph by searching the instruction set for instructions that move values between locations on the machine.

Both the temporary classes and data-movement graph are used within the next phase of our compile-compile-time analysis. This phase is driven by the desire to find instructions to implement all operators that may be involved in arbitrary computations. Particularly on a CISC machine, a single instruction may involve multiple operators, and it is likely that a single operator will occur in multiple instructions

<sup>&</sup>lt;sup>1</sup>Compile-compile time refers to the time when a compiler is generated. Compile time refers to the time when a compiler transforms a source program to assembly or machine code.

Figure 1.1: The overall process—white regions are presented in this paper

within a target architecture. We present various strategies to find the cheapest way to implement a single computation of each operator. Based on the result of this operator analysis, we discuss a framework to emit Burg rules to drive instruction selection at compile time. We frame our compile-compile-time analyses as an inductive proof of which source RTLs our code generator will be able to translate. If a compiler author composing a mapping from his intermediate representation to RTLs ensures that the only RTLs he produces fall within the set of RTLs that we prove we can translate, he is guaranteed that our back end will successfully generate code for his front end.

At compile time, the compiler front end behaves as normal, lexing and parsing a high-level language and then creating abstract syntax and—perhaps after high-level optimizations and semantic checking—transforming the code into an intermediate representation. The compiler then maps this intermediate representation to RTLs, at which point code generation begins. The RTLs at this point contain variables; we use the data-movement graph and our classes of temporaries to perform a simple analysis that assigns each variable to a temporary. Using the rules generated at compile-compile time, a Burg engine then expands each RTL into a sequence of machine instructions. We leave the representation of the instructions unspecified—it may be RTLs or assembly code or some other format. Following any additional optimizations along the lines of gcc and VPO, the register allocator runs, using the information about our temporary classes in order to assign hardware locations to all temporaries, while spilling temporaries to memory if necessary.

We present several instruction-set analyses in this thesis. In Chapters 3 and 4, we answer the questions, what storage locations are available on the target architecture and where should we store intermediate results of computations. We first develop formalisms with which we can express the problems and solutions, and then present implementations of the analyses. In Chapter 5 we then study the question: How do we use intermediate results in arbitrary computations? We propose a complete instruction-set analysis to answer this question.

We draw on many examples from actual architectures, particularly the SPARC, as we go along. In order to help illustrate the overall picture, we present a running example involving the translation of a single C procedure into assembly code for a fictitious and very simple machine known affectionately as the Tiny Machine. Our

```

int almostManhattanDistance(int x1, int y1, int x2, int y2) {

return((x1 - x2) + (y1 - y2));

}

```

Figure 1.2: The C procedure we translate for the Tiny Machine

```

%r4

li

20,

# Set up a 20-byte stack frame

sub

%sp, %sp,

%r4

%r0

ld

%sp,

0,

# Load the values of the function's

%sp,

%r1

# parameters from the stack into

ld

4,

%sp,

8,

%r2

# registers

ld

ld

%sp,

12,

%r3

%r0, %r2,

%r5

# Perform the Manhattan distance

sub

%r1, %r3,

%r6

# calculation

sub

%r5, %r6,

%r7

add

# Store the return value on the stack

st

%sp, 16,

%r7

```

Figure 1.3: The final assembly code output from translating almostManhattanDistance

example deals with the translation of the procedure in Figure 1.2 that *almost* calculates the Manhattan distance between two points.<sup>2</sup> As we go through the process outlined above, we will show how this procedure gets translated into the assembly code given in Figure 1.3. The next chapter presents the details of the Tiny Machine's architecture.

<sup>&</sup>lt;sup>2</sup>So named as it represents the distance between two points traveling only along horizontal and vertical 'city blocks.' For our function to actually calculate the correct Manhattan distance, we would need to take the absolute values of the two differences.

# Chapter 2

# Background

#### 2.1 Machine State

$\lambda$ -RTL posits that a machine's state can be fully represented as a collection of sets of mutable cells (Ramsey and Davidson 1998). We refer to each set of mutable cells as a *space*. We can then uniquely identify a cell by providing the space that it belongs to and its index within that space. For example, on the SPARC, integer registers, floating-point registers, and memory are three different spaces. r[3] refers to the fourth cell within r-space, i.e., the fourth integer register. This model of a machine's state extends without difficulty to less traditional locations such as the program counter and condition codes. Thus on the SPARC, the condition codes are nothing more than bits 20-23 of the Process State Register, represented in the  $\lambda$ -RTL machine description as i[0].

#### 2.2 Register-transfer Lists

A register-transfer list is a list of guarded effects that transform a machine's state. Each guarded effect consists of a guard and an assignment, itself composed of a left-hand side and a right-hand side. The left-hand side of the assignment specifies which locations of the machine's state are modified. The right-hand side specifies the new values for these locations. The guard specifies under what conditions this change of state occurs. Multiple guarded effects within a single RTL occur simultaneously.

RTLs have their roots in the ISP descriptions of Bell and Newell (1971). ISP descriptions allowed for nested sequences of actions predicated on conditions, describing instructions' effects on processors' memories and registers. ISP was not formally specified until it evolved into ISPS (Siewiorek, Bell, and Newell 1982). Davidson adapted register transfers in his original work on machine-independent optimizations (Davidson and Fraser 1984). Richard Stallman borrowed some ideas from these RTLs to create GNU's register-transfer language, a mix of semantic effects, pipeline information, and compiler-dependent C-code (Stallman 1999). The current detailed formalism of RTLs that we use was established by Ramsey and Davidson, and eliminates the last vestiges of any machine-dependent aspects (Ramsey and Davidson 1998).

While actual RTLs contain great amounts of detail in a tree form, we use a simplified meta-language borrowed from  $\lambda$ -RTL for convenience in referring to RTLs. We write the general form of an RTL as

$$g_1 \to l_1 := e_1 \mid g_2 \to l_2 := e_2 \mid \dots \mid g_n \to l_n := e_n$$

In this form, each  $g_i$  stands for a guard,  $l_i$  for a location, and  $e_i$  for an expression. We use  $\to$  to indicate that the expression on the left guards the effect on the right. An expression on the right-hand side of an assignment can be a constant, a variable, a value fetched from a location, or an operator applied to a list of one or more expressions. If an assignment is not predicated on a condition (or, equivalently,  $g_i = \text{true}$ ), then we omit the guard for that effect altogether. An empty RTL—a no-op—is represented as Rtl.Skip.

For example, the SPARC's and instruction might be represented as the RTL  $r[rd] := r[rs1] \land r[rs2]$ . While this example represents the general form of the and instruction, we use the same notation to refer to a specific instance of such an instruction, as in  $r[3] := r[7] \land r[4]$ . As another example, consider the SPARC swap instruction, r[rd] := r[rd] + rs2 | r[rs1 + rs2] = r[rd]. Because multiple effects within a single RTL occur simultaneously, we can define such an instruction without using temporary values.

Figure 2.1 is a formal specification of the RTLs we use. These RTLs have a rather simple structure. Expressions are built recursively through the application of operators to lists of expressions, with leaf expressions being constants, instruction

```

bit vector

width = (int) -- size of a value, in bits

const

operator

function

exp

= CONST

(const)

name

string

| FETCH

(location, width)

space

mutable store

| APP

(operator, exp*)

Meanings of unspecified

terminal symbols

| OPERAND (name, width)

location = LOC

(space, exp, width)

VAR

(name, width)

effect

= STORE (location dst, exp src, width)

KILL

(location)

= GUARD (exp, effect)

guarded

rtl

= RTL

(guarded*)

```

Figure 2.1: ASDL specification of the form of RTLs. Variables appear in italics as they can only occur within source RTLs and not within the RTLs that represent a machine's instruction set.

operands, or fetches from locations. A location may either be a machine location (including temporaries, see Chapter 3), or a variable. Variables may only occur within source RTLs. The RTLs that represent machine instructions do not contain variables.

The formalism used within this paper is a slight simplification of the actual RTLs we use. In particular, the full RTLs distinguish between *cells* and *locations*, allowing the user to dictate aggregations that specify how to interpret multiple cells as a single location. Aggregations are largely orthogonal to our work here, and so we ignore them for expository purposes. We make use of this basic structure of RTLs in our analyses below.

The RTLs used within our system have several properties distinguishing them from other systems. First, every node within a tree has its width (size in bits) fully specified. In particular, the width of every operand of an operator is given in the RTL, along with the width of the result of a computation with that operator. In addition, all fetches are explicit. On the surface, when we write RTLs in our metalanguage, we hide the difference between a location and a value fetched from that

location. Within the actual RTLs manipulated by our tools however, this distinction is made explicit. Both of these properties help to fully disambiguate the meaning of a given RTL. Nothing is left implicit and the tools that manipulate these RTLs have all relevant information directly available.

We present some details of the type system used by our RTLs here, in order to develop notation that is used throughout the paper. Consider the RTL add operator, which has type #n bits \* #n bits -> #n bits. This indicates that add is a function that takes two inputs, each of type #n bits and yields a single result, also of type #n bits. Each of these types is made up of two parts: #n is a variable of kind number, while the bits type constructor transforms values of kind number to types. Operators that contain number variables such as this are polymorphic; for all n, the add operator has a specific type. That is, an operator is specialized to a particular type by supplying specific values for the variables in the operator's type. Thus add might be specialized to add #32 with type #32 bits \* #32 bits -> #32 bits. When we use an operator in an instruction, all number variables must be specified to concrete widths.

#### 2.3 $\lambda$ -RTL

While the RTLs described above are structurally simple enough to be easily manipulated by tools, the high level of detail makes writing them by hand tedious.  $\lambda$ -RTL is a fully typed functional language based largely on Standard ML that provides a convenient environment for specifying RTLs for a target machine's instruction set. The  $\lambda$ -RTL translator is able to infer most widths and aggregations. Additionally, the translator conflates locations and values fetched from location such that writing r[4] can mean either a specific register or the value currently in that register, depending on context.

$\lambda$ -RTL also allows someone writing a machine description to treat bit slices of cells as full-fledged locations that can be manipulated directly. For example, to set the carry flag of the SPARC's condition codes, one would write the  $\lambda$ -RTL expression  $[0] \color \c$

The availability of a full-fledged functional language greatly simplifies the specification of instructions with semantics that are conditional on their operands by providing a standard if-then-else construct. A grouping mechanism provided by  $\lambda$ -RTL facilitates batch definitions of instructions with similar meanings.  $\lambda$ -RTL also defines a set of approximately 70 standard RTL operators that are automatically included in all machine descriptions (Ramsey and Lindig 2001, Ramsey and Davidson 1998). In addition, an author of a  $\lambda$ -RTL machine description may define machine-specific operators.

### 2.4 Tiny Machine

The Tiny Machine contains a single set of 16 32-bit integer registers, \$r[0]...\$r[15], as well as a primary memory. The Tiny Machine uses only base-displacement addressing into the primary memory. The Tiny Machine uses register 15 as the stack pointer, and it passes values to and from procedures via the stack. The instruction set contains the following five instructions:

- add rs1,rs2,rd. Sum the values in \$r[rs1] and \$r[rs2] and place the result in \$r[rd].

- sub rs1, rs2, rd. Take the difference of the values in \$r[rs1] and \$r[rs2] and place the result in \$r[rd].

- 1i con22, rd. Sign-extend the 22-bit constant con22 to 32 bits and load it into \$r[rd].

- ld rs1, con18, rd. Load the value at \$m[\$r[rs1] + con18] from memory into \$r[rd], where con18 is an 18-bit constant sign-extended to 32 bits.

- st rs1, con18, rd. Store the value in \$r[rd] into memory at \$m[\$r[rs1] + con18].

The Tiny Machine's instruction set's semantics are given by the  $\lambda$ -RTL machine description in Figure 2.2. The aggregate using RTL.AGGL line in the description indicates that the Tiny Machine is a little-endian machine, though aggregations are

```

module TinyMachine is

import RTL

from StdOperators import [sx := + -]

storage

'r' is 16 cells of 32 bits called "registers"

cells of 8 bits called "memory" aggregate using RTL.AGGL

operand [rs1 rs2 rd] : #4 bits

operand cons10

: #10 bits

operand con18

: #18 bits

operand con22

: #22 bits

operand address

: #32 bits

default attribute of

addr(rs1, con18) : address is $r[rs1] + sx con18

default attribute of

li(con22, rd) is r[rd] := sx con22

ld(address, rd) is $r[rd] := $m[address]

st(address, rd) is $m[address] := $r[rd]

default attribute of

add(rs1, rs2, rd) is r[rd] := r[rs1] + r[rs2]

sub(rs1, rs2, rd) is r[rd] := r[rs1] - r[rs2]

end

```

Figure 2.2:  $\lambda$ -RTL machine description for the Tiny Machine

immaterial to the rest of this paper. The default attribute of sections define both the Tiny Machine's addressing mode (addr) as well as the semantics of the Tiny Machine's instructions.

# Chapter 3

# Spaces and Location Sets

#### 3.1 Motivation

A human being's natural unit of computation is often much larger than a machine's. For example, we would not expect to find a single machine instruction that performs the Manhattan distance calculation (x1 - x2) + (y1 - y2) presented in Figure 1.2. When generating code for a computation too large to be represented by a single instruction on the target architecture, a compiler must break the large computation into smaller computations that can each be implemented by a single machine instruction.

By breaking up large computations in this manner, the compiler has created a new problem: Where on the machine should the intermediate results be stored? We must pick actual hardware locations for these values. More specifically, we would like to store these values within registers. However, not all registers are created equal. Some, such as the program counter or status registers, have defined purposes that prevent them from being used for intermediate results. Others may be intended to store floating-point values, or to store addresses as opposed to data.

Why do we prefer to store intermediate results in registers in the first place? The answer is twofold: First, registers are designed to be accessed more efficiently than memory. Second, the compiler has complete control over choosing—at compile time—which registers to use for which values.<sup>1</sup> Despite these advantages, there is

<sup>&</sup>lt;sup>1</sup>Also, registers are rich and chocolatey!

another difficulty. The number of variables and intermediate results involved in a large computation may be greater than the number of actual hardware registers available.

The standard solution to this problem involves the introduction of temporary locations and the use of a register allocator. To handle the limited supply of hardware locations, we create infinite supplies of temporary locations and allow the code generator to use these temporaries to store the intermediate results of computations. Following code generation, the register allocator maps the temporary locations to actual hardware registers. When there are more live values than available registers, the allocator inserts instructions to spill some values to memory and later reload these values from memory when they are needed again.

We cannot, however, simply deal with a single infinite supply of temporary locations. Because the actual hardware registers themselves are not all the same, we must separate our infinite supply of temporaries into different classes, associating each class of temporaries with one specific set of hardware registers. This relation says, in essence, that the register allocator may replace a location within a given class of temporaries with *any* location from the associated set of registers.

We do not wish to be limited to working with predefined types of register sets. Looking at the SPARC or MIPS architectures, we might conclude that we can classify all register sets as either integer or floating point. This characterization would fail, however, for a machine such as the Motorola 68000 that distinguishes between data and address register sets. As we noted above, the different temporary classes required directly depends on the different register sets available. Thus, before we can think about automatically generating code, we want to automatically discover the appropriate classes of temporary locations from a target machine's  $\lambda$ -RTL semantic description.

### 3.2 Spaces: Analysis

We have seen that  $\lambda$ -RTL divides locations within a machine into spaces. Before we can discern appropriate classes of temporary locations, we must examine an instruction set and determine which spaces correspond to sets of registers on the target machine. Spaces within a  $\lambda$ -RTL description are not annotated with this information,

and so we make this determination via an examination of *how* locations within spaces are used within the target machine's instruction set.

Achieving this goal is intimately connected with the binding times of expressions found within  $\lambda$ -RTL descriptions. There are three possibilities for this binding time:

- The value of an expression can be known at *specification time*. We can tell the values of these expressions simply by examining an instruction's opcode. The values of these expressions do not depend on the instruction's operands nor on the state of the machine. For example, the SPARC's call instruction involves a control transfer to the address PC + (4 \* disp30). In this address the value of the constant 4 is known at specification time; no matter when or with what operands call is invoked, the value of that expression is always 4.

- The value of an expression can be known at instruction-creation time. This is the case for expressions whose values depend on the particular operands with which an instance of an instruction is created. The values of expressions that are known at instruction-creation time cannot depend on the machine's state. In the calculation of the address for the call instruction above, disp30 is an operand to the instruction, and hence the value of disp30 is bound when a specific instance of the call instruction is created; no matter the machine's state when this instance is invoked, the value of this expression is unchanged.

- The value of an expression can be known at *run time*. This is the case for expressions whose values depend on the current state of the machine. The SPARC's st instruction stores into memory the value stored within a register, \$r[rs1], where rs1 is an operand to st. The value of the expression \$r[rs1] is bound at run time, as the value fetched from a register depends on the machine's state at the moment st is executed.<sup>2</sup> Expressions with values bound at run time will likely have different values when the *same instance* of an instruction is executed at multiple times.

Aside from atomic expressions such as constants, instruction operands, and values fetched from locations or variables, Figure 2.1 shows us that an expression can involve

<sup>&</sup>lt;sup>2</sup>The value of rs1 is bound at instruction-creation time and hence we know at instruction-creation time to which register rrs1 refers. But it is not until run time that we know what value is stored in that register.

applying an operator to one or more expressions. In this case, the binding time of the value of the resulting expression is directly related to the binding time of the values of the constituent expressions. In fact, we can simply state that the binding time of the über-expression is the *latest* binding time of the values of the operand expressions. Thus, in the call instruction the value of the expression 4 \* disp30 is bound at instruction-creation time. In one version of the SPARC add instruction—

\$r[rd] := \$r[rs1] + simm13—a value fetched from a register is added to one of the instruction's operands, simm13. As the operand's value is bound at instruction-creation time while the value fetched from \$r[rs1] is bound at run time, the entire expression \$r[rs1] + simm13 has a value that is bound only at run time.

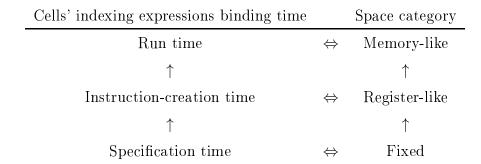

Returning to our view of a machine's state as collections of sets of mutable cells, we again note that a cell is specified completely by its space and its index (offset) within that space. By examining the binding time of cell's indexes, we can identify the register sets for a given architecture.

We noted above that one benefit of using registers to hold intermediate results is that the compiler controls which registers are used for which values. As a corollary to this, one defining characteristic of a register set is that specific registers used by an instruction are always known at *instruction-creation time*. That is, no matter how many times an instruction involving a register is executed, and no matter how the machine state varies, that instance of the instruction always refers to the same register.<sup>3</sup> On the flip side, it is usually the case that the specific register involved in an instance of an instruction is specified by one of the instruction's operands.<sup>4</sup> Given this observation, we can break spaces into three categories, based upon the binding time of the expressions used to index cells within them:

• A fixed space is one whose constituent cells are always indexed by expressions with values bound at specification time. Because of this relationship, locations within a fixed space are determined by the instruction's opcode only. The SPARC i-space, containing the integer-unit control and status registers, is an example of a fixed space. Locations within this space include the program

of this, as it saves the current value of the program counter into integer register 7: \$r[7]

<sup>&</sup>lt;sup>3</sup>Though as we have just noted, the value within that register *does* vary with the machine state. <sup>4</sup>We say 'usually' rather than 'always', for many architectures have instructions that refer directly (independent of operands) to specific registers. The call instruction on the SPARC is an example

counter and the processor-state register, which contains, among other things, the integer condition codes. All instructions that refer to a cell within this space do so directly, rather than via an instruction operand or machine state. For example, every instruction that refers to the processor-state register refers to it as \$i[0]. In general, all instances of an instruction that refers to locations in fixed spaces refer to the *same* locations within that space, regardless of both the values of the instructions' operands and also the current machine state.

- A register-like space is one that is not a fixed space and whose constituent cells are indexed by expressions with values bound either at specification time or at instruction-creation time. Because of this, locations within a register-like space may depend on operands of the instruction, but they are independent of machine state. The SPARC integer register r-space is an example of a register-like space, as is the SPARC floating-point register f-space. An instruction that refers to a cell within r-space either does so directly, as in the term \$r[7] or (in the usual case) via an instruction operand, such as \$r[rs1] in the SPARC's add instruction. When an instruction that refers to locations within a register-like space occurs more than once in a program, each instance may refer to different locations in that space. However, which cell is being referred to is specified only by the operands of the instruction, and cannot be influenced by machine state.

- A memory-like space is one that is neither a fixed nor a register-like space and whose constituent cells are indexed by expressions with values bound either at specification time, instruction-creation time, or run time. As such, locations within a memory-like space will usually depend upon the state of the machine at the time the instruction is executed. Thus, in the SPARC load instruction, \$r[rd] := \$m[\$r[rs1] + \$r[rs2]], the value of the address expression, \$r[rs1] + \$r[rs2], is bound at run time, and hence the specific location in m-space being fetched from for a specific instance of this instruction depends upon the machine state (specifically, the values in \$r[rs1] and \$r[rs2]). Thus, an instruction that refers to cells in a memory-like space may refer to different cells on different executions of the same instance of the instruction, depending on the machine state. Such a situation would arise, for example, when using a

Figure 3.1: Relationship between index expressions' binding times and space categorization

pointer to iteratively access the elements of an array.

We can place a given space, s, into one of these three categories by examining the individual occurrences of locations in s within an instruction set. If there is at least one mention of s in which the value of the index expression is bound at run time, then s is a memory-like space. If this is not the case and there is at least one mention of x in which the value of the index expression is bound at instruction-creation time, then s is a register-like space. Otherwise, it must be that every mention of s has the value of the index expression bound at specification time, and thus s is a fixed space. More concisely, we consider the *latest* binding time of all expressions that index cells in s. The relation between this binding time and a space categorization is shown in Figure 3.1.

#### 3.3 Spaces: Implementation

The implementation of this analysis is straightforward. We examine the RTLs for the entire instruction set. In particular, we survey all of the locations mentioned within the instruction set. When we find an occurrence of a location in space s, we perform the following steps:

Determine the binding time of the indexing expression. This is done in a manner consistent with the analysis presented above, via induction on the structure of the expression (see Figure 2.1). Constants—with values determined by the instruction itself—are bound at specification time. Instructions' operands are known when a

particular instance of an instruction is created, and hence are instruction-creation time expressions. Values fetched from locations are bound at run time. When an expression results from applying an operator to other expressions, its binding time is the latest binding time of its constituent expressions.

Update our categorization of s. Based on the binding time of the indexing expression, we can make a temporary categorization of s according to the correspondence in Figure 3.1. If we have already placed s into a category, we take the more conservative of the two categories. For example, if we have currently noted that s is a fixed space, and we find an RTL that contains a location in s with an index bound at instruction-creation time, then we update our conclusions to indicate that s is a register-like space. A memory-like space is more conservative than a register-like space, which in turn is more conservative than a fixed space.

We implemented this analysis and ran it on several machines' λ-RTL descriptions. For the SPARC, the analysis correctly showed that both the r-space (integer registers) and f-space (floating-point registers) are register-like spaces. The m-space (main memory) was classified as memory-like, as was the fictitious w-space used in the machine description to model the SPARC's register windows. The SPARC spaces representing integer and floating-point control and status registers were determined to be fixed spaces. The MIPS analysis is similar, and also correctly concludes that the p-space—the system control coprocessor registers—is register-like. On the Tiny Machine, we determined that m-space is memory-like while r-space is register like.

### 3.4 Location Sets: Analysis

Above, we note that not all register sets are equivalent. For example, registers in the SPARC's **r**-space are intended to hold integer data, while those in **f**-space are intended to hold floating-point values. From this, we concluded that we need different classes of temporaries for these different spaces.

This conclusion, however, is insufficient. By itself, it assumes that locations within a particular space are interchangeable. This is not always the case. For example, fetches from integer register zero—\$r[0]—on the SPARC always return zero. Furthermore, values cannot be stored into register zero. Because of this behavior, \$r[0]

is not interchangeable with the other integer registers, r[x] where  $x \neq 0$ . Therefore, it would be a mistake to create an infinite class of temporaries in which any of the temporary locations might stand for either r[0] or r[x] where  $x \neq 0$ . Rather than have a class of temporaries associated with all of r-space, we would want a class of temporaries associated with the registers specified by r[x] where  $x \neq 0$ .

We refer to such a class of interchangeable locations as a location set. Two locations l1 and l2 are 'equivalent in instruction i' if and only if there exist two instances of  $i, i_1$  and  $i_2$ , (created by applying i to different operands) such that the RTL semantics of  $i_2$  differs from the semantics of  $i_1$  only in that l1 is replaced by l2 everywhere. To preclude vacuous relationships, we also require that  $l_1$  be present in  $i_1$ . This relation is clearly reflexive and symmetric. Given three locations l1, l2, and l3 such that l1and l2 are equivalent in i and l2 and l3 are equivalent in i, we see that substituting l1with l2 and then l2 with l3 does not change an instance's RTL semantics, and hence l1and l3 are equivalent in i. Thus, this is an equivalence relation. Consider the SPARC add instruction, r[rd] := r[rs1] + r[rs2]. Registers r[3] and r[18] are equivalent in the add instruction. Considering two instances of add in which rs1 = 3 and in which rs1 = 18 (and in which rs2 and rd are left unchanged), the only difference in the instances' semantics is the substitution of \$r[18] for \$r[3]. On the other hand, \$r[3] and \$r[0] are not equivalent in add. Because a value fetched from \$r[0] is always zero, the semantics change when we replace \$r[3] with \$r[0]. Also, \$r[3] is not equivalent to \$f[8] in add, as there is no instance of add that replaces an integer register with a floating-point register.

We now formally define a location set. A location set is a set of locations that are equivalent in one or more instructions. Consider again the SPARC's add instruction. Following the argument above, all locations within the set r[rs1] where  $rs1 \neq 0$  are equivalent to one another in add, and hence rs1 where  $rs1 \neq 0$  is a location set. Conversely, r[x] where x = 0 (or better, r[0]) forms a singleton location set of its own. On an actual machine, many instructions define the same location sets.

As with the space analysis above, we separate location sets into fixed, register-like, and memory-like categories, as follows:

• A fixed location set is a singleton location set. The location within this set is specified directly by one or more instructions, and hence there are no other

locations on the machine that would be interchangeable with it in those instructions. All of the SPARC's instructions that manipulate condition codes refer directly to the integer-unit status/control register \$i[0], where the condition codes are stored. No other location can substitute for the role \$i[0] plays in these instructions, and hence \$i[0] is a fixed location set. As noted above, \$r[0] is another fixed location set, due to its unique semantics.

- A register-like location set consists of a subset of locations within a register-like space. On the SPARC, \$r[x] where x ≠ 0 is an example of a register-like location set. Unlike this example, a register-like location set may be an entire register-like space. The SPARC floating-point register zero does not share the unique semantics of integer register zero, and as such \$f[x] (all locations in f-space) constitutes a register-like location set.

- A memory-like location set consists of some set of locations within a memory-like space of a given width. For example, the 32-bit values within m-space form a memory-like location set on the SPARC. As with register-like location sets, a memory-like location set may correspond to an entire memory-like space. Alternatively, a memory-like location set may correspond to a proper subset of a memory-like space according to, for example, alignment requirements.

In a larger sense, a location on a machine is a place into which values can be put and out of which values can be taken. In this sense, a location is a read-write container for values. As we have seen, a location set is nothing more than a set of locations treated homogeneously by some group of instructions on a target architecture. We would like to extend this abstract idea of a location to value containers that are either read-only or write-only. But to what exactly would such odd notions of a location correspond?

A read-only location is nothing more than a constant.<sup>5</sup> We can get a value from a constant (the constant itself), but we cannot change the value stored 'in' a constant. How do we group constants into location sets? Machine instructions specify constants of particular widths, such as the 13-bit constant used by the SPARC's add instruction,

<sup>&</sup>lt;sup>5</sup>When we talk of constants here, we speak of values fixed *either* at specification time (constants) or at instruction-creation time (instruction operands).

r[rd] := r[rs1] + simm13. In this position, we can use any 13-bit constant interchangeably, but we cannot use, say, a 22-bit constant. Hence, we discriminate between read-only location sets based on width: 13-bit constants might comprise one location set while 22-bit constants would make up a different location set. We refer to the location set consisting of constants of width #U bits as conU.

We also include sign-extended and zero-extended constants as read-only location sets. In fact, simm13 above is really a 13-bit constant sign-extended to 32 bits. This location set represents all 32-bit constants that can fit within 13 bits. In general, the read-only location set consisting of constants zero- or sign-extended from n to w bits represents those w-bit values that can fit in n-bits.

Figure 2.1 tells us that an expression in a machine instruction that does not contain any operators is either a constant, an instruction operand, or a value fetched from a location. We now observe that any such expression can be classified as either a read-write or a read-only location set.

If a constant may be thought of as a read-only location, what might correspond to a write-only location? By our abstraction above, such a location is a container into which we can place values, but from which we cannot retrieve values. We have seen that memory-like expressions are addressed by arbitrary expressions (depending on the addressing mode). The SPARC can refer to memory locations via register-register addressing: \$m[\$r[rs1] + \$r[rs2]] or via base-displacement addressing: \$m[\$r[rs1] + simm13]. If we consider the expressions used to address m-space in this example, we would like to think of the addressing expressions as containers into which we can place arbitrary values (namely an address). We need this ability, for example, to translate code involving arbitrary pointer arithmetic. However, once we have gotten a value into an addressing expression, the value is used to address the memory-like space, and for nothing else. That is, the concept of reading a value out of an addressing expression is meaningless. Addressing expressions, then, fit our abstraction of write-only locations.<sup>6</sup>

We extend these write-only locations to write-only location sets by observing which

<sup>&</sup>lt;sup>6</sup>An alternative view notes that constants are read-only in the sense that we can move arbitrary values from a constant into read-write (actual hardware) locations, while we cannot move arbitrary values stored in read-write locations 'into' constants. Similarly, we want the ability to 'move' arbitrary addresses stored in read-write locations into the form of an addressing expression, but once we have an addressing expression we have no need to move that value into a read-write location.

addressing expressions may be used to refer to memory in a given instruction. The SPARC st instruction has the following two forms:

```

m[r[rs1] + r[rs2]] = r[rd]

m[r[rs1] + simm13] = r[rd]

```

As either of these two addressing expressions can be used interchangeably within this instruction, we would create a write-only location set containing the elements r[rs1] + r[rs2] and r[rs1] + simm13.

The concept of these location sets is a refinement and expansion of the space classification discussed above. It is worth noting, however, that fixed location sets may occur within register-like spaces. For example, on the SPARC \$r[0] is a fixed location set within a register-like space, due to its unique semantics already discussed. Furthermore, the SPARC's call instruction writes its own address into \$r[7]. Because no other location can take this role, \$r[7] is a fixed location set.

### 3.5 Location Sets: Implementation

Identifying the location sets present within an instruction set is straightforward. Location sets can be determined directly by a completely localized inspection of an RTL. Our interest in these location sets, then, comes from the fact that the same location sets occur time and time again throughout an instruction set. We will use these location sets for much of our analysis below.

Thus, to identify the various classes of temporary locations that we need, we iterate through all of the instructions in a target architecture and identify all of the register-like location sets. We associate each such location set that we find with a new class of temporaries, and we pass this mapping along to the rest of our work. In the next chapter, we will use the ideas developed here to assign temporary locations to variables and to discover how to move values between location sets. In Chapter 5, we will see that each read-write location set corresponds to a non-terminal in the Burg rules we create.

<sup>&</sup>lt;sup>7</sup>This example also demonstrates that location sets need not be disjoint. For most instructions, r[7] is interchangeable with the other integer registers (except for r[0]) and hence r[7] is a member of the location set r[x] where  $x \neq 0$ . For the call instruction, r[7] is unique, and hence it also comprises (on its own) a fixed location set.

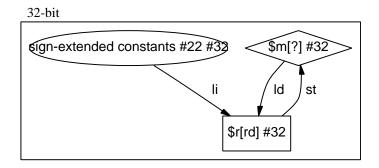

On the Tiny Machine we discover four location sets. First, we have the read-only location set that consists of constants sign-extended from #22 bits to #32 bits. Next, we have the register-like location set that consists of all locations within r-space. Unlike on the SPARC, on the Tiny Machine register zero is no different than the other registers, and hence they all form a single location set. The other read-write location set we discover on the Tiny Machine is all 32-bit locations within m-space. Finally, our location set analysis discovers the single write-only location set \$r[rs1] + con18. From these conclusions, we need only create one class of temporaries to correspond to our only register-like location set. We call this temporary space t-space.

This entire analysis can be performed at compile-compile time; all of the necessary information can be gleaned directly from a machine's  $\lambda$ -RTL semantic description.

# Chapter 4

# Choosing Locations for Variables

#### 4.1 Motivation

Before selecting instructions, a compiler must decide where to store variables that appear in a source procedure. There are two main choices. The compiler can decide either to store variables on the stack or else to store variables in registers. In the former case, the variables are stored on the stack before our code generator ever sees the code, and we need not take further action. In the latter case, it is our responsibility to decide in which registers to store each variable. Of course, as per our discussion in the previous chapter, we actually wish to assign each variable to a location in a temporary space associated with a register-like location set. Once the variables have been replaced by temporaries, the code expander can begin instruction selection. If at any time more temporaries in a given class are live than there are registers associated with that class, the register allocator will insert the appropriate spills to and loads from memory.

The goal of this analysis is to store each variable in a register-like location set most appropriate to that variable's usage within a procedure. Thus, if a machine provides both integer and floating-point registers, and a variable y is used primarily for floating-point computations, then it will be most efficient for y to be stored in a floating-point register. If y were stored in an integer register, its value would most likely have to be moved into a floating-point register every time it was used in a computation. The Motorola 68000 provides both data and address registers. We

would rather store a pointer in an address register, while a normal integer variable would be better stored in a data register.

We seek in this section a simple method to determine where to store variables. Our goal here is to present an algorithm that works reasonably well, while avoiding extra complexity. In particular, we do not attempt to split variables' live ranges between multiple locations.

#### 4.2 Analysis

We need to determine 'how' each variable is used within a procedure—but what exactly does this mean? For the most part, variables are used either as operands to an operator or to store the result of an operation.<sup>1</sup>

It will be useful in the following discussion to have some notation available for referring to results and operands of a given operator. We let  $op_n$  refer to the result of operator op if n = 0, and to the nth operand of op otherwise. Thus in the RTL x := y + 3 we have  $+_0 = x$ ,  $+_1 = y$ , and  $+_2 = 3$ . We refer to such a combination of operator and position as, logically enough, an operator position.

By examining the target machine's instruction set, we can determine from which location sets every operator takes its operands and places its results. That is, an instruction set might provide an instruction with an add operator that takes its operands from integer registers. If a procedure then contains a variable that is used only as an operand to the add operator, we would want to store that variable in an integer registers.

Of course, the situation is more complex than that; variables will most likely be used with various operators, and those operators may very well be used with different location sets throughout the instruction set. In these cases, we need to determine which location set will be cheapest for a given variable. We would like the cheapest location set to be a register-like location set, as it is for the register-like location sets that we have created temporary classes, and it is registers over which the compiler has the most control. However, there are cases in which it may be cheapest to store

$<sup>^{1}\</sup>mathrm{A}$  variable can also be the entire right-hand side of an assignment as in x := y. But all 'interesting' variable uses are as part of a computation.

4.2. ANALYSIS 33

a given variable in a fixed location set. For example, a 1-bit variable representing the carry bit in an explicit implementation of multiprecision arithmetic might be most efficiently stored within the carry bit of a machine's condition codes.

In order to find the cheapest location set for each variable, we estimate a *cost* for storing a given variable in every fixed or register-like location set for each instruction in which the variable occurs. We estimate the total cost for storing a variable in a given location set by summing the per-occurrence costs of storing the variable in that location set.

The question then becomes: how do we estimate these local costs? Each occurrence of a variable is in a specific operator position. By examining the target machine's instruction set, we can find all location sets that occur in that operator position. For this particular occurrence of this variable, these location sets would be cheapest. We can compute the cost (for this occurrence) of storing the variable in other location sets by finding the cheapest way to move a value from these other location sets into location sets that occur in this operator position within the instruction set. This is, of course, no more than an extremely rough approximation to a true cost of storing a variable in candidate locations.

Such an analysis—made more precise below—views every variable in a procedure independently of the other variables in a procedure. One could imagine a hypothetical machine setup in which choosing the optimal storage for one variable relied on using instructions that made other variables' storage choices extremely costly. Whether or not this is an issue to worry about is an experimental question that has not been taken up in the context of this paper. We hope that the simple analysis we present here is sufficient. If future experimental evidence indicates otherwise, a more complex analysis—such as one that allows for splitting a variable's live range between multiple locations—could easily be substituted.

The variable analysis we have described motivates a more general analysis: how can we move values between location sets, or even between locations within a single location set? By examining the instruction set, we can identify those instructions that do nothing more than move a value between location sets. For example, the 1d instruction on the SPARC moves a value from memory into the register-like location set r[x] where  $x \neq 0$ . By identifying data-movement instructions, we can construct

a data-movement graph in which the nodes are location sets and the edges represent instructions that move values between location sets. The edges in the transitive closure of this graph represent all pairs of location sets (l1, l2) for which there is some sequence of instructions to move a value from l1 into l2. Furthermore, finding the cheapest way to move a value between any two location sets is nothing more than a shortest-path calculation.

### 4.3 Implementation

We discuss the implementation of the analyses above for two reasons. First, it formalizes the procedures presented. Second, and equally important, it allows us to determine which aspects of the procedures can be conducted at compile-compile time, and which portions can be accomplished only at compile time.

The implementation begins by examining all of the RTLs associated within a given procedure, searching for variables used as the operands or results of operators. When a variable is found in a certain operator position  $op_n$ , we search for all read-write location sets l, such that there is an instruction in which  $op_n = l$ . For example, if we are examining variable x within the source RTL y := 8 + x, then we search for all instructions in which  $+_2$  is a read-write location set. On the SPARC, one such location set would be r[rs2] where  $rs2 \neq 0$  from the r[rd] := r[rs1] + r[rs2] version of the add instruction. However, we would not include simm13 from the r[rd] := r[rs1] + simm13 version of the add instruction, since a signed-immediate 13-bit constant is a read-only location set.

Given a variable x in operator position  $op_n$ , the search above identifies a set L such that for every location set  $l \in L$  there is an instruction that directly uses l in  $op_n$ . However, because x may appear in other operator positions that do not share the same L, we actually want to determine, for every source RTL in which x appears, the cost of storing x in any (read-write) location set. To accomplish this, we must know the cost of moving values between location sets. Given a function  $c(l_1, l_2)$  which returns the cost of moving a value from location set  $l_1$  to location set  $l_2$ , we can write the cost function for storing a variable x at operator position  $op_n$  in a particular

location set l as:

$$cost_l(x, op_n) = \frac{1}{vars(op)} + \begin{cases} 0 & \text{if } l \in L \\ \min_{l' \in L} c(l, l') & \text{otherwise} \end{cases}$$

where, as above,  $L = \{l : op_n = l \text{ for some instruction on the target machine}\}$ . Also, we define vars(op) to be the number of variables that appear in the source RTL that we are currently examining.

The term  $\frac{1}{vars(op)}$  ensures that if every variable in the source RTL is placed in a location in L, then the total cost for this source instruction will be 1. For example, if we examine the source RTL z:=x+y while compiling for the SPARC, then placing each of the variables into an integer register would give this instruction a total cost of  $\frac{1}{3} + \frac{1}{3} + \frac{1}{3} = 1$ . We justify this arrangement more below.

Every time we encounter a variable as we iterate through a procedure's RTLs, we calculate the cost of storing it in every fixed or register-like location set using the cost function above. Before summing up these local costs for a given variable, we must take into consideration the fact that not all source RTLs will be executed with the same frequency. An instruction within a loop, for instance, should be weighted more heavily than an instruction that will only be executed once. Thus, we scale the costs per variable occurrence by the estimated frequency of execution of the source RTL, a value provided by a compile-time analysis that is beyond the scope of this thesis. Taking into account this weighting, the presence of the  $\frac{1}{vars(op)}$  term above means that if every variable in a procedure is placed in an optimal location, the total cost that our analysis yields is equal to the estimate of the total number of source instructions executed in the procedure.

Once we finish examining every RTL within the procedure, we can easily assign variables to location sets. For each variable, the appropriate location set is the one for which our analysis yields the smallest cost. We use a simple allocator to assign each variable to a specific temporary within the class of temporaries associated with this location set (see previous chapter).

We cannot expect that every variable will be stored most cheaply within a registerlike location set. In particular, most architectures provide multiply, divide, and/or add with carry instructions that insist on using fixed locations. On the SPARC, for example, the high 32-bits of the product of a multiplication is placed within the fixed Y register, \$i[3]. The carry bit from an addition also almost always has a fixed location within the condition codes. Our analysis would likely find that variables used largely for such purposes can be stored most cheaply in the fixed locations themselves.

However, we would rather not deal with such fixed locations in our code generator. Instead, when we find that a variable should be stored within a fixed location, we create a new class of temporaries associated with the singleton set containing only this one location. By doing this, we defer handling the fixed location to the register allocator, which will spill and reload the fixed location as necessary. We note that spills are very likely in this situation, as every temporary within this new class maps to the same hardware location. It may be worthwhile to add an artificial cost for storing a variable in any fixed location set to represent a spill/reload penalty. Whether such a cost is necessary and what value it should have is an experimental question beyond the scope of this paper. We refer to the process of creating a new temporary class to correspond to a fixed location set as *promoting* the fixed location set.

How, then, do we implement the cost function,  $c(l_1, l_2)$ ? As discussed above,  $c(l_1, l_2)$  is the shortest-path from  $l_1$  to  $l_2$  in the graph of data-movement instructions. Recalling the general form of an RTL,

$$g_1 \to l_1 := e_1 \mid g_2 \to l_2 := e_2 \mid \dots \mid g_n \to l_n := e_n$$

a data-movement instruction can be identified as any RTL in which n = 1 (there is only a single effect),  $g_1 = \text{true}$  (the effect is not predicated on a run-time condition), and  $e_1$  does not contain any operators. Here we take advantage of the fact that any expression without an operator can be classified as either a read-write or read-only location set (see Section 3.4).<sup>3</sup>

From here it is a straightforward process to examine a full instruction set and create a data-movement graph. We use the Floyd-Warshall all-pairs shortest-paths algorithm (Cormen, Leiserson, and Rivest 1990) to create the transitive closure of the data-movement graph in which the edges are weighted with the lengths of the

<sup>&</sup>lt;sup>2</sup>This solution is still not entirely satisfactory. We would like these fixed locations to be spilled to registers rather than memory, if possible.

<sup>&</sup>lt;sup>3</sup>Actually, instructions that do not fit this form can also (in some cases) be used as data-movement instructions. On the SPARC, the instruction \$r[rd] := \$r[rs1] + simm13 can be used to move values between registers when simm13 is equal to 0. We discover this and other more complex data-movement possibilities using the techniques presented in the next chapter.

shortest paths from the original graph. We call this second graph the cost graph. Both the data-movement graph and the cost graph do not depend on any information beyond the  $\lambda$ -RTL description of the instruction set, and hence they can be created at compile-compile time. Once we have created the cost graph, the cost function c, from above, can be read directly from the graph.

We have implemented the analysis to produce the data-movement and cost graphs from a  $\lambda$ -RTL machine description. We use the publicly available graphing program dot (Koutsofios and North 1996) to draw portions of these graphs. Figures 4.1 and 4.2 show part of the data-movement graph and cost graph produced by our analysis of the SPARC's  $\lambda$ -RTL semantics. Specifically, they show the subgraphs that consist solely of 32-bit register-like and memory-like location sets. The full graph, containing location sets of other sizes as well as fixed location sets, constants, and addressing expressions, is much larger. Each edge of the data-movement graph is labeled with the instructions that perform the associated data movement, while the edges of the cost graph are labeled with the associated values of the  $c(\cdot, \cdot)$  function.

The lack of a self-loop on the vertex \$r[rs1] where ne(rs1, 0) seems an obvious omission from the data-movement graph. However, our analysis here finds only those instructions whose sole effect is to move a value between locations. On the SPARC, there is no instruction with the sole effect of moving a value from one integer register to another, and instead a value is moved between two integer registers by using an or instruction in which one of the operands is zero. We present techniques to discover such non-obvious move instructions in the next chapter.

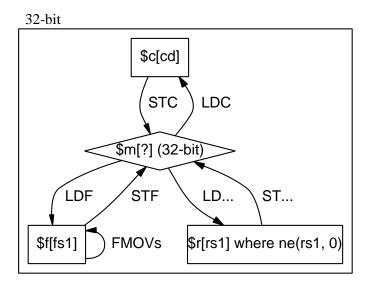

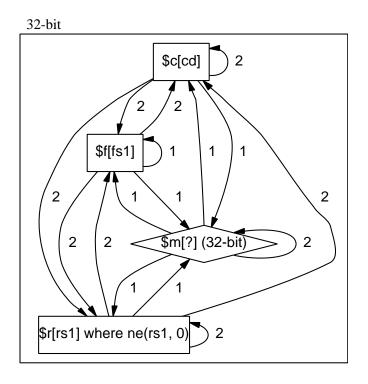

We also include the connected portion of the Tiny Machine's data-movement graph (excluding the unconnected write-only location set \$r[rs1] + con18) as Figure 4.3.

We have not yet implemented the compile-time variable analysis outlined in this chapter. Armed with our temporary classes and the data-movement graph, however (both of which are implemented), the rest of the variable analysis is machine-independent, and hence need only be directly implemented, rather than derived from a  $\lambda$ -RTL description. This direct implementation would, however, refer to the derived data-movement graph for cost information while examining each variable.

Figure 4.1: Part of the SPARC's data-movement graph. There is no self-loop on the vertex **\$r[rs1]** where ne(rs1, 0) because the SPARC does not contain an instruction whose sole effect is to move a value between integer registers. We present techniques to remedy this in the next chapter.

Figure 4.2: Part of the SPARC's cost graph

Figure 4.3: The Tiny Machine's data-movement graph.

```

# create a new stack frame by adjusting the stack pointer r[15] := r[15] - 20;

# retrieve parameters into variables r[15] := r[15] + 0;

y1 := r[15] := r[15] + 4;

x2 := r[15] := r[15] + 8;

y2 := r[15] := r[15] + 12;

# compute and return the appropriate value r[15] := r[15] + 16 := r[15] := r[15] + r

```

Figure 4.4: RTLs with variables produced from the C code in Figure 1.2 on page 11

# 4.4 Choosing Variables' Locations on the Tiny Machine

We now return to the C procedure from Figure 1.2 that we wish to translate for the Tiny Machine. Figure 4.4 shows the RTLs that a compiler front end might produce for this procedure. They add little to the procedure itself beyond a stack frame and several RTLs to move the procedure's parameters from the stack into local variables. We also assume that the result of the procedure is returned via the stack.

Using the compile-time variable analysis given in this chapter, we would estimate a cost of storing x1, y1, x2, and y2 in every register-like location set. Because the Tiny Machine only has one such location set—\$r[x]—all the variables are placed in the corresponding temporary class. Figure 4.5 shows what the RTLs for this procedure would look like once the variables have been replaced with temporaries.

```

# create a new stack frame by adjusting the stack pointer r[15] := r[15] - 20;

# retrieve parameters into variables t[0] := m[r[15] + 0];

t[1] := m[r[15] + 4];

t[2] := m[r[15] + 8];

t[3] := m[r[15] + 12];

# compute and return the appropriate value m[r[15] + 20] := (t[0] - t[2]) + (t[1] - t[3]);

```

Figure 4.5: RTLs with temporaries produced from the C code in Figure 1.2 on page 11

# Chapter 5

## From RTL to Machine Code

#### 5.1 Motivation

The code expander runs after temporary locations have been assigned to variables. It is charged with finding a sequence of machine instructions that implement an arbitrary program statement. More formally, the code expander takes as input an arbitrary source RTL and outputs a sequence of RTLs such that the execution of the sequence has the same observable effect as the execution of the original RTL and each RTL in the list can be represented by an instruction on the target machine. As we have mentioned with vpo, we call this latter property the machine invariant (Benitez and Davidson 1988).

We desire also to classify at compile-compile time the set of RTLs that our code expander is able to translate. Such a categorization is crucial to compiler authors writing a mapping from their intermediate representation to RTLs. If such an author ensures that the RTLs generated by his front end all fall within our set of translatable RTLs, then we guarantee to the author that those RTLs will be successfully compiled to machine instructions.

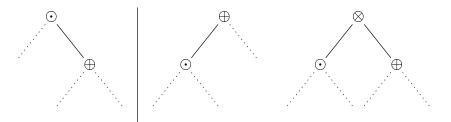

To generate code, we must know something about the semantics of the operators involved. To know that we must use the SPARC's orn instruction  $r[rd] := r[rs1] \lor \neg r[rs2]$  with r[rs1] = 0 in order to perform bitwise-complement, we either must have this particular knowledge about this instruction, or else we must know that  $0 \lor x = x$ . The first requires a priori machine-dependent knowledge. The

second is a universal truth. Thus we approach instruction selection by investigating the properties of operators' semantics, independent of any particular machine. By applying this knowledge to a particular machine, we glean the machine-specific knowledge we need to generate code.

### 5.2 Analysis

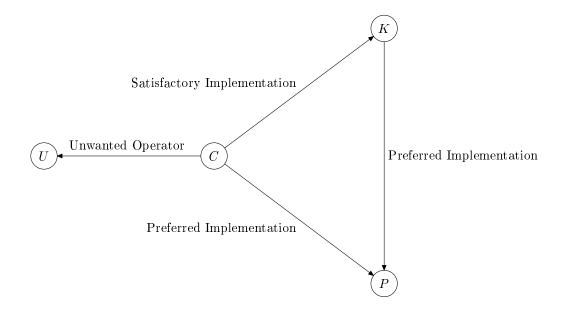

Following our analysis in the last chapter, we now must deal with the challenge of translating source RTLs with no variables into sequences of machine instructions. This challenge boils down to being able to move the result of an arbitrary computation into any arbitrary location on the machine. Our framework here does not deal with either guards or simultaneous effects. We have not taken up either of these issues within this paper, although we do address them briefly in Chapter 7.

As we develop techniques for translating code, we wish to have a framework for proving which computations we are able to translate. We approach this goal via structural induction over an RTL, with the aim of proving:

We can get the result of any computation into any location of the appropriate size.

Instrumental in establishing this result is the data-movement graph discussed in Section 4.2. If we determine that we can get a certain value into a location within location set l, then the data-movement graph immediately tells us that we can get that value into any location within any location set reachable from l in the data-movement graph.

Ideally, we would like the set of read-write location sets within the data-movement graph to be strongly connected.<sup>1</sup> This would indicate that we have a way to move a value from any machine location to any other machine location. Additionally, we would want every read-only location set to contain an edge to at least one read-write location set, indicating that we can move constant values into any location in the machine. Finally, we would want every write-only location set to have an incoming edge from at least one read-write location set, indicating that we can use values stored