## AlGaN/GaN MOSHEMT on Si Substrate with High on/off Ratio and High Off-state Breakdown Voltage Enabled by Atomic Layer Epitaxial MgCaO as Gate Dielectric

#### Citation

Zhou, Hong; Lou, Xiabing; Chabak, Kelson D.; Gordon, R.G.; Ye, Peide D. 2015. AlGaN/GaN MOSHEMT on Si Substrate with High on/off Ratio and High Off-state Breakdown Voltage Enabled by Atomic Layer Epitaxial MgCaO as Gate Dielectric. 46th IEEE Semiconductor Interface Specialists Conference, Arlington, VA, December 2-5, 2015.

#### Permanent link

http://nrs.harvard.edu/urn-3:HUL.InstRepos:29003619

### Terms of Use

This article was downloaded from Harvard University's DASH repository, and is made available under the terms and conditions applicable to Open Access Policy Articles, as set forth at http://nrs.harvard.edu/urn-3:HUL.InstRepos:dash.current.terms-of-use#OAP

# **Share Your Story**

The Harvard community has made this article openly available. Please share how this access benefits you. <u>Submit a story</u>.

**Accessibility**

#### AlGaN/GaN MOSHEMT on Si Substrate with High on/off Ratio and High Off-state Breakdown Voltage Enabled by Atomic Layer Epitaxial MgCaO as Gate Dielectric

Hong Zhou<sup>1</sup>, Xiabing Lou<sup>2</sup>, Kelson D. Chabak<sup>3</sup>, R. G. Gordon<sup>2</sup>, and Peide D. Ye<sup>1\*</sup>

<sup>1)</sup> School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47906, U.S.A

<sup>2)</sup> Department of Chemistry and Chemical Biology, Harvard University, Cambridge, MA 02138, U.S.A.

<sup>3)</sup> Air Force Research Laboratory, Sensors Directorate, Wright-Patterson AFB, OH 45433, U.S.A. \*Tel: 1-765-494-7611, Fax: 1-765-496-7443, Email: yep@purdue.edu

AlGaN/GaN high-electron-mobility-transistors (HEMTs) on Si substrates have attracted more and more attention in the area of high voltage power switches due to their lower-cost substrates, large substrate diameters and their ability to integrate with silicon processes [1-3]. Conventional Schottky gate HEMTs suffer from relatively high gate leakage currents which limit maximum forward gate bias swing and off-state performance. Metal-oxide-semiconductor HEMTs (MOSHEMTs) are proposed with a thin oxide layer in between gate and barrier to solve the aforementioned problems [4]. A good oxide must have a sufficiently large barrier height and high interface quality. In this work, we incorporate epitaxial  $Mg_{0.25}Ca_{0.75}O$  gate dielectric deposited by atomic layer deposition (ALD) into the GaN MOSHEMT process yielding improved device performance.

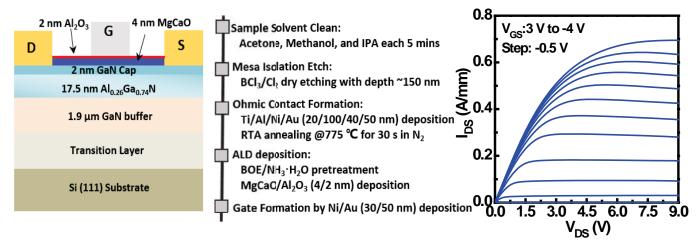

Fig. 1 shows schematic view of an AlGaN/GaN MOSHEMT on a Si (111) substrate with sheet resistance  $(R_{sh}) \sim 450 \ \Omega/\Box$ . Device fabrication started with mesa isolation by Cl<sub>2</sub>/BCl<sub>3</sub> etching to a depth of 150 nm. Then, Ohmic contacts were formed by depositing Ti/Al/Ni/Au (20/100/40/50 nm) followed by 775 °C rapid thermal anneal in N<sub>2</sub> atmosphere, yielding a contact resistance (R<sub>c</sub>) of 0.35  $\Omega$ ·mm. A 4 nm epitaxial Mg<sub>0.25</sub>Ca<sub>0.75</sub>O dielectric capped with 2 nm of amorphous Al<sub>2</sub>O<sub>3</sub> was then deposited by ALD. The growth temperature of MgCaO was 310 °C, using bis(*N*,*N*'-di-*tert*-butylacetamidinato)calcium, bis(*N*,*N*'-di-*sec*-butylacetamidinato) magnesium, and water vapor as precursors [5]. Single crystalline MgCaO offers an advantageous band offset, a good interface, and good lattice matching to GaN alloys [6]. Finally, Ni/Au (30/50 nm) was deposited as the gate metal followed by a lift-off process. All of the lithography processes were carried out using a MJB3 mask aligner lithography system. Devices have a gate width (W) of 100 µm and gate length (L<sub>g</sub>) of 1, 2, 4, 8, 20, and 40 µm.

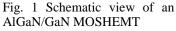

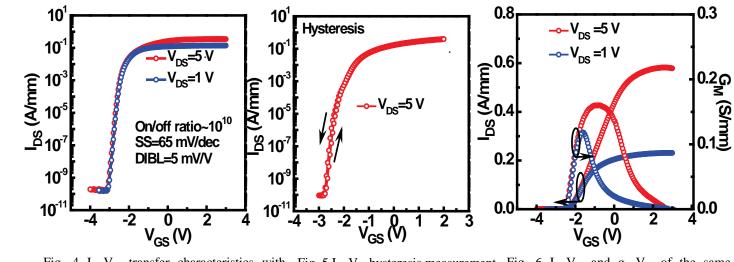

Fig. 3 shows the well-behaved DC output Ids-Vds characteristics of a GaN MOSHEMT. The device has an  $L_g=1 \mu m$  and source to drain spacing ( $L_{sd}$ ) of 4.2  $\mu m$ . Due to a 6 nm thick gate oxide, a high gate bias ( $V_{gs}$ ) of 3 V can be applied, yielding a maximum drain current  $(I_{ds,max})$  of 700 mA/mm. Fig. 4 is the  $I_{ds}$ -V<sub>gs</sub> transfer characteristic measurement of the same device. Impressively, a high on/off ratio of 1010 is achieved with subthreshold swing (SS) of 65 mV/dec at V<sub>ds</sub>=5 V. Traditional HEMT devices are not able to have such a high on/off ratio because of their large gate leakage currents in the off-state. The oxide of the MOSHEMT suppresses this leakage, yielding large on/off ratios. In addition, benefiting from the lattice matching and good interface between MgCaO and GaN,[5] the GaN MOSHEMT also demonstrates a negligible hysteresis (50 mV) as shown in Fig. 5. Fig. 6 shows the  $I_{ds}$ - $V_{gs}$  and  $g_m$ - $V_{gs}$  plot at the linear region. Peak transconductance ( $g_{m,max}$ ) of 160 mS/mm and threshold voltage ( $V_T$ ) of -2.2 V are observed at  $V_{ds}$ =5 V. The off-state breakdown/leakage characteristics of a MOSHEMT are shown in Fig.7. This device has a W/L<sub>g</sub>=100  $\mu$ m/1  $\mu$ m and L<sub>gs</sub>=L<sub>gd</sub>=1.6  $\mu$ m. The device is operated at the pinch-off region with  $V_{gs}$ =-3.5 V and  $V_s$ =0 V. It can be observed that the breakdown voltage is 150 V even with a short  $L_{gd}=1.6 \mu m$ . The breakdown voltage, which is a critical figure of merit for power switch, is expected to increase with the increase of  $L_{ed}$  and drain-gate region engineering. Scaling metrics of GaN MOSHEMTs are also studied as shown in Fig. 8 and Fig. 9. The  $I_{ds}$  and  $g_{max}$  are found to increase when the L<sub>g</sub> is scaled. SS and drain induced barrier lowering (DIBL) are found to be slightly influenced by the L<sub>g</sub>, and  $V_T$  shows roll-off behavior when  $L_g=1 \ \mu m$ .

In conclusion, we have demonstrated high performance AlGaN/GaN MOSHEMTs on Si substrate with high on/off ratio and high off-state breakdown voltage with epitaxial MgCaO gate dielectric. The lattice-matched MgCaO provides high quality interface and an appropriate electron barrier height, which makes it feasible to be applied to future GaN power switch applications.

The work at Purdue is supported by AFOSR and the work at Harvard is supported by the ONR.

**References:** [1] B. De Jaeger et al., *Proc. ISPSD*, pp. 49-52, 2012. [2] P. Moens et al., *Proc. ISPSD*, pp. 374-377, 2014. [3] N. Ikeda et al., *Proc. of the IEEE*, Vol. 98, No. 7, pp. 1151-1161, 2010. [4] P. D. Ye et al., *Appl. Phys. Lett.*, vol. 86, pp. 063561, 2005. [5] X. B. Lou et al., CSW, 2015. [6] H. Zhou et al., DRC, 2015.

Fig. 2 Device fabrication process steps of AlGaN/GaN MOSHEMTs

Fig. 3 Output characteristics of an AlGaN/GaN MOSHEMT with  $L_e=1 \mu m$  and  $L_{SD}=4.2 \mu m$ .

Fig. 4  $I_{ds}$ - $V_{gs}$  transfer characteristics with on/off ratio of 10<sup>10</sup> and low SS=65 mV/dec. Fig. 5  $I_{ds}$ - $V_{gs}$  hysteresis measurement fig. 6  $I_{ds}$ - $V_{gs}$  and  $g_m$ - $V_{gs}$  of the same device in the linear region plot.

Fig. 7 Three-terminal off-state breakdown measurement with  $L_g=1 \ \mu m$  and  $L_{gd}=1.6 \ \mu m$ .

Fig. 8  $I_{on}$  and  $G_{max}$  scaling metrics of GaN MOSHEMTs.

Fig. 9 SS, DIBL and  $V_T$  scaling metrics of GaN MOSHEMTs.