# Quantitative Evaluation of Cobalt Disilicide/Si Interfacial Roughness

# Citation

Yang, Jing, Jun Feng, Kecheng Li, Harish B. Bhandari, Zhefeng Li, and Roy G. Gordon. 2017. "Quantitative Evaluation of Cobalt Disilicide/Si Interfacial Roughness." ECS Journal of Solid State Science and Technology 6 (5): P345–P349. doi:10.1149/2.0271705jss.

# **Published Version**

10.1149/2.0271705jss

# Permanent link

http://nrs.harvard.edu/urn-3:HUL.InstRepos:32696198

# Terms of Use

This article was downloaded from Harvard University's DASH repository, and is made available under the terms and conditions applicable to Open Access Policy Articles, as set forth at http://nrs.harvard.edu/urn-3:HUL.InstRepos:dash.current.terms-of-use#0AP

# **Share Your Story**

The Harvard community has made this article openly available. Please share how this access benefits you. <u>Submit a story</u>.

**Accessibility**

# Quantitative Evaluation of Cobalt Disilicide/Si Interfacial Roughness

Jing Yang,<sup>a</sup> Jun Feng,<sup>b</sup> Kecheng Li,<sup>a</sup> Harish B. Bhandari,<sup>a,c</sup> Zhefeng Li,<sup>a,d</sup> Roy Gordon <sup>z,a,b</sup>

<sup>a</sup> John A. Paulson School of Engineering and Applied Sciences, Harvard University, Cambridge, MA 02138, USA

<sup>b</sup> Department of Chemistry & Chemical Biology, Harvard University, Cambridge, MA, 02138 USA

<sup>c</sup> Current Address: RMD - Radiation Monitoring Devices, Inc, Watertown, MA 02472

<sup>d</sup> Current Address: Applied Materials, Santa Clara, CA

#### Abstract

The formation of smooth, conformal cobalt disilicide (CoSi<sub>2</sub>) without facets or voids is critical for microelectronic device reliability owing to the ultra-shallow contact areas. Here we demonstrate the formation of smooth and conformal CoSi<sub>2</sub> films by chemical vapor deposition (CVD) of cobalt nitride (Co<sub>x</sub>N) films on silicon (Si) or on silicon on insulator (SOI) substrates, followed by in-situ rapid thermal annealing (RTA) at 700°C. To reveal the CoSi<sub>2</sub>/Si interfacial morphology, we report a back-to-front sample preparation method, in which mechanical polishing, anisotropic tetramethylammonium hydroxide (TMAH) wet etching, hydrofluoric acid (HF) wet etching, and isotropic xenon difluoride (XeF<sub>2</sub>) dry etching are employed to remove the SOI substrate from the back side to expose the CoSi<sub>2</sub>/Si interface. This method offers a robust and reliable procedure for quantitative assessment of the CoSi<sub>2</sub>/Si interfacial roughness, as well as analytical support for advanced fabrication process development.

<sup>&</sup>lt;sup>z</sup> Corresponding Author E-mail Address [gordon@chemistry.harvard.edu]

# Introduction

Metal silicides have been widely used as self-aligned contacts in silicon-based microelectronic devices for the past decades.<sup>1</sup> Among various metal silicides, CoSi<sub>2</sub> is considered as an attractive contact material because of its low resistivity (10-20  $\mu\Omega$ ·cm), no line-width dependence in narrow lines, and its superior chemical and thermal stability.<sup>2-4</sup> CoSi<sub>2</sub> has been used for various electronic devices, such as memory electrode for 3D structure<sup>5</sup> and the metallization material for nanoparticles, nanowires<sup>6, 7</sup>. As devices scale down, a thin, uniform CoSi<sub>2</sub> layer is essential for those nano-electronic applications. Otherwise, cobalt silicide spikes will cause severe junction leakage and lead to device failure.8 However, the complicated growth mechanism of CoSi2 can result in a problematic, rough CoSi<sub>2</sub>/Si interface. 9 10 The complex kinetics results from several concurrent mechanisms: nucleation, diffusion and perhaps interface reaction. <sup>11</sup> Many efforts have been focused on the formation of a smooth CoSi<sub>2</sub> interface with Si by optimizing the fabrication process. For example, a Ti capping layer was introduced to reduce interfacial roughness induced by ambient contamination.<sup>12</sup> Hence, the quantitative evaluation of the CoSi<sub>2</sub>/Si interfacial roughness is crucial for optimization of fabrication processes for CoSi<sub>2</sub>.

CoSi<sub>2</sub> is typically fabricated by annealing sputtered Co films on active source, drain and gate regions.<sup>2</sup> However, the conventional sputtering process results in poor step coverage and induces high ion damage in the active regions, making it undesirable for complex 3D architectures in modern transistors. Chemical vapor deposition (CVD) can avoid these problems by producing conformal cobalt-containing thin films without ion-induced damage.<sup>13-15</sup>

In this paper, we evaluate quantitatively the roughness of the cobalt silicide/Si interface, in which the cobalt silicide is produced from CVD-deposited Co<sub>x</sub>N by in-situ RTA at 700°C. The CVD process produced smooth, uniform and highly conformal Co<sub>x</sub>N, and also resulted in a smooth and high-quality CoSi<sub>2</sub>/Si interface.<sup>13</sup> To reveal the CoSi<sub>2</sub>/Si interface for analysis of its roughness, we adapted and modified a SIMS sample preparation technique to remove the backside of the sample. This method uses both wet-etching and dry etching to remove a SOI substrate below the CoSi<sub>2</sub>. This work provides direct quantitative assessment of cobalt silicide/Si interfacial roughness for the first time, and offers critical insights for future process optimization.

# **Experimental**

Cobalt nitride films on Si and SOI substrates were prepared by CVD using bis(*N-tert*-butyl-*N'*-ethyl-propionamidinato) cobalt(II) and a mixture of 20 sccm NH<sub>3</sub> and 40 sccm H<sub>2</sub> at 200°C. The details of this process have been described elsewhere. The Si and SOI substrates were first treated by UV-ozone and then cleaned by HF before deposition. After cleaning, the substrates were immediately placed into the reactor chamber and evacuated, to suppress oxidation of the substrates. As Co is unable to react with SiO<sub>2</sub>, the cobalt silicide formation might be slowed down or even blocked by any interfacial native oxide. Therefore, a clean substrate without native oxide is critical to obtain a uniform and smooth CoSi<sub>2</sub> films.

The as-deposited Co<sub>x</sub>N films were treated by *in-situ* RTA at elevated temperatures from 500°C to 700°C for 30 sec in purified N<sub>2</sub>. Those gases used in the deposition and annealing

processes were purified by gas purifiers (Entegris Gatekeeper) to reduce the impurities below 1 ppb for all contaminants including O<sub>2</sub>, CO, CO<sub>2</sub>, and H<sub>2</sub>O. This purification is needed because the CoSi<sub>2</sub> formation process is highly sensitive to traces of oxygen-containing impurities in the annealing ambient. Extremely low levels of these impurities are essential for smooth CoSi<sub>2</sub> formation. Indeed, attempts to form CoSi<sub>2</sub> from Co<sub>x</sub>N by ex-situ RTA were unsuccessful owing to the sample contamination during the exposure to the air and the annealing ambient (our *ex-situ* RTA tool does not use purified gas for annealing). Those impurities resulted in discontinuous CoSi<sub>2</sub> with many voids. A previous study also showed that impurities in the annealing atmosphere formed voids during silicidation. Therefore, we employed *in-situ* annealing inside our cobalt deposition system to produce consistent, continuous CoSi<sub>2</sub> films.

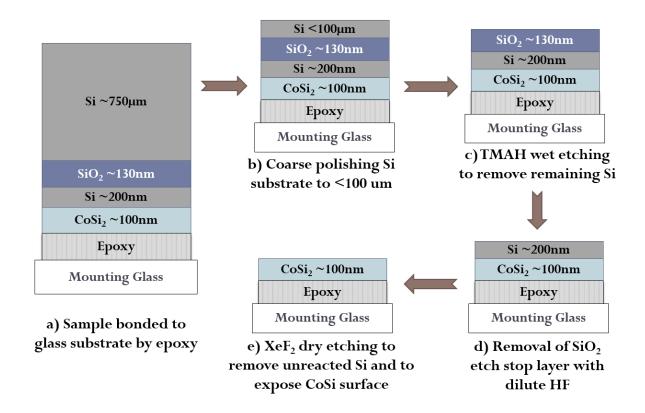

The backside sample preparation included 5 steps to reveal the CoSi<sub>2</sub>/Si interface. First, the sample was bonded upside down to a glass slide of similar size for mechanical support. Epoxy Bond 110 (Ted Pella Inc.) is used for bonding the two. Thin epoxy glue was carefully applied in between and degassed, then cured at 125°C for 10 min to obtain a homogenous glue film with good adhesion.

Second, the bonded sample stack was mounted onto a specimen mount – a cylindrical Pyrex stub (Gatan Inc.) using a low-melting-point wax (Crystalbond 509, Ted Pella Inc.). The stub was heated on a hot plate at 130°C~160°C to melt a tiny granule of wax for mounting the sample stack to be ground flat. Then a metal ring (Gatan Inc.) was used to hold the stub flat on the polishing sand paper. Rough thinning of the specimen was performed with a polisher (Allied High Tech Products Inc.) until a thickness of 100 µm or less was achieved.

The thickness of the specimen was measured and monitored by the micrometer to reach the desired thickness of less than 100 µm after polishing. The Si substrate was coarsely polished sequentially by SiC sand paper of 600 grit and 1200 grit. The polished specimen was detached from the mounting stub by melting the wax on a hot plate and dissolving the remaining wax in acetone.

Third, the remaining Si substrate was removed by a heated TMAH (25 wt%) bath at 85°C. TMAH etching is highly selective towards the thermal oxide. Thus when no more bubbles were formed in the etching solution, it indicated the bulk Si had been completely removed, exposing the SiO<sub>2</sub> layer. Then the sample was immersed in 10:1 buffered HF solution until the SiO<sub>2</sub> layer of the SOI was removed, which is the fourth step.

In the final step, the remaining Si layer (~100 nm) from SOI (originally 200 nm) was removed by dry etching with XeF<sub>2</sub> gas. This was performed in a home-built XeF<sub>2</sub> etching tool. Exposed Si was quickly etched by alternating exposure to XeF<sub>2</sub> and subsequent pumping away of gaseous reaction products. Si reacts with XeF<sub>2</sub> to form gaseous Xe and SiF<sub>4</sub>. XeF<sub>2</sub> etching has been used to selectively remove Si because it removes only silicon, but not photoresist, SiO<sub>2</sub>, silicon nitride, Al, Cr, or TiN. We measured that in our system the XeF<sub>2</sub> etch rate of CoSi<sub>2</sub> is 200 times slower than that of Si; thus XeF<sub>2</sub> etching can selectively remove the thin layer of residual Si. As a result of the excellent selectivity towards CoSi<sub>2</sub>, the XeF<sub>2</sub> etching process is highly robust and tolerant towards some over-etch. This final step leaves a clean CoSi<sub>2</sub> surface, allowing the CoSi<sub>2</sub>/Si interface to be examined by atomic force microscopy (AFM). The interfacial roughness study is valuable for optimizing cobalt silicide process.

# **Results and Discussion**

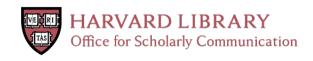

We used X-ray diffraction (XRD, Bruker D8) to study cobalt silicidation process by annealing Co<sub>x</sub>N/Si(100) structure in-situ at 500°C, 600°C and 700°C in N<sub>2</sub> for 30 sec. XRD measurements were carried out by using D8 diffractometer and 2-Dimensional detector. The as-deposited Co<sub>x</sub>N showed a face-cubic-centered (fcc) phase, as indicated by our previous study. 13 The Co<sub>x</sub>N remained stable in its fcc phase after RTA at 500°C. After RTA at 600°C, CoSi<sub>2</sub> with (111) and (220) orientations dominated the resulting films, while CoSi (210) and (211) orientations occurred simultaneously. This suggests polycrystalline CoSi<sub>2</sub> started to appear together with CoSi after annealing at 600°C. Meanwhile, the intensity of CoSi<sub>2</sub> (111) peak is greater than of other CoSi<sub>2</sub> and CoSi peaks, indicating that the film is textured. The CoSi completely transformed to CoSi<sub>2</sub> after RTA at 700°C, forming a textured CoSi<sub>2</sub> with a (111) preferred orientation on the Si (100) substrate. The cubic CoSi<sub>2</sub> and CoSi phases were formed directly from cubic CoN<sub>x</sub> films without any intermediate Co-rich phases, such as tetragonal Co<sub>2</sub>Si or orthorhombic Co<sub>3</sub>Si at low temperatures. In a conventional Co silicide process, Co-rich silicide phases such as Co<sub>2</sub>Si or CoSi generally formed at a low temperature ranging between 400 °C and 500 °C. These results indicate that because of retardation of the Co-Si reaction by the nitrogen in the Co<sub>x</sub>N film, the conversion of Co<sub>x</sub>N to CoSi<sub>2</sub> does not form any intermediate Co-rich phases. This finding agrees with a previous study of CoSi<sub>2</sub> formation by annealing Co/CoN<sub>x</sub>/Si structures. 19 Additionally, CoSi<sub>2</sub> grown by the reaction of Co<sub>x</sub>N on Si(100) produced polycrystalline CoSi<sub>2</sub> films as expected. Although CoSi<sub>2</sub> (cubic  $CaF_2$  structure with a=5.36 Å) and Si (cubic diamond structure with a=5.43 Å) have a small lattice mismatch of only 1.2 % and similar crystallographic structure, it has proved challenging to form epitaxial CoSi<sub>2</sub> on Si substrates. Bulle-Lieuwma *et al.*<sup>20</sup> explained the possible reason for the polycrystalline nature of CoSi<sub>2</sub> on Si (100). They suggested that the competition between different epitaxial orientations with similar matching resulted in the growth of polycrystalline CoSi<sub>2</sub>.

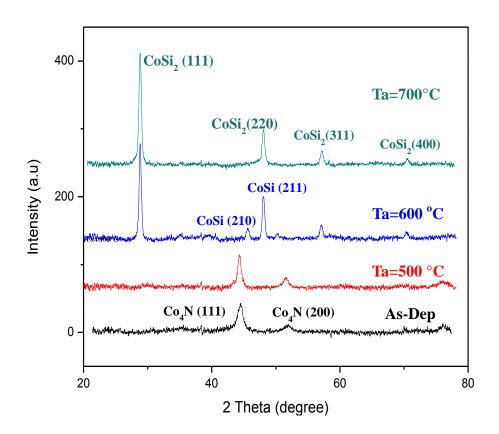

Figure 2 shows electron diffraction (ED) images of CoSi<sub>2</sub> from transmission electron microscopy (TEM; JEOL 2100 TEM system). ED shows that the films are polycrystalline cubic cobalt disilicide. The speckled pattern of the diffraction rings indicates that the specimen has relatively large grain sizes. The pattern showed part of the ring is more intense compared to the rest, indicating a textured film. This result agreed with the XRD result.

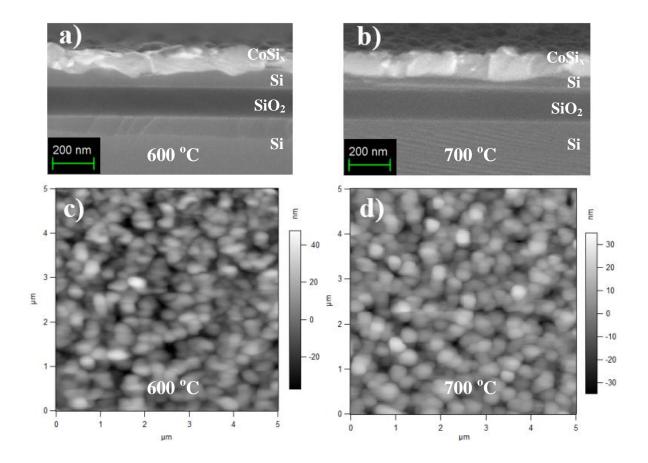

The resistivity of  $Co_xN$  and  $CoSi_2$  thin films could be obtained by measurements of the thickness and sheet resistance. A four point probe was applied to measure the sheet resistance. The unreacted cobalt nitrides (if any) on top of the formed  $CoSi_2$  were removed by a dilute sulfuric acid solution at 50 °C before the measurements. A scanning electron microscope (SEM) was used to measure the physical thicknesses. An as-deposited 30 nm  $Co_xN$  film on a Si (100) substrate generated around 120 nm of  $CoSi_2$  by in-situ annealing at 700 °C (Figure 5). The formed polycrystalline  $CoSi_2$  film was composed of grains and displayed thickness variation in the field of view as observed in SEM image (Figure 5b). The interfacial roughness between  $CoSi_2$  film and Si substrate fabricated from CVD  $Co_xN$  is similar to that from PVD Co. The resistivity of the  $Co_xN$  films decreased from 140  $\mu\Omega$ ·cm to 20  $\mu\Omega$ ·cm due to the formation of more conductive  $CoSi_2$ . This value is close to reported resistivity of  $CoSi_2$ , i.e.  $16\sim20$   $\mu\Omega$ ·cm.

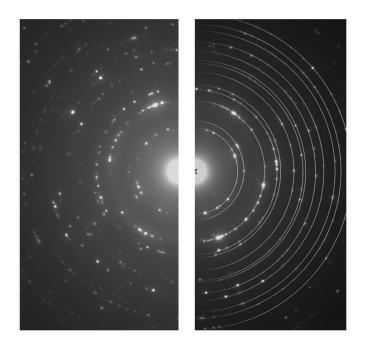

X-ray photoelectron spectroscopy (XPS) was used to measure the composition of  $CoSi_2$  films formed by annealing  $Co_xN$  on Si (100) substrates at 700°C. XPS spectra taken during argon sputtering determined the composition profiles using the Co 3p, Si 2s, C 1s, O 1s and N 1s XPS peaks. The trace of nitrogen near the surface can be attributed to a small amount of unreacted  $Co_xN$  left on the surface. Carbon and oxygen remain on the surface of the film from air exposure. The Co:Si ratio is about 1:2 inside the film. This result confirmed that we obtained cobalt disilicide with the expected stoichiometry after annealing  $Co_xN/Si$  at 700 °C.

The CoSi<sub>2</sub>/Si interfacial roughness is an important factor that affects device performance. We highlight here the backside sample preparation procedure to examine the CoSi<sub>2</sub>/Si interfacial roughness by AFM (Asylum MFP-3D AFM). The initial backside sample preparation was first proposed for SIMS sample preparation.<sup>22</sup> We adapted this method to remove the substrate and reveal the CoSi<sub>2</sub> layer of interest. The CoSi<sub>2</sub> sample was prepared by in-situ annealing Co<sub>x</sub>N/SOI at 700 °C. We selected SOI instead of Si (100) as the substrate owing to its built-in etch-stop layer (i.e. the buried oxide of an SOI wafer). The buried oxide in SOI allowed selective removal of most of the SOI substrate.<sup>22</sup> We employed a combination of mechanic polishing, wet etching, and dry etching to reveal the CoSi<sub>2</sub>/Si interface. Wet etching of Si-substrate is commonly performed using heated TMAH (tetramethylammonium hydroxide) or KOH solutions. 18 The wet etching is fast and easy to perform. However, the wet etching of thick and roughly polished remaining Si inadvertently leads to the formation of <111> faceted Si-pyramids. This formation of faceted Si-pyramids is caused by the highly anisotropic etch rates, with etch rates of <sup>3</sup> crystallographic orientation being 2-3 orders of magnitude lower than those of other major crystallographic orientations. 18 Therefore, wet

etching cannot be used as a high-precision polishing step, and an etch-stop layer is crucial for eliminating the roughness from the anisotropic wet-etching step. Alternatively, the Si dry etching using XeF<sub>2</sub> gas exhibits essentially isotropic etch rates regardless of crystallographic orientations. And XeF<sub>2</sub> dry etching has been proved to be highly selective towards CoSi<sub>2</sub>. Thus the XeF<sub>2</sub> dry etching process was applied to remove the thin Si remaining on top of CoSi<sub>2</sub>.

To reveal and analyze the CoSi<sub>2</sub>/Si interfacial morphology, we adopted a modified back-to-front sample preparation method, in which mechanical polishing, anisotropic tetramethylammonium hydroxide (TMAH) wet etching, hydrofluoric acid (HF) wet etching, and isotropic xenon difluoride (XeF<sub>2</sub>) dry etching are employed to remove the SOI substrate from the back side to expose the CoSi<sub>2</sub>/Si interface, as schematically illustrated in Figure 4. Note that for all roughness studies, "interface" is defined as the interface between CoSix and Si, while "surface" is defined as the other side of the CoSi<sub>x</sub> film. And the surface roughness was analyzed before mounting the sample upside down onto the substrate by epoxy. Based on the AFM image and rms results shown in Figure 5 and Table 1, the CoSi formed at 600°C showed a surface roughness (10.1 nm) of 9.2 % of the silicide thickness (110 nm), and the interface roughness (13.2 nm) was 12.0 % of the silicide thickness (110 nm). When Co<sub>x</sub>N/SOI was annealed at 700°C in N<sub>2</sub>, stoichiometric CoSi<sub>2</sub> was formed. The surface roughness of the resulting CoSi<sub>2</sub> was determined to be around 10.3 % (12.3 nm) of the silicide thickness (120 nm), while the interface roughness is 7.6 % (9.1 nm) of the silicide thickness (120 nm). Comparing the samples annealed at 600 °C and 700 °C, the surface roughness of CoSi<sub>x</sub>/Si did not change much while the CoSi<sub>x</sub>/Si interfacial roughness is substantially reduced after conversion of CoSi to CoSi<sub>2</sub> at  $700^{\circ}$ C. This is because CoSi<sub>2</sub> (cubic, lattice constant a= 5.36 Å) has a smaller lattice mismatch with Si (cubic, a= 5.54 Å), compared with CoSi (cubic, a= 4.45 Å).

#### **Conclusions**

We successfully evaluated the CoSi<sub>2</sub>/Si interfacial roughness quantitatively by a backside sample preparation procedure. We obtained stoichiometric cobalt disilicide, which has low interfacial roughness because of its small lattice mismatch with Si, by *in-situ* rapid thermal annealing CVD-Co<sub>x</sub>N at 700°C in N<sub>2</sub>. The backside sample preparation utilized a combination of mechanical polishing, wet etching and dry etching to expose the CoSi<sub>2</sub>/Si interface for AFM measurements. This approach provides a robust and reliable procedure to acquire quantitative morphological information about silicon-silicide interfaces, which can serve as an important assessment method for modern silicidation and metallization processes.

# Acknowledgments

The authors thank Dr. Qing Min Wang, Dr. Jean-Sebastien Lehn, Dr. Huazhi Li and Dr. Deo Shenai for helpful discussions, and for their work to synthesize the cobalt amidinate precursor used in this work at Dow Chemical Company. This work was performed in part at the Center for Nanoscale Systems (CNS) at Harvard University, a member of the National Nanotechnology Infrastructure Network (NNIN), which was supported by NSF award no. ECS-0335765.

#### References

- 1. S.-L. Zhang and M. Östling, *Critical Reviews in Solid State and Materials Sciences*, **28** (1), 1-129 (2003).

- 2. K. Maex, Materials Science and Engineering: R: Reports, 11 (2–3), vii-153 (1993).

- 3. L. Anhua, C. Jianming, D. Shaonan, Y. Yanbo, L. Ling, L. Fengping, and C. Lifu, *Journal of Materials Chemistry C*, **2** (25), 4980-4988 (2014).

- K. Bernal-Ramos, M. J. Saly, R. K. Kanjolia, and Y. J. Chabal, *Chemistry of Materials*,

27 (14), 4943-4949 (2015).

- 5. J. H. Park, S. J. Kim, J. H. Lee, C. J. Yoo, H. J. Kang, B. C. Lee, and J. G. Jeong, *ECS Journal of Solid State Science and Technology*, **5** (5), P264-P271 (2016).

- 6. P. Krogstrup, *Nat Mater*, **14** (8), 757-759 (2015).

- F. Panciera, Y. C. Chou, M. C. Reuter, D. Zakharov, E. A. Stach, S. Hofmann, and F.

M. Ross, *Nat Mater*, 14 (8), 820-825 (2015).

- 8. J. Y. Dai, Z. R. Guo, S. F. Tee, C. L. Tay, E. Er, and S. Redkar, *Applied Physics Letters*, **78** (20), 3091-3093 (2001).

- 9. M. Tsuchiaki, C. Hongo, A. Takashima, and K. Ohuchi, *Japanese Journal of Applied Physics*, **41** (Part 1, No. 4B), 2437- 2444 (2002).

- 10. K. Kim, K. Lee, S. Han, W. Jeong, and H. Jeon, *Journal of The Electrochemical Society*, **154** (3), H177-H181 (2007).

- 11. F. M. d'Heurle and C. S. Petersson, *Thin Solid Films*, **128** (3–4), 283-297 (1985).

- 12. K. Maex, A. Lauwers, P. Besser, E. Kondoh, M. de Potter, and A. Steegen, *Electron Devices, IEEE Transactions on*, **46** (7), 1545-1550 (1999).

- 13. H. B. Bhandari, J. Yang, H. Kim, Y. Lin, R. G. Gordon, Q. M. Wang, J.-S. M. Lehn, H.

- Li, and D. Shenai, ECS Journal of Solid State Science and Technology, 1 (5), N79-N84 (2012).

- 14. J. Yang, K. Li, J. Feng, and R. G. Gordon, *Journal of Materials Chemistry C*, **3** (46), 12098-12106 (2015).

- J. Feng, X. Gong, X. Lou, and R. G. Gordon, ACS Applied Materials & Interfaces, 9

(12), 10914-10920 (2017).

- 16. H. Li, G. Vereecke, K. Maex, and L. Froyen, *Journal of The Electrochemical Society*, **148** (6), G344-G354 (2001).

- 17. N.-S. Kim, C. Han-Seob, N.-K. Sung, R. Hyuk-Hyun, K.-S. Youn, and L. Won-Gyu, *Journal of Vacuum Science & Technology A: Vacuum, Surfaces, and Films*, **20** (4), 1171-1176 (2002).

- 18. G. T. A. Kovacs, N. I. Maluf, and K. E. Petersen, *Proceedings of the IEEE*, **86** (8), 1536-1551 (1998).

- 19. S. I. Kim, S. R. Lee, J. H. Park, and B. T. Ahn, *Journal of The Electrochemical Society*, **153** (5), G506-G510 (2006).

- 20. Bulle, x, C. W. T. Lieuwma, A. H. van Ommen, J. Hornstra, and C. N. A. M. Aussems, *Journal of Applied Physics*, **71** (5), 2211-2224 (1992).

- 21. C.-J. Chiou, S.-P. Chiu, J.-J. Lin, and Y.-C. Chou, *CrystEngComm*, **17** (23), 4276-4280 (2015).

- 22. M. J. P. Hopstaken, C. Cabral, D. Pfeiffer, C. Molella, and P. Ronsheim, *AIP Conference Proceedings*, **1173** (1), 94-98 (2009).

**Figure 1.** The XRD spectra of the as-deposited  $Co_xN/Si$  (100) and the films after *in-situ* annealing under 1 Torr of  $N_2$  at various temperatures ( $T_a = 500^{\circ}C$ ,  $600^{\circ}C$ ,  $700^{\circ}C$ ) for 30 s.

**Figure 2.** The electron diffraction (ED) images of  $CoSi_2$  formed by *in-situ* annealing  $Co_xN/Si(100)$  in  $N_2$  at  $700^{\circ}C$  for 30 sec.

Figure 3. XPS depth-profile study of CoSi<sub>2</sub> formed by annealing Co<sub>x</sub>N/Si (100) at 700 °C

**Figure 4.** Schematic representation of consecutive steps in backside sample preparation procedure to reveal  $CoSi_2/Si$  interface: Sample is prepared by annealing  $Co_xN$  on SOI substrate at 700 °C to form  $CoSi_2$  on SOI. (a) Sample is invert and fixed on a support glass substrate of approximately same size. (b) Sample after grinding the backside substrate with SiC sand paper (600 - 1200 grit) to reduce substrate thickness down to below 100  $\mu$ m. (c) Sample after TMAH wet etching to selectively remove the residual silicon substrate. (d) Sample after a dilute HF etching to remove the exposed buried oxide. (e) Sample after dry XeF<sub>2</sub> etching to selectively remove the residual unreacted silicon, leaving the  $CoSi_2$  surface ready for AFM measurements.

**Figure 5.** (a-b) Cross-section SEM images of silicided SOI substrates; (c-d) Measurement of  $CoSi_2/Si$  interfacial roughness by AFM.  $CoSi_2$  is produced by annealing CVD  $Co_xN$  film at 700 °C in  $N_2$ .

**Table 1.** Cobalt silicide roughness of both surface and interface at different silicidation temperatures. Note: For roughness study, "interface" is defined as the interface between  $CoSi_x$  and Si; "surface" is defined as the other side of  $CoSi_x$ , which was analyzed before mounting the sample upside down onto the substrate by epoxy.

| Annealing Temperature (°C) | Silicide<br>Thickness (nm) | Surface Roughness |            | Interface Roughness |            |

|----------------------------|----------------------------|-------------------|------------|---------------------|------------|

|                            |                            | rms (nm)          | Percentage | rms (nm)            | Percentage |

| 600                        | 110                        | 10.1              | 9.2%       | 13.2                | 12.0%      |

| 700                        | 120                        | 12.3              | 10.3%      | 9.1                 | 7.6%       |