## Chemical Vapor Deposition (CVD) of Manganese Self-Aligned Diffusion Barriers for Cu Interconnections in Microelectronics

### Citation

Gordon, Roy G., Hoon Kim, Yeung Au, Hongtao Wang, Harish B. Bhandari, Yiqun Liu, Don K. Lee and Youbo Lin. 2009. Chemical vapor deposition (CVD) of manganese self-aligned diffusion barriers for Cu interconnections in microelectronics. In Advanced Metallization Conference 2008 (AMC 2008): Proceedings of the conference: September 23-25, 2008, San Diego, California, U.S.A. and October 8-10, 2008, at the University of Tokyo, Tokyo, Japan. Materials Research Society conference proceedings. Warrendale, Pa: Materials Research Society.

## **Published Version**

http://www.mrs.org/s\_mrs/sec\_detail.asp?CID=1728&DID=241813

## Permanent link

http://nrs.harvard.edu/urn-3:HUL.InstRepos:3347575

## Terms of Use

This article was downloaded from Harvard University's DASH repository, and is made available under the terms and conditions applicable to Open Access Policy Articles, as set forth at http://nrs.harvard.edu/urn-3:HUL.InstRepos:dash.current.terms-of-use#OAP

# Share Your Story

The Harvard community has made this article openly available. Please share how this access benefits you. <u>Submit a story</u>.

<u>Accessibility</u>

## **Chemical Vapor Deposition (CVD) of Manganese Self-Aligned Diffusion Barriers for Cu Interconnections in Microelectronics**

Roy G. Gordon, Hoon Kim, Yeung Au, Hongtao Wang, Harish B. Bhandari, Yiqun Liu, Don K. Lee and Youbo Lin Department of Chemistry and Chemical Biology, Harvard University, Cambridge, MA 02138

Keywords: manganese, chemical vapor deposition, diffusion barrier, copper, adhesion

#### ABSTRACT

Barriers to prevent diffusion of copper, oxygen and water vapor were formed by CVD using a manganese precursor vapor that reacts with silica surfaces. The manganese metal penetrates only a few nanometers into the silica to make conformal amorphous manganese silicate layers. This  $MnSi_xO_y$  was found to be an excellent barrier to the diffusion of Cu,  $O_2$  and  $H_2O$  vapor. The adhesion strength of Cu to the  $MnSi_xO_y$  was found to be sufficiently strong to satisfy the semiconductor industry requirements for interconnections in future microelectronic devices. CVD Mn dissolves into copper surfaces and then diffuses to increase adhesion to SiCNO capping layers.

#### **INTRODUCTION**

Copper (Cu) is now becoming the standard material for connecting transistors in microelectronic devices. However, transistors cannot function properly if Cu diffuses into them. Cu also reduces the resistance of the insulating material between the Cu wires. For both these reasons, Cu must be confined inside diffusion barriers that surround the Cu wires. Also, barriers to oxygen and water must separate these materials in the environment from the copper to prevent its oxidation. In current technology, the diffusion barriers are formed by sputtered tantalum nitride (TaN). Although TaN is an effective diffusion barrier, Cu does not adhere strongly to TaN. The adhesion of Cu to tantalum (Ta) metal is much stronger than to TaN, so Ta is sputtered on top of the TaN to enhance the durability of interconnect structures. Next in the process flow a thin Cu "seed" layer is sputtered, and then the trenches and holes are filled with Cu by electroplating.

As the dimensions of microelectronic circuits are being reduced, the non-conformal nature of sputtered barrier (TaN), adhesion (Ta) and seed (Cu) layers has caused problems. These layers are thicker near the top openings, so that the remaining openings are narrower at the top than lower inside the features. Then the electroplating process for Cu can form voids inside the features, which later can lead to failure of the interconnections. Another difficulty arises from roughness on the sidewalls of features, which may prevent deposition of the layers on recessed regions that are shielded from the line of sight to the sputtering target. If these areas are missing TaN, then Cu may diffuse out through these holes in the diffusion barrier. If Ta is missing from an area, then reliability may be reduced because of the reduced adhesion of the Cu to the TaN. If these areas are missing the Cu seed layer, then Cu electroplating will not take place on the oxidized surface of the exposed Ta,

producing voids in the Cu. Thus there is a need for methods to produce more conformal diffusion barriers, adhesion layers and seed layers. CVD and atomic layer deposition (ALD) are methods that can produce conformal diffusion barriers, adhesion layers and seed layers.<sup>1</sup>

Another problem with current diffusion barriers and adhesion layers is that TaN and Ta have a much higher resistivity than Cu. Thus by displacing Cu metal, they increase the resistance of interconnects. The time delay due to interconnects increases with their resistance, and thus the volume of barrier material should be minimized in order to form the fastest circuits. Ideally, a barrier should not occupy any of the volume reserved for Cu. Such a "zero-thickness barrier" can be realized by sputtering a manganese-Cu alloy, from which manganese diffuses into the surface of silica insulation at 450 °C.<sup>2</sup> The resulting self-aligned barrier layer of amorphous manganese silicate (MnSi<sub>x</sub>O<sub>y</sub>), just a few nm thick, remains part of the surface of the insulator, whose dimensions are not significantly changed by in-diffusion of the manganese. The resulting interconnects have lower resistance than ones made with conventional TaN barriers, and have proven to be even more durable as well.<sup>3</sup>

The self-aligned  $MnSi_xO_y$  barriers start with sputtering of a Mn-Cu alloy, so they are still subject to the conformality problems of sputtered barriers. Voids in electroplated Cu may form under overhangs near the tops of features or inside rough areas on the sidewalls In this paper we propose a way to make conformal self-aligned  $MnSi_xO_y$  barriers using CVD of manganese metal. We find that vapors of a manganese compound react with silica surfaces to form a thin amorphous layer of manganese silicate mainly within the surface of the silica. The  $MnSi_xO_y$  layer is shown to be a good barrier against diffusion of Cu, O<sub>2</sub> and H<sub>2</sub>O. CVD Mn also greatly increases the adhesion of copper to capping layers of SiCNO. The layer is completely conformal inside the surfaces of holes and trenches.

#### **EXPERIMENTAL**

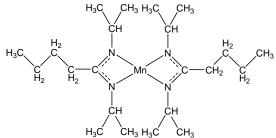

The compound that serves as a precursor for the manganese is called bis(N,N'-diisopropylpentylamidinato)manganese(II), whose chemical formula is shown in Figure 1. The compound was synthesized by methods similar to those described previously.<sup>4</sup> It is a pale yellow crystalline solid that melts at about 60 °C to a clear liquid. For the CVD experiments, the manganese precursor was evaporated from the liquid in a bubbler at a temperature of 90 °C into a 60 sccm flow of highly purified nitrogen (concentrations of water and oxygen less than 10<sup>-9</sup> of the N<sub>2</sub>). The manganese precursor reacts immediately with oxygen or water to form a black material when it is exposed to air. The vapor pressure of the precursor is estimated to be around 0.1 mbar at 90 °C.

The substrates of silica were either thermally oxidized silicon or silica deposited by ALD. The CVD was carried out in a hot-wall tube reactor (diameter 36 mm) within a tube furnace at temperatures between 200 and 400 °C and a total pressure of about 5 Torr. The amount of manganese deposited was measured by Rutherford backscattering spectroscopy (RBS). The MnSi<sub>x</sub>O<sub>y</sub> formation was evaluated by cross-sectional high-resolution transmission electron microscopy (HRTEM). The effectiveness of the  $MnSi_xO_y$  as a barrier to diffusion of Cu was tested in four ways: optical appearance, sheet resistance, Cu silicide formation and capacitance-voltage (CV) analysis of capacitors. For Cu diffusion tests, layers of SiO<sub>2</sub> 8 nm thick were grown on HF-etched silicon wafers by ALD at 215 °C, followed by CVD Mn at 350 °C for 10 min, which formed 2.3 nm of Mn metal. Control samples of SiO<sub>2</sub> omitted the CVD Mn treatment. Then Cu layers about 200 nm thick were deposited on top of the CVD MnSi<sub>x</sub>O<sub>y</sub> or SiO<sub>2</sub> layers. Anneals in a pure nitrogen atmosphere were carried out at temperatures of 400, 450 and 500 °C for one hour. For CV analysis, CVD Mn layer is deposited on 300 nm thermal SiO<sub>2</sub>. Cu pad (500 µm diameter circle) is formed by thermal evaporator using shadow mask. CV was measured with a HP 4275A meter in a shielded probe station at room temperature. The Cu pad samples were used for Bias-Temperature Stress (BTS) test that was conducted at 250°C under 1 MV/cm bias condition in Ar ambient. After this stress condition, CV was measured at room temperature.

#### **RESULTS AND DISCUSSION**

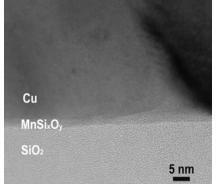

Thin Mn layers (2.3 nm) deposited on SiO<sub>2</sub> did not have any conductivity by 4-point probe (>  $10^6$  ohm/square). It may form MnSi<sub>x</sub>O<sub>y</sub>, which is an insulator, and any remaining metal Mn may be oxidized when the sample is taken out into the air for measurement. Thus, it is not clear from this measurement whether the CVD process deposited manganese metal or some insulating manganese compound. To confirm Mn metal deposition, CVD was carried out on substrates of Cu films 50 nm thick that had been evaporated onto SiO<sub>2</sub>/Si substrates. The resulting structure was examined by cross-sectional HRTEM. Figure 2 shows that the CVD metal Mn diffused through the Cu layer and reacted with the SiO<sub>2</sub> to form an amorphous MnSi<sub>x</sub>O<sub>y</sub> layer about 2~5 nm thick between the Cu and the SiO<sub>2</sub>. The MnSi<sub>x</sub>O<sub>y</sub> layer is thicker near grain boundaries in the Cu, along which Mn diffusion is faster. This result is evidence of Mn metal deposition.

Figure 2. Cross-sectional HRTEM of CVD Mn / PVD Cu / SiO<sub>2</sub>

The effectiveness of  $MnSi_xO_y$  as a copper barrier was evaluated using a sample structure PVD Cu(200 nm)/CVD Mn (2.3 nm)/ALD SiO<sub>2</sub> (8 nm)/Si. A MnSi<sub>x</sub>O<sub>y</sub> layer was formed between the Cu and ALD SiO<sub>2</sub> layers. The shiny Cu color and sheet resistances of these samples were unchanged by anneals in nitrogen at 400 or 450 °C. After a 500 °C anneal, the control sample, which does not have any  $MnSi_xO_y$  layer, turned black and its sheet resistance increased by a factor of 200 because of massive diffusion of the Cu through the thin ALD SiO<sub>2</sub> into the silicon. The CVD Mn sample, by contrast, retained its shiny Cu color and increased its resistance only slightly.

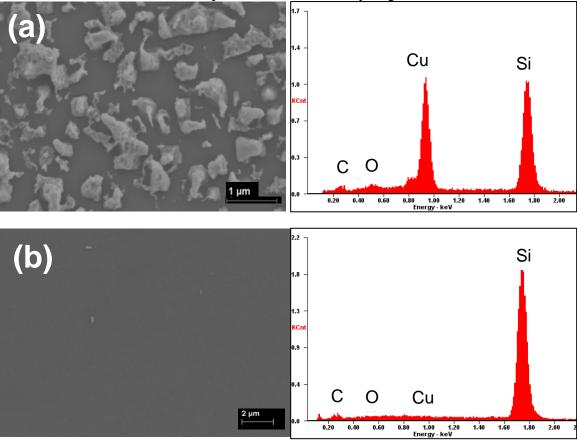

To analyze for Cu diffusion, the remaining Cu layers were dissolved in nitric acid, and then the manganese silicate and silica were removed by dilute HF. The etched surfaces were then analyzed by an energy-dispersive X-ray spectrometer (EDX) and scanning electron micrographs (SEM). Figure 3 shows the SEM results after a 500 °C for 1 hr anneal. The few Cu-containing spots appear to be Cu silicide crystallites oriented by the crystal directions of the silicon. The control sample shows that the majority of its surface is covered by Cu silicide. The control sample showed a large Cu signal in EDX analysis that was stronger than the silicon signal, confirming that the thin ALD SiO<sub>2</sub> allowed diffusion of Cu. The CVD Mn-treated samples did not show Cu by large-area EDX.

**Figure 3.** SEM of etched Si surface after annealing at 500  $^{\circ}$ C (a) with SiO<sub>2</sub> alone, and (b) with CVD MnSi<sub>x</sub>O<sub>y</sub> on SiO<sub>2</sub>.

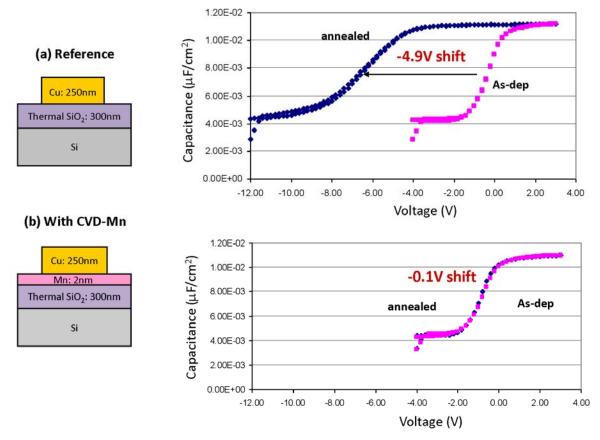

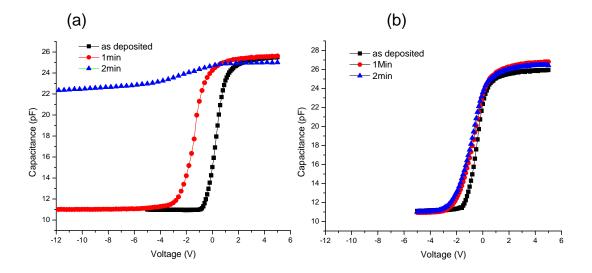

An electrical test of barrier properties was carried out by patterning the Cu into capacitor electrodes. CV curves for samples annealed at 450 °C for 1 hr are shown in Figure 4. The large shift (-4.9 V) to negative voltages in the control sample is caused by positive Cu ions diffusing into the silica insulator.<sup>6</sup> In contrast, the silica protected by  $MnSi_xO_y$  shows only a very small shift (- 0.1 V). This electrical test is more sensitive to diffusion of small amounts of Cu, than the other tests. These CV curves also demonstrate that the capacitance of the SiO<sub>2</sub> is not changed significantly by the CVD Mn treatment. Thus, we can expect this process is acceptable in low-k integration.

**Figure 4.** CV curves of samples before and after annealing at 450  $^{\circ}$ C (a) with SiO<sub>2</sub>, and (b) with CVD MnSi<sub>x</sub>O<sub>y</sub> on SiO<sub>2</sub>.

Anneals of similar capacitors were also conducted under an applied voltage of 1 MV/cm at 250 °C. Bias temperature stress (BTS) test is more sensitive method for Cu diffusion into SiO<sub>2</sub>, because Cu ion diffusion in the SiO<sub>2</sub> is accelerated by electric field.<sup>6</sup> BTS condition is closer to the environment of chip operation. Thus, BTS testing gives more relevant results for evaluating Cu diffusion barriers.<sup>6</sup> The control sample lost the capacitance behavior just after 2 min in the BTS condition, implying that a large amount of Cu diffused into the Si, so that the Si would not work as a semiconductor. However, the CVD Mn treated sample had no significant change in its CV curve (Figure 5). The results of this BTS test confirm the good Cu barrier properties of the MnSi<sub>x</sub>O<sub>y</sub> layers.

**Figure 5.** CV curves of samples before and after annealing at 250  $^{\circ}$ C under a 1 MV/cm field (a) with SiO<sub>2</sub>, and (b) with CVD MnSi<sub>x</sub>O<sub>y</sub> on SiO<sub>2</sub>.

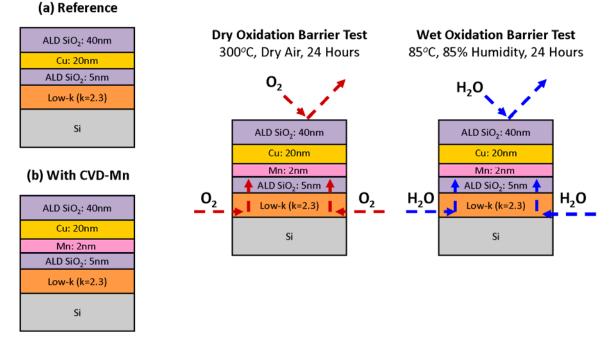

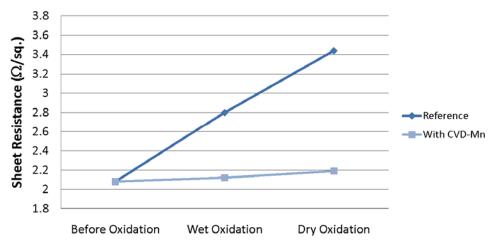

$MnSi_xO_y$  layers were also found to be good barriers to oxygen and water, which can corrode copper layers. To test how well the metal silicate layers protected copper, commercial low-k porous insulator layers from Applied Materials were coated with manganese as described above, followed by PVD copper. The top surface of the copper was protected with 40 nm of ALD silica.<sup>7</sup> The sample was cut into pieces to expose the edges of the low-k insulator so that oxygen or water vapor could diffuse into the low-k layer by the pathways shown in Fig. 6.

Figure 6. Sample structures and pathways for tests of MnSi<sub>x</sub>O<sub>y</sub> as an oxidation barrier.

After exposure to dry air at 300 °C for 24 hours, the CVD-Mn-treated sample maintained its shiny copper color. A control sample without the CVD manganese treatment was corroded near its edges to dark copper oxide by the same exposure. This test shows that the manganese silicate layer is a good barrier to oxygen. Similar tests in a humid atmosphere (85% humidity at 85 °C for 24 hours) showed that the manganese silicate layer is a good barrier to water and oxygen also significantly increased the sheet resistance of the unprotected control copper layers, whereas the resistance of the Mn-protected copper layers remained nearly constant (Fig. 7.).

Figure 7. Sheet resistance of copper before and after oxidation.

The formation of the  $MnSi_xO_y$  layer remarkably increased the adhesion of the Cu/SiO<sub>2</sub> interface, which failed the tape adhesion test prior to the CVD of Mn, but easily passed after the CVD of Mn. Adhesion strength was measured by 4-point bend tests.<sup>5</sup> The samples were prepared by CVD of Mn onto thermal SiO<sub>2</sub> on silicon wafers. Then CVD at 160 °C was used to form Cu oxynitride (CuON), which was then reduced to Cu metal by a hydrogen plasma at room temperature.<sup>8</sup> The adhesion energy was found to be  $10.1 \pm 1$  J m<sup>-2</sup>, which is higher than the value of 5 J m<sup>-2</sup> that is considered to be sufficient for making durable interconnections.<sup>9</sup>

The CVD Mn process can also be used to strengthen the adhesion between copper and the commonly-used capping layers of SiCNO. To test this adhesion effect, 50 nm of copper was evaporated onto SiCNO layers (BLoK<sup>TM</sup>, Applied Materials). The Cu showed very poor adhesion, with adhesion energy less than 3 J m<sup>-2</sup>. Next, similar Cu/SiCNO layers were treated by CVD Mn at 350 °C for 10 minutes. This process increased the sheet resistance from 0.5 ohms/square to 1 ohm per square because of the manganese impurity in the copper. Then the structure was annealed for 1 hour at 400 °C in a nitrogen atmosphere. The sheet resistance then returned to 0.5 ohms per square because the manganese diffused to the surfaces or the interface. The out-diffusion of the manganese from the Cu film was confirmed by SIMS analysis. After the manganese treatment, the adhesion energy was remarkably increased to greater than 12 J m<sup>-2</sup>, because manganese at both surfaces.

created by delamination of the 4-point bend test sample. The exact compounds formed at the interface are not known.

This manganese metal diffusion process could be used to strengthen the bond between copper and the usual SiCNO capping layers. To do this, CVD Mn would be applied just after chemical-mechanical polishing, thereby dissolving Mn into the upper portions of the Cu below its polished surface. After SiCNO deposition, this dissolved Mn will diffuse up to the surface of the SiCNO and strengthen its bonding to the copper, probably increasing the electromigration lifetime.<sup>10</sup>

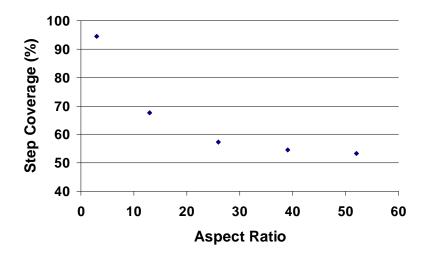

Complete conformality of the CVD CuON depositions in holes with aspect ratios up to 40:1 was confirmed by cross-sectional SEM studies.<sup>8</sup> Because the  $MnSi_xO_y$  layers are too thin to image by SEM, the distribution of CVD  $MnSi_xO_y$  was tested by Energy Dispersive Analysis by X-rays (EDAX) for Mn. The test substrates were holes in silicon with a very high aspect ratio of 52:1 and a native oxide surface with which the Mn precursor reacted. The results plotted in Fig. 8 show how the Mn content decreased with distance into the holes. At an aspect ratio of 3 (typical of interconnects), the step coverage is about 95 %. Even at the bottom of the very narrow holes (52 diameters deep) the amount of Mn is more than half of the amount at the top entrances to the holes.

Figure 8. Distribution of CVD Mn down the length of a hole with aspect ratio 52:1.

This result shows that the Mn precursor has a fairly slow reaction with silica surfaces at 350 °C. Thus interconnect trenches and vias with typical aspect ratios less than 5:1 can be coated fairly uniformly with CVD  $MnSi_xO_y$  at 350 °C. At lower temperatures, the surface reactions are expected to be slower, and the conformality should be even higher. Even when roughness is present on sidewalls, the CVD process should form a complete  $MnSi_x-O_y$  diffusion barrier without pinholes or gaps.

#### CONCLUSIONS

In summary, we presented a simple CVD method to make conformal self-aligned diffusion barriers of manganese silicate. This  $MnSi_xO_y$  is an effective barrier to diffusion

of copper, oxygen and water. Because the  $MnSi_xO_y$  is formed within the insulator, it does not decrease the volume available for Cu, as happens with conventional Ta/TaN barriers. Also, the CVD Mn dissolves into copper surfaces, such as at the tops of vias, so no resistive barrier exists between the tops of vias and the copper in the next higher level. The CVD process can also be used to strengthen the interfacial bonding between copper and a capping barrier layer of SiCNO. Thus more conductive and more durable interconnections are possible using the self-aligned  $MnSi_xO_y$  barriers. The CVD Mn-CuON process should allow formation of conformal seed layers for void-free electroplating of Cu in even the narrowest interconnects.

#### ACKNOWLEDGMENTS

This work was performed in part at the Center for Nanoscale Systems (CNS), a member of the National Nanotechnology Infrastructure Network (NNIN), which is supported by the National Science Foundation under NSF award no. ECS-0335765. CNS is part of the Faculty of Arts and Sciences at Harvard University. D. K. Lee was supported by a Korea Research Foundation Grant from the Korean Government (MOEHRD, KRF-2005-214-C00206). Substrates and SIMS analysis were supplied by IBM. This work was supported in part by Intel Corporation and the National Science Foundation.

#### REFERENCES

- 1. The International Technology Roadmap for Semiconductors, http://public.itrs.net (2007).

- J. Koike and M. Wada, Appl. Phys. Lett. 87 (4), 041911/1 (2005); M. Haneda, J. Iijima, and J. Koike, Appl. Phys. Lett. 90 (25), 252107/1 (2007); J. Koike, M. Haneda, J. Iijima, Y. Otsuka, H. Sako, and K. Neishi, J. Appl. Phys. 102 (4), 043527/1 (2007).

- J. Iijima, M. Haneda, and J. Koike, IEEE Int. Interconnect Technol. Conf., Proc., 155 (2006); J. Koike, M. Wada, T. Usui, H. Nasu, S. Takahashi, N. Shimizu, M. Yoshimaru, and H. Shibata, AIP Conf. Proc. 817 (Stress-Induced Phenomena in Metallization), 43 (2006); T. Usui, H. Nasu, S. Takahashi, N. Shimizu, T. Nishikawa, M. Yoshimaru, H. Shibata, M. Wada, and J. Koike, IEEE Trans. Electron Devices 53 (10), 2492 (2006); T. Usui, K. Tsumura, H. Nasu, Y. Hayashi, G. Minamihaba, H. Toyoda, H. Sawada, S. Ito, H. Miyajima, K. Watanabe, M. Shimada, A. Kojima, Y. Uozumi, and H. Shibata, IEEE Int. Interconnect Technol. Conf., Proc., 216 (2006); H. Haneda, T. Tabira, H. Sakai, H. Kudo, M. Sunayama, N. Ohtsuka, A. Tsukune, and N. Shimizu, Conf. Proc. AMC XXIII, 59 (2008).

- 4. B. S. Lim, A. Rahtu, J.-S, Park, and R. G. Gordon, Inorg. Chem. 42, 7951 (2003).

- 5. Y. Lin, J.J. Vlassak, T.Y. Tsui, and A.J. McKerrow, Materials Research Society Symposium Proceedings **795**, 93 (2004).

- 6. A.L.S. Loke, C. Ryu, C. P. Yue, J. S. H. Cho, and S. S. Wong, IEEE Elec. Device Lett. **17**, 549 (1996).

- 7. D. Hausmann, J. Becker, S. Wang, and R. G. Gordon, Science 298, 402 (2002).

- 8. H. Kim, H. B. Bhandari, S. Xu, and R. G. Gordon, J. Electrochem. Soc. 155, H496 (2008).

- 9. L. Peters, Semiconductor International (July 1, 2001).

- 10. M. W. Lane, E. G. Liniger, and J. R. Lloyd, J. Appl. Phys. 93, 1417 (2003).