DIGITAL ACCESS TO SCHOLARSHIP AT HARVARD DASH.HARVARD.EDU

# Direct Liquid Evaporation Chemical Vapor Deposition(DLE-CVD) of Nickel, Manganese and Copper-Based Thin Films for Interconnects in Three-Dimensional Microelectronic Systems

## Citation

Li, Kecheng. 2016. Direct Liquid Evaporation Chemical Vapor Deposition(DLE-CVD) of Nickel, Manganese and Copper-Based Thin Films for Interconnects in Three-Dimensional Microelectronic Systems. Doctoral dissertation, Harvard University, Graduate School of Arts & Sciences.

## Permanent link

http://nrs.harvard.edu/urn-3:HUL.InstRepos:33493366

## Terms of Use

This article was downloaded from Harvard University's DASH repository, and is made available under the terms and conditions applicable to Other Posted Material, as set forth at http://nrs.harvard.edu/urn-3:HUL.InstRepos:dash.current.terms-of-use#LAA

# **Share Your Story**

The Harvard community has made this article openly available. Please share how this access benefits you. <u>Submit a story</u>.

Accessibility

## Direct Liquid Evaporation Chemical Vapor Deposition (DLE-CVD) of Nickel, Manganese and Copper-based Thin films for Interconnects in Three-Dimensional Microelectronic Systems

A dissertation presented

by

#### **Kecheng Li**

to

#### The John A. Paulson School of Engineering and Applied Sciences

in partial fulfillment of the requirements

for the degree of

#### **Doctor of Philosophy**

in the subject of

**Applied Physics**

Harvard University

Cambridge, Massachusetts

April, 2016

© 2016 – Kecheng Li

All rights reserved.

**Professor Roy G. Gordon**

## Direct Liquid Evaporation Chemical Vapor Deposition (DLE-CVD) of Nickel, Manganese and Copper-based Thin films for Interconnects in Three-Dimensional Microelectronic Systems

### Abstract

Electrical interconnects are an intrinsic part of any electronic system. These interconnects have to perform reliably under a wide range of environmental conditions and survive stresses induced from thermal, mechanical, corrosive and electrical factors. Semiconductor technology is predominantly planar in nature, posing a severe limitation to the degree of device integrations into systems such as micro-processors or memories. 3D transistor FinFET (Fin type Field Effect Transistors) has been used by Intel since the advent of its 22 nm technology node, and has now advanced further down to 14 nm. While the technology nodes have consistently been shrinking in line with Moore's law, increasing difficulties in scaling down the feature sizes in transistors is urging the industry to seek alternative fabrication approaches for the extension of Moore's law. The most promising solution thus far is 3D heterogeneous integration, which will stack logical and analog chips together to enable multi functions chip without the need to scale the size of transistors with Moore's law. Furthermore, as wearable electronics are fast growing in the next big wave in consumer electronics after the smartphone era, interconnects face the unique challenge of having to be embedded into fashion and withstand the mechanical stresses from everyday activity. This makes the role interconnects even more important as well as making it the main bottleneck to unleashing the full performance of the 3D microelectronics systems.

This thesis explores the fabrication, characterization and application of Nickel, Manganese, Copper based thin films for the interconnects of 3D microelectronics systems. Direct Liquid Evaporation-Chemical Vapor Deposition (DLE-CVD) technique has been proven to be a highthroughput process for high-quality Nickel, Manganese, Copper based thin films with excellent conformality in complex architectures as the interconnects for state-of-the-art 3D microelectronics systems.

Chapter 2 introduces the advantages of DLE-CVD process and its application in deposition of Nickel, Manganese and Copper based thin films. DLE-CVD process is used to deliver consistent and high vapor concentrations of Nickel, Manganese and Copper precursors to coat nanostructures with high aspect ratios.

Chapter 3 demonstrates the atom probe tomography (APT) as an effective method for understanding the 3D microstructure and compositional properties in thin films at an atomic scale. 3D compositional information of DLE-CVD NiNx, NiSi thin films from inside and outside regions of the trench structures have been investigated using APT. The APT characterization technique provides a unique tool that can be applied both to the design of 3D nanostructured microelectronic devices and to the further understanding of the fundamental physical properties.

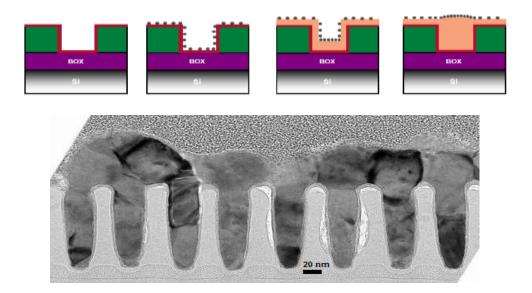

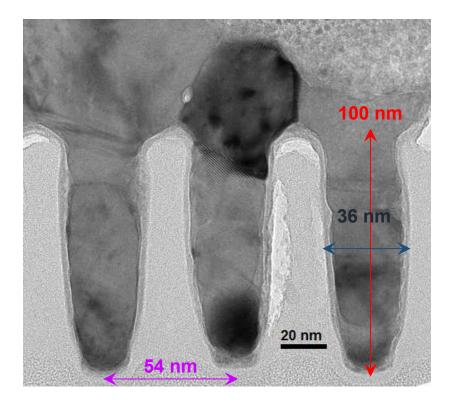

iv

Chapter 4 highlights the application of DLE-CVD manganese and copper based thin film process in the complex nanostructures for 3D microelectronic systems. Narrow trenches with width under 30 nm are the key nanostructure in the local interconnects in 3D FINFET with technology node smaller than 14 nm for use in microelectronic chips. It can be filled with DLE-CVD copper and copper-manganese alloy in a bottom-up fashion using a surfactant-catalyzed CVD process. An ultrathin manganese nitride layer (~ 3 nm) acts as a diffusion barrier and an adhesion layer. Through-silicon vias (TSVs) plays a crucial role in advancing the 3D integration of semiconductor devices by improving the performances of interconnections between chips. Using DLE-CVD processes, conformal, smooth and continuous copper/copper-manganese seed layers can be prepared in TSVs with aspect ratio greater than 25:1. manganese Nitride film is deposited via the DLE-CVD process to serve as an adhesion and barrier layer. Dow Chemicals achieved voidfree TSV filling through the electroplating process.

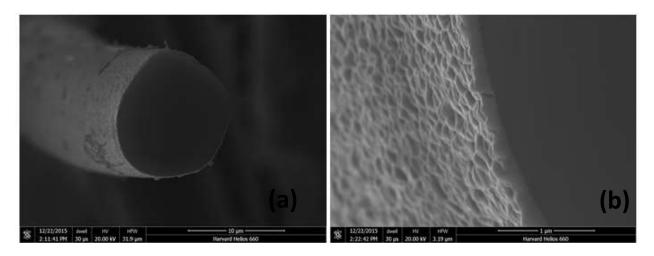

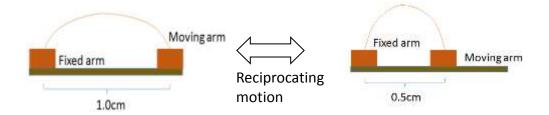

Chapter 5 shows the application of the DLE-CVD manganese and copper based thin film process in the metallization of polyaramids for the application in the interconnects embedded in wearable electronic systems. Conformal and conductive coatings of copper-manganese have been successfully deposited on Kevlar fibers using the DLE-CVD process with complete film coverage. The mechanical resistance of copper-manganese coated Kevlar was tested via our inhouse robotic arm system, demonstrating how the electrical resistance of the wire remains unchanged despite being flexed repeatedly to a bend of 5mm radius for half a million times.

۷

## Table of Contents

| Chapter 1               | Introduction1                                                                                     |

|-------------------------|---------------------------------------------------------------------------------------------------|

| 1.1 Int                 | erconnects in 3D Microelectronic System1                                                          |

| 1.1.1                   | 3D Microelectronic System1                                                                        |

| 1.1.2                   | Categories of Interconnects in 3D Microelectronic System                                          |

| 1.2 Nic                 | kel, manganese and copper-based thin films in 3D Microelectronic System                           |

| 1.2.1                   | Overview of Nickel, manganese and copper-based Thin Films                                         |

| 1.2.2                   | Nickel-based thin Films in 3D Microelectronic System5                                             |

| 1.2.3                   | Manganese and copper-based thin Films in 3D Microelectronic System                                |

| 1.3 De                  | position Techniques9                                                                              |

| 1.3.1                   | Physical Vapor Deposition9                                                                        |

| 1.3.2                   | Chemical Vapor Deposition11                                                                       |

| 1.3.3                   | Direct Liquid Evaporation Chemical Vapor Deposition12                                             |

| 1.4 Ov                  | erview of Thin Film Characterization14                                                            |

| 1.4.1                   | Thickness and Structural Characterization14                                                       |

| 1.4.2                   | Chemical Characterization15                                                                       |

| 1.4.3                   | Atom Probe Tomography17                                                                           |

| Chapter 2               | DLE-CVD Processes of nickel, manganese and copper-based thin films                                |

| 2.1 Introc              | luction                                                                                           |

| 2.2 Exper               | iments                                                                                            |

| 2.2.1 N                 | 1etal Amidinate Precursors                                                                        |

| 2.2.2Pr                 | recursor Chemistry in DLE-CVD of nickel, manganese and copper-based thin film 30                  |

| 2.2.4 D                 | LE CVD Reactor Setup                                                                              |

| 2.2.5 C                 | haracterization Methods                                                                           |

| 2.3 Resul               | ts and Discussion                                                                                 |

| 2.3.1 D                 | LE CVD Process of Nickel Nitride thin films and conversion to Nickel Silicide                     |

| 2.3.2 D                 | LE CVD Process of manganese Nitride and copper Thin films                                         |

| 2.4 Concl               | usions                                                                                            |

| Chapter 3<br>Atom Probe | DLE CVD Nickel-based thin film for local interconnects in 3D microprocessors and<br>Investigation |

| 3.1 Int                 | roduction                                                                                         |

| 3.2 Exp                 | periments                                                                                         |

| 3.3 Re                   | sults and Discussion                                                                            | 57      |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------|---------|--|--|--|

| 3.3.1                    | DLE CVD of Nickel Nitride and Nickel Metal in high aspect ratio nanostructu                     | res 57  |  |  |  |

| 3.3.2                    | Conversion to Nickel Silicide                                                                   | 58      |  |  |  |

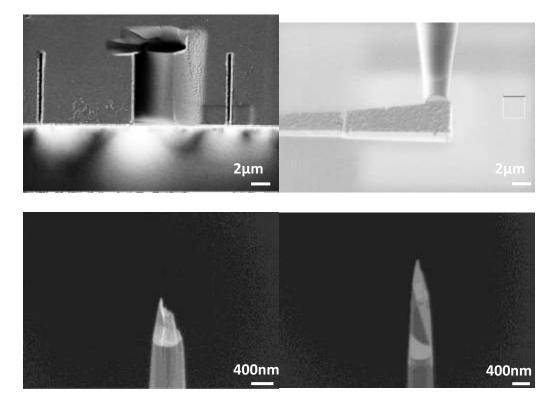

| 3.4 Sp                   | ecimen Preparation for Atom Probe Tomography                                                    | 59      |  |  |  |

| 3.4.1                    | Specimen Geometry Requirements                                                                  | 59      |  |  |  |

| 3.4.2                    | Deposition-Based Specimen Preparation                                                           | 60      |  |  |  |

| 3.4.3<br>nano s          | Focused Ion Beam (FIB)-Based Specimen Preparation in ultra high aspect ra<br>tructures          |         |  |  |  |

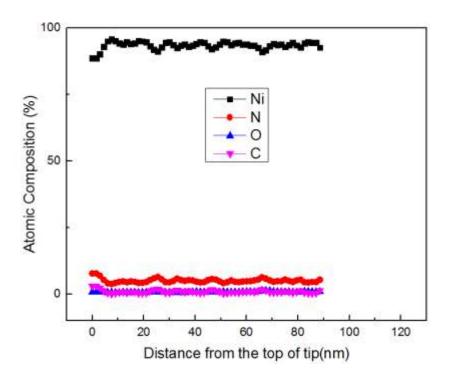

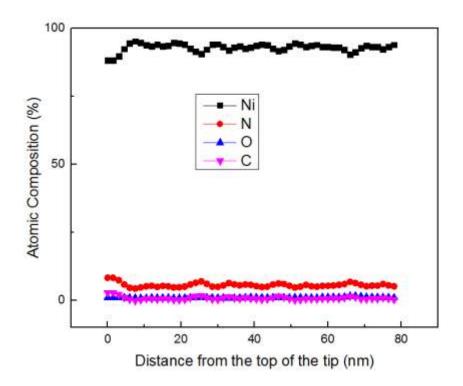

|                          | om Probe Tomography Investigation of Nickel Nitride Thin Films in Ultra high a o structures     | •       |  |  |  |

| 3.5.1<br>specim          | Optimizing the ATP analytical conditions for Nickel Nitride Thin Films with P ens               |         |  |  |  |

| 3.5.2                    | ATP result of NiN <sub>x</sub> film inside and outside of ultra high aspect ratio nanostru $70$ | ictures |  |  |  |

|                          | om Probe Investigation of Nickel Silicide Thin Films in Ultra high aspect ratio n<br>s          |         |  |  |  |

| 3.6.1                    | ATP sample preparation                                                                          | 75      |  |  |  |

| 3.6.2                    | 1D compositional depth profiles                                                                 | 77      |  |  |  |

| 3.6.3                    | Spatial Composition Mapping of Nickel Silicide                                                  | 78      |  |  |  |

| 3.6.4                    | Decomposition                                                                                   | 79      |  |  |  |

| 3.7 Co                   | nclusions                                                                                       | 80      |  |  |  |

| Reference                | es                                                                                              | 81      |  |  |  |

| Chapter 4<br>in 3D micro | DLE-CVD manganese-based and CuMn alloy thin film materials for intercon                         |         |  |  |  |

|                          | luction                                                                                         |         |  |  |  |

|                          | iments                                                                                          |         |  |  |  |

| •                        | ts and Discussion                                                                               |         |  |  |  |

|                          | usions                                                                                          |         |  |  |  |

| Chapter 5<br>CuMn alloy  | Metallization on Polyaramids for electronic textiles with DLE-CVD Mangane thin film materials   |         |  |  |  |

|                          | luction                                                                                         |         |  |  |  |

|                          | iment                                                                                           |         |  |  |  |

| •                        | ts and Discussion                                                                               |         |  |  |  |

|                          | 5.4 Conclusions                                                                                 |         |  |  |  |

## Acknowledgments

I would like to express my sincere gratitude to the countless people who have been an indispensable part of my PhD life in making this challenging process an enjoyable one.

First, I would like to thank my advisor Professor Roy G. Gordon for his tremendous support and valuable guidance throughout my graduate career. Roy is not only a great scientist with extensive knowledge in chemistry, but also a great mentor with patience. I am deeply grateful for his generous contributions of his time, of innovative ideas and of funding that made my research not only highly productive but also intellectually stimulating.

I would also like to thank the other members of my thesis committee, Professor Frans Spaepen and Professor Joost Vlassak. Frans has guided me from the beginning to the end of my PhD career. Thank you Frans for serving both on my qualifying committee and on my thesis committee. Frans is a great teacher. His courses "Solids: Structure and Defects" and "Kinetics of Condensed Phase Processes" helped me build a solid foundation for my graduate research. Also from Joost is his classs "Solid mechanics" from which I built the foundation on mechanics, which turned out to be extremely useful for my graduate research.

Besides my thesis committee, I need to extend my gratitude and thank many other great mentors who supported me along the way. I am grateful for my advisor in Xi'an Jiaotong University, Professor Hong Wang, who played an important role on my choice of graduate schools. She always has faith in me and cheers me up when I am at my lowest point. I feel lucky to know such a caring advisor.

I am indebted to my colleagues from Gordon Group. The members of the Gordon group have contributed immensely to my personal and professional life at Harvard. I enjoyed my days in Gordon group and I had great fun working with them. I deeply treasure the great friendship built over the years and believe some will last lifelong. I would like to express my greatest gratitude to Danny (Mingwei) Chua for introducing me to the Gordon group, which opened up my life to this incredible field of research. I owe countless thanks to Danny Chua for the extraordinarily insightful discussions and remarkably creative criticisms in the lab. Danny has also radically improved my work-life balance in graduate school with the strikingly memorable escapes away from lab. I also want to thank my mentor, Dr. Yeung (Billy) Au, for teaching me the basics of CVD reactor design and construction. And I am grateful for many people who I worked with and shared ups and downs together: Dr. Jing Yang, Dr. Leizhi Sun, Dr. Bin Xi, Dr. Xinwei Wang, Dr. Zhefeng Li, Dr. Yiqun Liu, Dr. Sang Bok Kim, Dr. Luke Davis, Dr. Eugene Beh, Xiabing Lou, Jun Feng, Lu Sun, Xiang Gong, Kaixiang Lin, Michael Vogel, Xizhu Zhao, Liuchuan Tong, Robert Gustafson, Christina Chang, Ashwin Jayaraman, Rachel Heasley, Lauren Hartle, Aykut Aydin, Chuanxi Yang, Dr. Dawen Pang, , Prof. Qiang Chen, Prof. Xudong Chen, Prof.

Zhongwei Liu, Dr. Tamara Powers. I also need to thank Teri Howard, my lab admins, for making my life much easier.

I need to extend my warm gratitude to my friends. I met most of my friends at Harvard in the Harvard Chinese Students and Scholars Association. The 4-year experience is definitely the highlight of my graduate life. Thanks for all the emotional support, camaraderie, entertainment, and caring they provided. There are too many friends in a long list to thank: Hechen Ren, Dr. Haifei Zhang, Dr. Xu Zhang, Dr. Yu Lei, Dr. Lilei Xu, Dr.Ruichao Ma, Dr. Tao Tong, Dr.Wenqi Zhu, Dr. Dongxing Wang, Dr. Yang Li, Dr. Sicong Shan, Ge Zhang, Yunfei Xu, Ruobing Bai.

Finally yet importantly, I would like to thank my parents, Furong Yang and Wangzhang Li, for their unconditional love and uplifting encouragement. Without their sincere understanding and endless support, all these accomplishments and the completion of my PhD will not have been possible. Their trust in me has given the freedom to pursue my dreams and for this I will be grateful for eternity.

Kecheng Li Cambridge, Massachusetts May 7 2016 Page intentionally left blank

To my parents

for their love and support

### 献给我的父亲母亲

### 感谢父母的爱与支持

Page intentionally left blank

## Chapter 1 Introduction

#### 1.1 Interconnects in 3D Microelectronic System

#### 1.1.1 3D Microelectronic System

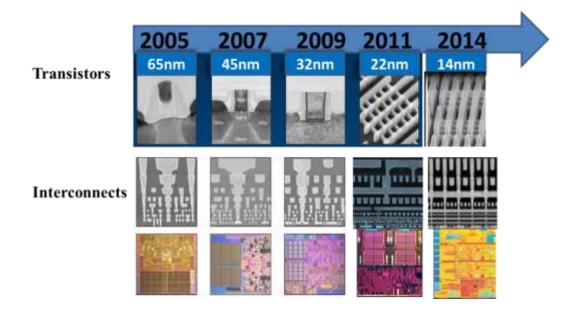

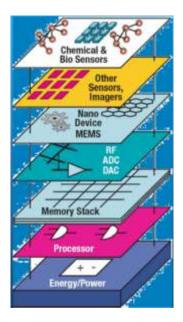

Interest in three-dimensional (3D) semiconductor technology has increased dramatically in the recent years. Moore's law predicts the doubling of semiconductor transistor density every 1-1.5 years, requiring rapid advancement in device miniaturization and improvements in electrical interconnect densities. Decades of semiconductor scaling on a two-dimensional (2D) level has far outpaced innovations at the 3D die stacking technologies. As we begin to get diminishing returns in improving traditional 2D semiconductor scaling, the industry has begun focusing more on developing 3D integration with a focus on through-silicon vias (TSV) for scaling in the vertical direction and faster interconnects between multiple dies in a 3D die stack.[1]

As we progress microelectronic systems from 2D to 3D, it is important to note the dominant differences to understand the challenges that 3D systems present. 2D microelectronic systems are planar and consist of a single layer. On the other hand, 3D systems have features defined in the vertical direction and consist of multiple layers stacked together. Interconnects in the 2D

systems require films that are uniformly deposited on a flat surface that adhere well; they do not need to survive flexing of the electronic components. In the 3D systems, interconnects require films to be uniformly deposited in 3D structures with high aspect ratios, and demand that the films be capable of withstanding a large number of bends while maintaining operating performance.

#### 1.1.2 Categories of Interconnects in 3D Microelectronic System

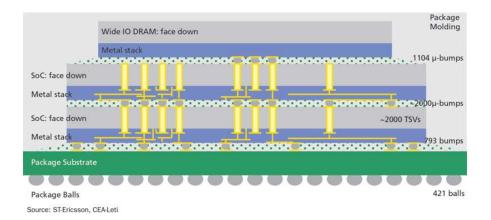

Through-silicon vias (TSVs), thinned silicon and fine-pitched silicon-silicon interconnections (SSIs) are the three main emerging technologies in 3D die stacks. [2] These 3D silicon technologies are rapidly gaining momentum now that Moore's law is decelerating and potentially coming to a halt. TSVs are the most promising 3D integration technology in the current strategies. [3]

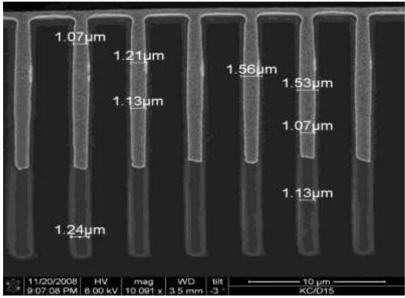

TSV technology is essential for both die-to-die and wafer-to-wafer stacking in order to achieve high bandwidth and low inductance in these vertical interconnects.[4] The desired TSV structures can range widely, including diameters that range from 1 to 90  $\mu$ m, with silicon thickness ranging from 1  $\mu$ m typical of SOI to 730  $\mu$ m which is the thickness of a full wafer. Aspect ratios of these structures can be as low as 2:1 and as high as 50:1. Copper, tungsten and other composite compounds are potential material candidates for TSVs.[5][6]

2

Figure 1.1. TSVs for the interconnects in 3D ICs. Source: http://www.eettaiwan.com/

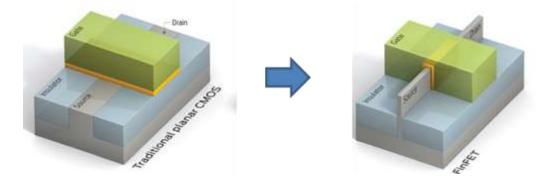

The 3D transistors is a form of non-planar transistor architecture that features a gate stacked above two vertical gates, first demonstrated by Intel Corporation in September 2002. [7]With essentially triple the surface area of previous transistors for conducting electron flow, these new type of transistors allow more current to flow when they are in the "on" state, providing higher switching speed and a significantly lower power consumption. By replacing the conventional flat 2D planar gate with a thin vertical 3D fin, 3D transistors are able to provide improvements both in performance and in energy efficiency.

Figure 1.2. Cross-sectional micrograph view of the transistor (top) and metal interconnects (bottom)demonstrating the rate of miniaturization of in microelectronic components. Source: Intel.

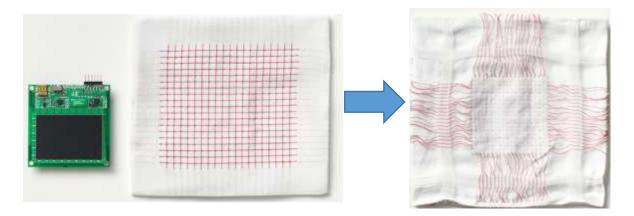

Wearable electronics consists of fabric materials that are embedded with electronics connected together via interconnections, enabling smaller sizes and greater flexibilities far beyond what can be achieved using traditional manufacturing techniques for electronic systems. [8]Interconnect wires that allow the wide range of devices in the electronic systems to communicate must be sufficiently robust to survive continuous dynamic stresses brought on by flexing, bending, twisting, stretching and dropping in an uncontrolled use environment.

Figure 1.3. Project Jacquard makes it possible to weave touch and gesture intractivity into any textile using standard industrial looms. Source: Project Jacquard

#### 1.2 Nickel, manganese and copper-based thin films in 3D Microelectronic System

#### 1.2.1 Overview of Nickel, manganese and copper-based Thin Films

With the shrinking of features in microelectronic circuits, existing materials for transistor interconnects and diffusion barriers can no longer be fabricated using traditional methods involving physical vapor deposition.[9] For highly conformal thin film coatings demanded by the technological advances in the advanced semiconductor industry, new deposition processes using atomic layer deposition (ALD) and chemical vapor deposition (CVD) must be explored for compounds based on materials such as nickel, manganese and copper.[10][11]

#### 1.2.2 Nickel-based thin Films in 3D Microelectronic System

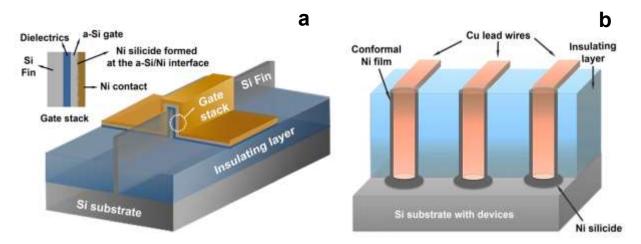

Recent years have seen rapid miniaturization in modern electronics continue, making interfacial issues become critical for the overall performance and durability of electronic architectures, of which a most important issue is discovering a high performance contact between silicon and metals. In advanced semiconductor manufacturing processes, nickel silicide is fast becoming the preferred method for improving the contact with silicon due to its lower formation temperature, higher conductivity and smoother interface as compared to the alternatives, which are the silicide of cobalt and titanium. [12]

Although Ni silicide has various advantages, one of the greatest challenges is to reduce the silicon consumption during the silicide formation while keeping a low resistivity, low formation temperature and high stability. By introducing Ni monosilicide phase (NiSi) instead of NiSi<sub>2</sub> or

Ni<sub>2</sub>Si, these requirements can be met since NiSi has a low resistivity of around 14 m $\Omega$ -cm and only requires formation temperature below 400 °C, while NiSi<sub>2</sub> requires higher than 600 °C and Ni<sub>2</sub>Si is unstable when interfacing with silicon. Therefore, to enable higher-performance silicon devices, development of processes toward high-quality NiSi at Ni/Si interface is urgently called for.[13]

#### 1.2.3 Manganese and copper-based thin Films in 3D Microelectronic System

Copper was introduced as the material of choice for interconnect lines in 1997 as a viable replacement for aluminum alloy due to copper having a lower electrical resistivity (1.67  $\mu$ Ω-cm) and higher resistance towards electro migration.[14] As transistors get smaller and smaller, each new generation of microprocessors demand ever decreasing thickness of wire interconnects connecting transistors. The downscaling of these features means a reduced cross-sectional area and increased capacitance will result in the loss of device performance due to increased resistivity and increased interconnect delays (RC delays). This forced the industry to seek a higher performing replacement material for the existing aluminum-based wires.

6

Figure 1.4. Cross-sectional micrograph view of the transistor (top) and metal interconnects (bottom) demonstrating the rate of miniaturization of in microelectronic components. Source: Intel.

When copper become the industry standard material for interconnects, it was crucial to avoid copper diffusion into the transistors as copper contamination can cause the transistors to stop functioning. As a result, diffusion barriers must be applied to the copper interconnect wires to confine them within the interconnect regions only.

Tantalum nitride diffusion barriers are typically used by the industry as a diffusion barrier material for copper.[12] Unfortunately, TaN has poor adhesion to copper, so Ta metal has to be deposited after the deposition of TaN barrier layer, followed by a thin copper seed layer and filling of the trenches and holes via electrodeposition of copper.[15]

Several challenges arise when the feature scales of these microelectronic circuits shrink dramatically in size. Due to the non-conformal characteristics of sputtered film, the sputtering of TaN as a barrier layer, Ta metal as the adhesion layer, and Cu metal as the seed layer for Cu electrodeposition are not able to provide a uniform coating in the high aspect ratio structures in these devices, resulting in film depositions that are thicker near the opening of these features and thinner near the bottom of them. Consequently, the electrodeposition of copper will fail to fill completely these trenches with high aspect ratio. Therefore highly conformal ALD and CVD thin film deposition processes have to be developed to overcome these problems.[16]

#### **1.3 Deposition Techniques**

Thin film deposition techniques are considered the most critical component to the creation of microelectronic devices. Device engineers continuously push the limits of semiconductor technologies by demanding films of higher quality and complexity, and the number of stages involved in such devices can reach over a thousand steps. The first 500 steps belong to FEOL and the remaining 500 steps correspond to the BEOL portion, both essential to the modern microprocessor fabrication.[17]

Thin film deposition is the method of choice for depositing critical layers in the nanometer to micrometer scales utilized in microelectronic devices. Thin film deposition can be classified into two different types, physical vapor deposition and chemical vapor deposition.

#### 1.3.1 Physical Vapor Deposition

Physical vapor deposition process, unlike chemical vapor deposition processes, do not involve chemical reactions. The target material vapors are generated via thermal heating or using high energy ion bombardment. Sputtering and evaporation are the two most common techniques used in physical vapor deposition.[9]

#### **1.3.1.1** Evaporation

During the early days of semiconductor device fabrication, the metal films were predominately deposited by evaporation technique. Wafers are inserted into a high-vacuum process chamber of the evaporator system which is evacuated by a cryogenic vacuum pump and is maintained at a low pressure of under 10<sup>-5</sup> Torr. The target deposition material is heated in a crucible using an embedded resistive heater (thermal evaporation) or using a beam of electrons (e-beam evaporation). A mechanical shutter is positioned between the crucible and the substrate to allow the deposition to start and stop sharply and abruptly. Under such low pressure in the chamber, the material vapors transverse across the chamber in a straight path before arriving at the surface of the substrate wafer. Over time the accumulation of material vapors on the substrate results in the formation of the desired film.[18]

#### 1.3.1.2 Sputtering

Sputtering is the primary deposition technique used to deposit diffusion barriers, adhesion layers and seed layers in copper interconnect systems. Sputtering involves ejecting particles of the target material to be deposited from a solid target material using the energetic bombardment of this target using high energy particles just as inert gas ions.[9]

In a sputtering system, the plasma chamber is designed so that high-energy ions striking the solid target material. The higher pressure in sputtering systems results in films of higher conformity and step coverage due to atoms experiencing more gas-phase collisions. Material

composition can be controlled more closely and deposition rates can be high. With sputtering being a physical etching process, a wide range of materials are suitable for deposition using the sputtering technique. When high growth rates are desired, DC sputtering is employed. On the other hand, when the deposited materials are insulating in nature, RF sputtering involving plasma is preferred.[19]

#### **1.3.2** Chemical Vapor Deposition

Chemical vapor deposition is the process of reacting the vapor of a volatile precursor compound with other gases via chemical reactions, to produce high quality, high-performance nonvolatile solid film that deposits on a substrate. [17] Volatile by-products are usually produced from the CVD reactions, which are evacuated from the process chamber by gas flows. CVD methods are often used in the semiconductor industries to deposit a large range of thin films.

CVD is a popular technique compared to other vacuum deposition methods due to its low equipment costs and affordable operating expenses for films and coatings of metals, insulators and semiconductors. CVD is able to deposit materials in various morphologies, such as epitaxial, polycrystalline and amorphous films. Furthermore CVD processes have the unique capabilities to enable surface-selective deposition and uniformly coat structures with very high aspect ratios.[10][20]

11

There are 3 main formats of CVD each operating at a different pressure. Atmospheric pressure CVD (APCVD) is a variant of CVD that deposits at atmospheric pressure. Low-pressure CVD (LPCVD) operates at sub-atmospheric pressures in the range of 5-20 Torr to reduce unwanted reactions in the gas-phase and for increased film uniformity across the wafer substrates. Ultrahigh vacuum CVD (UHVCVD) is CVD that operates at very low pressure, often in the order of 10<sup>-8</sup> Torr. Plasma-Enhanced CVD (PECVD) enhances the rate of CVD reactions at lower temperatures by placing the substrate in the plasma discharge region.[10]

#### 1.3.3 Direct Liquid Evaporation Chemical Vapor Deposition

Direct liquid evaporation chemical vapor deposition (DLE-CVD) is a promising and attractive deposition technique that has widespread applications to a large variety of pressures and is especially effective in leveraging CVD precursors having low vapor pressures. [21]

Organometallic CVD precursors typically have low vapor pressures of under 1 Torr at room temperature but high vapor pressures are needed to deposit high quality films with high conformity and high growth rates. However, the high temperatures needed to achieve sufficient vapor pressures for use with conventional CVD bubblers can result in thermal decomposition of those precursors that lack the necessary thermal stability. This gives rise to the incorporation of impurities in the film as well as non-uniformity in the deposited films.

DLE-CVD solves the challenging problem of avoiding premature thermal decomposition when using precursors with low vapor pressures at elevated temperatures. In a DLE-CVD setup, the CVD precursor is dissolved in a solvent that is chemically insert. Small amounts of liquid are precisely delivered into a long heated spiral length of vaporizer tubing for full vaporization of the liquid droplets. A carrier gas is used to transport these vaporized chemicals for mixing with the co-reactants before they are injected into the reaction chamber for deposition on the substrate.[13]

#### 1.4 Overview of Thin Film Characterization

#### 1.4.1 Thickness and Structural Characterization

Atomic force microscopy (AFM) is used to investigate the surface morphology of thin films. It is a ultra-high resolution variant of the scanning probe microscopy (SPM) with sub-nanometer resolution. The AFM system has a tiny and sharp mechanical probe that measures the forces acting between this probe and the surface of the sample being measured using the reflection of a laser spot off the top surface of the AFM cantilever tip.[22]

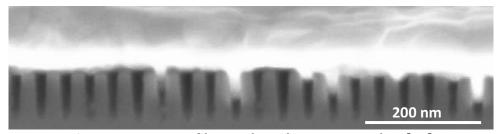

Scanning electron microscopy (SEM) is used to measure the thickness of thin films with thicknesses that are much larger than tens of nanometers, to analyze the surface morphology of the films as well as to inspect the step coverage of thin films on high aspect ratio (AR) features. SEM is a variant of the electron microscope that injects a focused beam of electrons at the surface of the sample, and measures how the incident electrons interact with the atoms on sample's surface, giving us high-resolution images of the sample's surface topology, electrical resistivity and composition. SEM is commonly employed for both top-view and cross-sectional analyses due to the ease of their sample preparation.[23]

Transmission electron microscopy (TEM) is a ultra-high resolution electron microscopy technique. TEM is similar to SEM in many ways, and it shoots a beam of electrons through an ultra-thin sample that has been specially prepared to this thickness. The electrons interact with the specimen producing an image with resolution with an order of magnitude higher than that

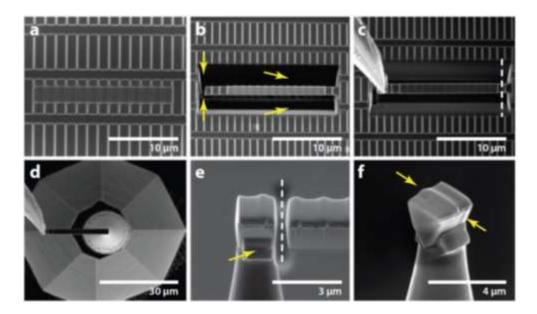

of the SEM. This image is projected onto an imaging device such as a CCD camera. There are two main methods of preparing a sample for cross-sectional TEM analysis.[24] The first method involves placing 2 identical samples together facing each other mechanical polishing to thin them down, followed by ion milling to the desired thickness that is transparent to the incoming electron beam. The second method involves using the focused ion beam (FOB) where the target region to be extracted is coated with a layer of protecting material, after which a wedge of the material is milled out using the FIB system.[25] This FIB'ed wedge is then held in place on a TEM grid with a thin layer of metal deposition. Finally, the wedged sample is thinned further to about a micron in thickness.

#### 1.4.2 Chemical Characterization

X-ray photoelectron spectroscopy (XPS) is a surface analysis spectroscopic technique that measures the elemental composition, chemical state, empirical formula and electronic state of the elements in a specimen. A beam X-rays is generated and focused on a micro-sized spot on the sample being measured. The irradiated x-ray excites the electrons in the various orbitals of the material, causing some electrons to be excited and emitted from the surface of the materials as photoelectrons. The photoelectrons are then collected by a detector where the kinetic energies of the collected particles are measured, producing the XPS spectrum. Since we know the energy of a particular X-ray wavelength (E<sub>photon</sub>), we are able to calculate the binding energy of these electrons

$$E_{binding} = E_{photon} - (E_{kinetic} + \phi)$$

where  $E_{kinetic}$  is the kinetic energy of the photo electron measured by the XPS detector, and  $\phi$  is the work function of the spectrometer.[26]

Rutherford backscattering spectroscopy (RBS) is a characterization technique that is used to determine the structure and composition of thin films by impinging a beam of high energy ions on the specimen and measuring the backscattering of this beam. Rutherford backscattering involves the elastic collision of a high kinetic energy particle from the incident beam to a stationary particle on the sample. By the law of conservation of energy and momentum, the energy  $E_1$  of the backscattered projectile is reduced from the initial energy  $E_0$ :[27]

$$E_1 = k.E_0$$

where k is the kinematic factor

$$k = \left(\frac{m1\cos\theta \pm \sqrt{m_2^2 - m_1^2(\sin\theta_1)^2}}{m1 + m2}\right)^2$$

Energy-dispersive X-ray spectroscopy (EDX) is a characterization technique for doing elemental analysis or chemical characterization of a sample. It uses a high-energy beam of electrons, protons or X-rays to excite an electron in the ground state in an inner shell, ejecting it to create an electron hole pair.[28] This causes a higher energy in an outer, higher energy shell to relax down to fill the newly created hole. This difference in energy between the higher energy shell and the lower energy shell may result in the emission of X-rays, which are measured by an energy-dispersive spectrometer and the elemental composition of the sample is determined based on how energies of X-rays are characteristic of the difference in energy between the two shells and the specimen's atomic structure.

#### 1.4.3 Atom Probe Tomography

#### 1.4.3.1 Unique features of the Atom Probe Tomography

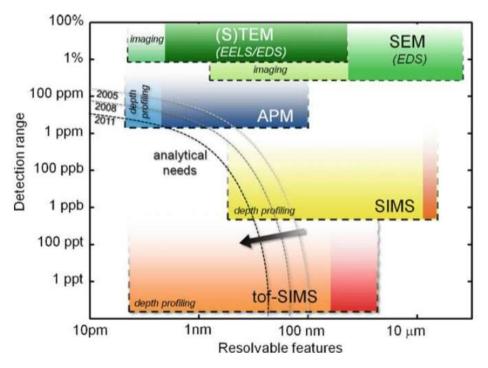

Atom Probe Tomography (APT) is an extremely high resolution analysis technique for characterizing materials, providing unique data in both the atomic structure and the chemical composition of the specimen, making APT a highly complementary technique to the various forms of electron microscopy. APT has the unique ability to construct three-dimensional models of the chemical composition of the specimen at an atomic scale, with a resolution of under 3 angstroms in all 3 dimensions with an analytical sensitivity of up to 10 ppm. This makes APT an excellent method to investigate features located beneath the surface of the specimen, not limited to dislocations, two-dimensional features (including interfaces and layered structures) and three-dimensional features (such as precipitates).[29]

In addition to its unmatched spatial resolution and high analytical sensitivity, APT poses several distinct advantages not seen in other analytical instruments. The detection efficiency of APT is very high at over 50%. It is also capable of detecting all elements with the same efficiency due

to having a time-of-flight (TOF) mass spectrometer and microchannel plates (MCPs) being equally sensitive to all elements. Furthermore, no prior knowledge of the composition is needed.[29]

#### 1.4.3.2 Fundamentals of the Atom Probe Tomography

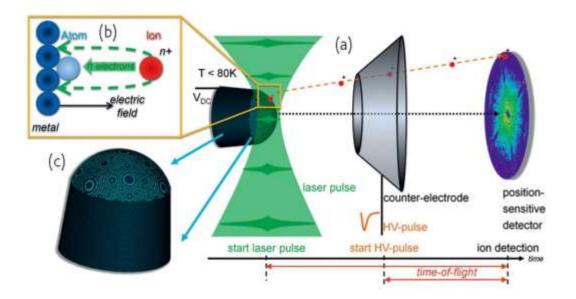

Field evaporation is the effect exploited by APT where a very strong electric field is applied to the specimen for the field-induced removal of atoms from the specimen's surface. This electric field, created using either a standing (DC) electrostatic field combined with either a high voltage (HV) field or a sequence of laser pulses, is able to ionize the surface atoms with single or multiple charges causing it to desorb from the surface.[29]

The removed ions are pulled towards a reflection compensator configuration which straightens the curved trajectory of these ions towards a position-sensitive detector, which collects them and measures their impact positions. TOF measurements of individual ions are made possible due to the pulsing of the high voltages or laser pulses, which is used to determine the mass to charge ratio for the identification of the elements corresponding to each collected ions. These processes can be seen schematically in Figure 1.5

18

Figure 1.5 (a) Schematics of the atom probe tomography process. (b) An illustration of the field evaporation process. (c) An example of a 3D representation of the specimen. The regions shaded in light blue represent atoms protruding from the specimen, and these patterns represent the crystal structure of the specimen. [29]

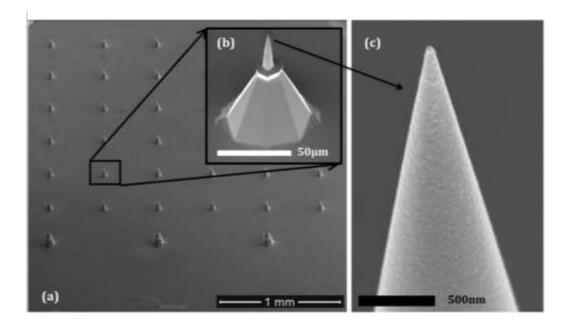

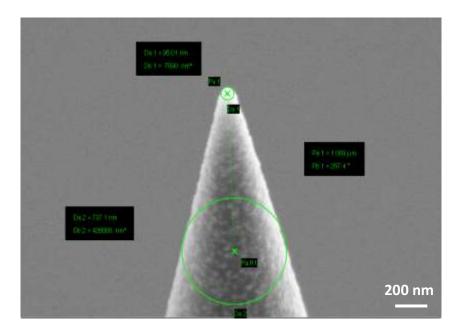

Before the specimen is ready for field evaporation of surface atoms, it must first be sharpened into a sharp tip with a radius of curvature between 50 to 150 nm as well as a sharp shank angle of usually under 20 degrees in order to achieve the desired evaporation field. The surface electric field can be estimated with

$$F = \frac{V}{k_f R}$$

where *F* is the induced electric field at the apex of the sharpened tip, *R* is the radius of curvature of this tip,  $k_f$  is the field factor which is also known as the field reduction factor (a constant that is characteristic of the shape of the tip and the electrostatic environment the tip resides in).

The cone shape geometry of the sharpened tip allows a highly magnified projection in the order of 10<sup>6</sup> using the resulting highly divergent electric field. This allows atoms 0.2 nm apart on the surface of the specimen to strike the detector with a separation of 0.2 mm, allowing this measurement to be made with high precision and ease. Furthermore, the specimen is cooled down to cryogenic temperatures to reduce surface diffusion of the specimen's atoms, increasing the spatial resolution even more. A reverse-projection algorithm is used to reconstruct a 3D atomically resolved tomographic structure of the analyzed volume of the specimen using the positions of the atoms collected by the detector.[29]

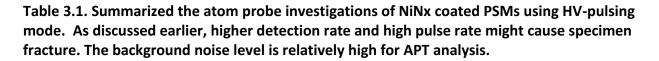

APT is able to operate using either HV pulses or laser pulses. Using HV pulses involve an electric field created from the combination of a standing DC voltage and HV pulses. This requires the specimen to be sufficiently conductive (with a electrical conductivity greater than 10<sup>2</sup> S cm<sup>4</sup>). As a result, this limits the use of HV pulses to typically metallic samples. Optimizations have to be made for the standing voltage, the specimen temperature and the pulse fraction for each specimen such that there is no preferential evaporation of the elements experiencing the lowest electric field and simultaneously avoid the evaporation of atoms by field evaporation due to just the standing voltage only. The pulse fraction is defined as the ratio of the HV pulse amplitude to the DC standing voltage.[29]

The alternative pulsing mode is the laser pulsing mode. This method uses laser pulses in the picosecond and femtosecond ranges for inducing field evaporation on the apex of the specimen

tip. Unlike the HV pulses, laser pulses allow insulating materials to be analyzed without too many specimen failures. This makes it suitable for characterizing specimens comprised of semiconductors, organic compounds, ceramics and bio minerals. Because the energy of laser pulses is hard to vary compared to the pulse duration, the pulse fraction is varied as the DC voltage changes, as opposed to the case of the HV-pulsing mode.[30]

APT exercises very precise control over the pulsed field evaporation by having tight control over the HV and laser pulsing. This enables it to accurately control the precise moment an ion is ejected from the surface of the tip, allowing the instrument to measure the TOF of the ion, defined as the time between the pulse application and the time the ejected particle is measured by the detector. The mass-to-charge ratio m/n of the ion is related to the TOF by the formula

$$\frac{m}{n} = \frac{2eV}{v^2} = \frac{2eV}{d^2}t^2$$

Where *m* is the mass of the atom, v = d/t is the velocity of the atom, *d* is the distance o separation between the specimen and the detector, and *t* is the time of flight. The potential energy of the surface atom due to the electric field, *neV*, is convered to kinetic energy  $\frac{1}{2}mv^2$ .[30]

The highly accurate measurement of the TOF of the evaporated atoms allows for the elemental identification of these detected ions. Coupled with the location data of each detected ions, the

final compositional mapping of the specimen volume can be reconstructed in 3-dimensions with atomic scale resolution using APT.

#### 1.4.3.3 Limitations of the Atom Probe Tomography

APT analysis requires tremendous skill and experience to operate as the number of successful specimen runs is highly dependent on it. Fracturing of specimen is a typical problem during APT analysis. This can be a result of the high mechanical stresses on the specimen at the apex region when they approach the cohesive strength of the material. This prevents sufficient data to be collected during the experiment. The efficiency of ion collections is greatly limited to under 60% of incident atoms due to the area on the MCPs that are open for them. Specimens with complex structures also serve to be challenging as a high degree of distortion can be introduced into the 3D reconstructed images. The volume being analyzed is also limited by the field of view of the spatial detector, resulting in data sets 100 nm in diameter and 100 nm in depth, which gives a volume of  $10^6$  nm<sup>3</sup> and  $10^7$ - $10^8$  atoms. Such a run will require 17 hours of collection time based on an optimistic collection rate of  $10^6$  atoms/min.[31]

| Table 1.1. Summary of Major Chem | nical Characterization Techniques |

|----------------------------------|-----------------------------------|

|----------------------------------|-----------------------------------|

| Method  | Primary               | Detected                | Elemental               | Detection  | Lateral         | Effective      |

|---------|-----------------------|-------------------------|-------------------------|------------|-----------------|----------------|

|         | Beam                  | Signals                 | Sensitivity             | Limit      | Resolution      | Probe<br>Depth |

| APT/APM | -                     | lons                    | H-U                     | ~ few ppm  | 0.3 – 0.5<br>nm | ~1-3Å          |

| EDS     | Electron              | Characteristic<br>X-ray | Na –U                   | ~ 0.1%     | ~ 1 µm          | ~ 1 µm         |

| RBS     | He+ ions              | Backscattered ions      | He-U                    | ~ 0.1%     | ~ 1 µm          | ~ 4 μm         |

| SIMS    | $Cs^+, O_2^-$<br>ions | Secondary ions          | H-U                     | > 0.1 ppm  | ~ 1 µm          | ~ 15 Å         |

| XPS     | X-ray or<br>UV        | Photoelectrons          | Li-U                    | ~ 0.1 – 1% | ~ 100 µm        | 5 - 15 Å       |

| XRD     | X-ray                 | Diffracted X-<br>ray    | Crystalline<br>Material | 5%         | > 1 µm          | > 1 µm         |

Figure 1.6. Typical elemental sensitivity (detection range) and sparial resolution of common microscopy and microanalysis techniques. The dotted lines indicate imaging techniques ((S)TEM, SEM) or depth profiling (SIMS, APM). [30]

# Reference

- [1] S. Arpiainen, Integration of 2D and 3D nanostructure fabrication with wafer-scale microelectronics Photonic crystals and graphene Integration of 2D and 3D nanostructure fabrication with wafer-scale microelectronics Photonic crystals and graphene.

- J. U. Knickerbocker, P. S. Andry, B. Dang, R. R. Horton, C. S. Patel, R. J. Polastre, K. Sakuma, E. S. Sprogis, C. K. Tsang, B. C. Webb, and S. L. Wright, "3D silicon integration," *Proc. Electron. Components Technol. Conf.*, no. December, pp. 538–543, 2008.

- [3] T. Wafers, F. Flip, and C. Applications, "(12 > UllIted States Patent USING THROUGH SILICON VIAS AND," vol. 2, no. 16, 2005.

- [4] J. Q. Lu, "3-D hyperintegration and packaging technologies for micro-nano systems," *Proc. IEEE*, vol. 97, no. 1, pp. 18–30, 2009.

- [5] Y. Au, Q. Min Wang, H. Li, J.-S. M. Lehn, D. V. Shenai, and R. G. Gordon, "Vapor Deposition of Highly Conformal Copper Seed Layers for Plating Through-Silicon Vias (TSVs)," J. Electrochem. Soc., vol. 159, no. 6, p. D382, 2012.

- [6] C. Krauss, S. Labat, S. Escoubas, O. Thomas, S. Carniello, J. Teva, and F. Schrank, "Stress measurements in tungsten coated through silicon vias for 3D integration," *Thin Solid Films*, vol. 530, pp. 91–95, 2013.

- [7] D. Hisamoto, W. C. Lee, J. Kedzierski, H. Takeuchi, K. Asano, C. Kuo, E. Anderson, T. J. King, F. Jeffrey Bokor, and C. Hu, "FinFET-A self-aligned double-gate MOSFET scalable to 20 nm," *IEEE Trans. Electron Devices*, vol. 47, no. 12, pp. 2320–2325, 2000.

- [8] M. Stoppa and A. Chiolerio, "Wearable electronics and smart textiles: A critical review," *Sensors (Switzerland)*, vol. 14, no. 7, pp. 11957–11992, 2014.

- [9] J. Singh, F. Quli, D. E. Wolfe, and J. Schriempf, "An Overview: Electron Beam-Physical Vapor Deposition Technology-Present and Future Applications," *Surf. Eng. Sci. Technol. 1*, pp. 59–74, 1999.

- [10] A. C. Jones and M. L. Hitchman, "Overview of Chemical Vapour Deposition," *Chem. Vap. Depos. Precursors, Process. Appl.*, pp. 1–36, 2009.

- [11] Y. Au, Y. Lin, and R. G. Gordon, "Filling Narrow Trenches by Iodine-Catalyzed CVD of Copper and Manganese on Manganese Nitride Barrier/Adhesion Layers," J. Electrochem. Soc., vol. 158, no. 5, p. D248, 2011.

- [12] M. Tinani, a. Mueller, Y. Gao, E. a. Irene, Y. Z. Hu, and S. P. Tay, "In situ real-time studies of nickel silicide phase formation," *J. Vac. Sci. Technol. B Microelectron. Nanom. Struct.*, vol. 19, no. 2, p. 376, 2001.

- [13] Z. Li, R. G. Gordon, H. Li, D. V. Shenai, and C. Lavoie, "Formation of Nickel Silicide from Direct-Liquid-Injection Chemical-Vapor-Deposited Nickel Nitride Films," J. Electrochem. Soc., vol. 157, no. 6, p. H679, 2010.

- [14] R. Civanlar, A. Eleftheriadis, and O. Shapiro, "United States Patent," 2009.

- [15] K. I. Choi, B. H. Kim, S. W. Lee, J. M. Lee, W. S. Song, G. H. Choi, U. Chung, and J. T. Moon, "Characteristics of ALD-TaN Thin Films Using," *leee*, pp. 129–131, 2003.

- [16] Z. Li, A. Rahtu, and R. G. Gordon, "Atomic Layer Deposition of Ultrathin Copper Metal Films from a Liquid Copper(I) Amidinate Precursor," J. Electrochem. Soc., vol. 153, no. 11, p. C787, 2006.

- [17] R. Gordon and J. Becker, "Vapor deposition of metal oxides and silicates: Possible gate insulators for future microelectronics," *Chem. ...*, no. 12, pp. 2463–2464, 2001.

- [18] N. Kaiser, "Review of the fundamentals of thin-film growth.," *Appl. Opt.*, vol. 41, no. 16, pp. 3053–3060, 2002.

- [19] J. A. Thornton, "Magnetron sputtering: basic physics and application to cylindrical magnetrons," *J. Vac. Sci. Technol.*, vol. 15, no. 2, pp. 171–177, 1978.

- [20] B. Potts and P. Mark, "(12) UllIted States Patent (10) Patent N0.: () Nonce : Assistant Examiner \* Anshu Bhatia US . Patent," vol. 1, no. 12, pp. 1–7, 2013.

- [21] T. Zumin, "United States Patent [ 19 ]," pp. 1–5, 1980.

- [22] G. Binnig and C. F. Quate, "Atomic Force Microscope," *Phys. Rev. Lett.*, vol. 56, no. 9, pp. 930–933, 1986.

- [23] T. Hideo and T. Otaka, "Scanning Electron Microscope," 1995.

- [24] H. P. Stevenson, A. M. Makhov, M. Calero, A. L. Edwards, O. B. Zeldin, I. I. Mathews, G. Lin, C. O. Barnes, H. Santamaria, T. M. Ross, S. M. Soltis, C. Khosla, V. Nagarajan, J. F. Conway, A. E. Cohen, and G. Calero, "Use of transmission electron microscopy to identify nanocrystals of challenging protein targets.," *Proc. Natl. Acad. Sci. U. S. A.*, vol. 111, no. 23, pp. 8470–5, 2014.

- [25] K. Kuroda, "Application of focused ion beam milling to cross-sectional TEM specimen preparation of industrial materials including heterointerfaces," *Thin Solid Films*, vol. 319, no. 1–2, pp. 92–96, 1998.

- [26] D. D. Sarma, P. K. Santra, S. Mukherjee, and A. Nag, "X-Ray Photoelectron Spectroscopy : A Unique Tool to Determine the Internal Heterostructure of Nanoparticles X-Ray Photoelectron Spectroscopy : A Unique Tool to Determine the Internal Heterostructure of Nanoparticles," 2013.

- [27] H. Hashimoto, A. Ohno, K. Nakajima, M. Suzuki, H. Tsuji, and K. Kimura, "Surface characterization of imidazolium ionic liquids by high-resolution Rutherford backscattering spectroscopy and X-ray photoelectron spectroscopy," *Surf. Sci.*, vol. 604, no. 3–4, pp. 464–469, 2010.

- [28] D. Nam, A. S. Opanasyuk, P. V. Koval, A. G. Ponomarev, A. R. Jeong, G. Y. Kim, W. Jo, and H. Cheong, "Composition variations in Cu2ZnSnSe4 thin films analyzed by X-ray diffraction, energy dispersive X-ray spectroscopy, particle induced X-ray emission, photoluminescence, and Raman spectroscopy," *Thin Solid Films*, vol. 562, pp. 109–113, 2014.

- [29] M. K. Miller, D. Larson, T. Prosa, R. Ulfig, B. Geiser, T. Kelly, and Imago, *Atom Probe Microscopy*, vol. 10, no. S02. 2013.

- [30] D. Larson, T. Prosa, R. Ulfig, B. Geiser, and T. Kelly, Local electrode atom probe tomography. 2013.

- [31] E. a. Marquis, "Atom probe tomography applied to the analysis of irradiated microstructures," J. Mater. Res., vol. 30, no. 09, pp. 1222–1230, 2015.

# Chapter 2 DLE-CVD Processes of nickel, manganese and copper-based thin films

# 2.1 Introduction

Direct liquid evaporation (DLE) is a very attractive deposition method, which can be applied to a wide range of precursors, especially ones that have low vapor pressure. DLE of suitable liquids or solutions can consistently deliver high vapor concentrations of precursors that are very difficult to achieve by the typical method involving vaporization of precursors from conventional bubblers.[32] Higher vapor concentrations enable the deposition of highly conformal films with high growth rates. In this chapter, DLE-CVD is used to deliver consistent and high vapor concentrations of nickel, manganese and copper precursors to coat structures with high aspect ratios for use in next-generation microelectronics interconnect applications.

Nickel nitride, manganese nitride and copper have been previously deposited by various means, including PVD, CVD and ALD methods.[13] As the advancement of microelectronic devices demands the rapid shrinkage of features in devices, highly conformal metal deposition is required for the ultra large scale integration (ULSI) fabrication of three dimensional structures. [33] The poor step coverage of PVD methods caused severe limitations in coating deep contact holes and ultra-small trenches. [34]CVD and ALD are thus ideal deposition methods for these devices as they are able to produce high-quality and conformal thin films that meet the high demands of these advanced semiconductor devices. [17]

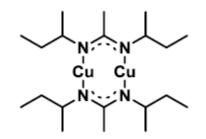

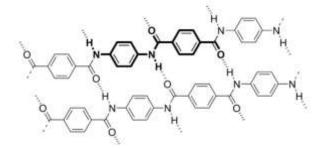

The thermal ALD NiNx process uses bis(N,N'-di-tert-butyl-acetamidinato)nickel(II) as the metal precursor and H<sub>2</sub> and NH<sub>3</sub> as the co-reactants, respectively. Successful depositions of high quality NiN<sub>x</sub> and Ni metal films have been achieved. The CVD process uses bis(N,N'diisopropylpentylamidinato) manganese (II) as the metal precursor and NH<sub>3</sub> as the co-reactant, achieving successful deposition of high quality manganese nitride at temperatures as low as 130°C. High quality copper films can also be achieved by CVD process with copper (N,N'-di-*sec*butylacetamidinate) dimer as the precursor and H<sub>2</sub> as the co-reactant. [35][36]

However, the growth rate of Ni metal using either ALD or CVD is too slow for many practical applications. In contrast, direct-liquid-injection (DLI-CVD) process provides a much faster growth rate. It has the advantage of being able to prevent early decomposition of the precursors compared to the traditional bubbler delivery since the precursor solution for a DLI-CVD system is typically stored at room temperature.[32] Furthermore, this technique can be applied to a wide range of precursors, especially for those having low vapor pressure and limited thermal stability. DLI-CVD can deliver high vapor concentration of precursors that are challenging conventional bubbler delivery to achieve, making it favorable for growing highly conformal films with high growth rates. DLI-CVD has been successfully employed for the deposition of Ni, Co, cobalt oxide, Ru, Cu and metal oxides. [32][13][5]The DLI-CVD method typically uses a nebulizer to break up the liquid solution into tiny droplets, which then generate vapor when the droplets are exposed to a hot carrier gas. However, the process still has obstacles to be widely used in the industry, since it produces small particles made up of non-volatile residues in the precursor after most of the precursor has evaporated. These particles

can be carried along with the vapor into the deposition region, where they can contaminate substrates. Particle contamination is a very serious problem in microelectronics manufacture industry. Particles can cause defects for thin film materials; also, they can accumulate in the narrow openings of nebulizer or block the liquid flow. [32]

We developed a direct-liquid-evaporation (DLE-CVD) process to avoid the obstacles of the DLI-CVD process. DLE vaporizes the precursor solution by flowing the liquid along the heated tubing coil inside the oven. It takes advantage of the faster heat transfer from a heated solid tube to the flowing liquid than the slower heat transfer from the heated carrier gas to the liquid droplets. Even if any non-volatile residue is left behind by DLE process, the residue tends to adhere to the bottom of the tube where it remains instead of being carried into the reactor. The tubing does not become clogged or blocked. Our DLE systems have demonstrated steady, reproducible performance for years without the need to replace the tubing oils.

The choice of a suitable precursor and its solvent is crucial for obtaining high quality films via the DLE-CVD process. The precursor requires a reasonable volatility and high decomposition temperatures.[32][13][37] Both the solubility of precursor and vaporization rate is crucial when deciding on a suitable solvent. The solubility of precursor should be high enough in the solvent to ensure a sufficient supply of precursor during the deposition. The vaporization rate of solvent must be similar to that of the precursor; if the solvent evaporates more quickly than the solid precursor, the precursor residue will block the vaporizer. In this chapter, bis(N, N'-di-tert-butyl-acetamidinato)nickel(II), copper (N, N'-di-sec-butylacetamidinate) dimer, bis(N, N'-di-tert-butyl-acetamidinato)nickel(II), copper (N, N'-di-sec-butylacetamidinate) dimer, bis(N, N'-di-tert-butyl-acetamidinato)nickel(II), copper (N, N'-di-sec-butylacetamidinate) dimer, bis(N, N'-di-tert-butyl-acetamidinate) butyl-acetamidinato)manganese(II) are selected as the precursors for nickel, manganese, copper based thin film deposition. Tetradecane and trihexyamine are chosen for the solvents. We investigated the impact of different processing parameters and found optimal conditions for producing highly-conformal, high-quality nickel, manganese and copper-based thin films using DLE-CVD processes.

#### **2.2 Experiments**

#### 2.2.1 Metal Amidinate Precursors

CVD and ALD precursors need to be highly reactive toward the surfaces of substrates and to the surface prepared by a complementary precursor such as  $H_2O$ ,  $NH_3$ , or  $H_2$ . These compounds must also be volatile and thermally stable at the desired growth temperatures, and the reaction byproducts should be nonreactive and noncorrosive. CVD precursor chemistry has been dominated by halides, alkoxides,  $\beta$  -diketonates, alkyls, and cyclopentadienyl derivatives. [38] Alkylamide precursors have attracted more attention in recent years because these compounds do not have M-C bonds, resulting in minimal carbon incorporation in the deposited films, and the lower M-N bond strengths as compared to those of the M-Cl and M-O bonds allow depositions to occur at relatively low temperatures. These amide derivatives produce no corrosive byproducts, unlike metal halides. Metal amidinates are alternatives to alkylamides. [39] The amidinate ligand can provide volatile metal amidinate compounds. The bidentate chelating effect, on the other hand, should increase the thermal stability of resulting metal

compounds. In this thesis, we study the DLE-CVD of nickel, manganese and copper thin films using metal amidinates precursor.

# 2.2.2Precursor Chemistry in DLE-CVD of nickel, manganese and copper-based thin film

# The Nickel precursor

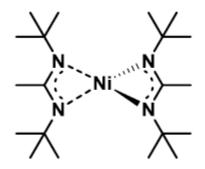

The nickel precursor, bis(N,N'-di-tert-butylacetamidinato)nickel(II) [38], is a dark brown, airsensitive crystalline solid that melts at a temperature of 87 °C. This liquid precursor has a vapor pressure of ~200 mTorr at 90 °C and ~320 mTorr at 120 °C.

Fig 2.1. bis(N,N<sup>'</sup>-di-tert-butylacetamidinato)nickel(II) Molecular Structure

# The Manganese Precursor

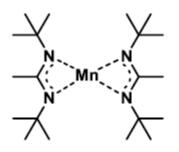

The manganese precursor, bis(N,N'-di-tert-butylacetamidinato)manganese(II)[38], is a dark yellow, super air-sensitive crystalline solid that melts at a temperature of 106 °C. This liquid precursor has a vapor pressure of ~52 mTorr at 100 °C

Fig 2.2. bis(N,N<sup>'</sup>-di-tert-butylacetamidinato)manganese(II) Molecular Structure

# **The Copper Precursor**

The copper precursor, copper (N,N'-di-*sec*-butylacetamidinate) dimer[35] is bright white, air sensitive crystalline solid that melts at a temperature of 75 °C. The liquid precursor has a vapor pressure of ~187.5 mTorr at 95 °C.

Fig 2.3. Copper (N,N<sup>'</sup>-di-sec-butylacetamidinate) dimer Molecular Structure

# 2.2.3 Choices of Solvents

There are several requirements for choosing the solvent:[37]

- The solvent should be inert. The precursors must be soluble and stable for long periods in the specific solvent, and must not react with the solvent.

- 2. The solvent should have a vapor pressure similar to the precursor

In the case of ternary oxides, as multiple precursors co-exist in the solvent they should not react with each other. Co-precursors should evaporate at similar temperatures. Otherwise it will be difficult to control the composition of complex oxides.

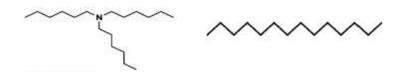

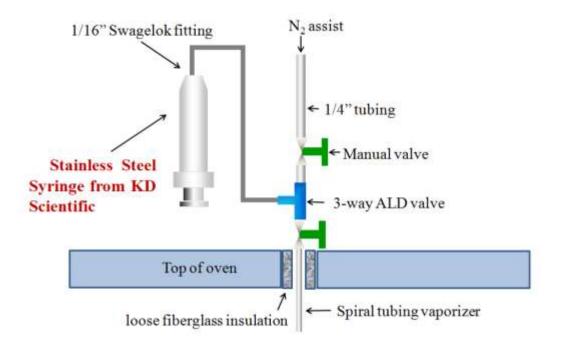

In this paper, trihexylamine and tetradecane are chosen as the solvent of copper, manganese, Nickle precursors. In Fig. 2.5, The Thermal Gravimetric Analysis (TGA) of copper, manganese amidinate and Trihexylamine shows their volatilities are quite similar.

Trihexylamine Boiling Point 265 °C Tetradecane Boiling point 253 °C

Fig2.4. The Molecular Structure of Trihexylamine and Tetradecane

Figure 2.5. Thermal Gravimetric Analyses of Cu and Mn amidinates and Trihexylamine

The nickel, manganese and copper precursor solutions were prepared in a glovebox. The precursor solution is finally transferred into containers inside the glove box. Manganese and copper precursors were then injected into the chamber through their respective evaporation loops. These precursor vapor flows were mixed together with 100 sccm of hydrogen at a temperature of 180 - 200 °C and a pressure of 5 Torr.

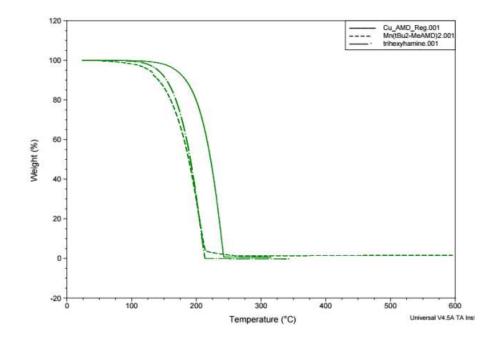

#### 2.2.4 DLE CVD Reactor Setup

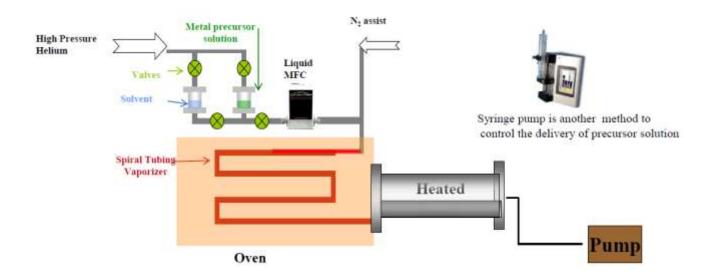

Figure 2.6 shows the schematic diagram of the home-made syringe based DLE-CVD system. Common glass syringes do not have fittings that have tight seals; thus oxygen or water in the air can diffuse into the precursor solution through these leakage paths fairly easily. To overcome this problem, a stainless steel syringe (KD Scientific) with a 1/16" Swagelok fitting connection was used. The stainless steel syringe was controlled by an infusion/withdrawal syringe pump (KD Scientific, Model #KDS210). The syringe was positioned vertically in order to expel out any trapped gas bubble inside the syringe, which might cause inconsistent flow of the liquid solution. Two manual valves were added in order to avoid the air exposure to the 2-way ALD valve during bubbler refill.

33

Figure 2.6. Schematic diagram of our DLE-CVD system.[37]

Figure.2.7 shows a schematic diagram of our DLE-CVD system for manganese based film deposition. The Mn precursor bubbler has a rounded glass viewport in the middle for performing visual checks on the current level of the precursor solution. The top of the bubbler is under a high pressure N<sub>2</sub> ambient, which serves as the driving force for the liquid flow. The flow rate of the liquid solution is controlled by a liquid mass flow controller (Brooks Instrument), which ranges from 0.05 to 1 sccm. The small amount of liquid delivered is assisted with 60 sccm N<sub>2</sub> gas flow to enter into the oven, which is kept at 150 °C. Lower temperatures could cause incomplete vaporization of the liquid droplets and hereafter the clogging of the flow path. After the liquid enters the oven, it travels through a long (3-4 meters) spiral tubing, which serves as a robust and reliable, low-cost thermal vaporizer for the complete vaporization of the liquid. The vapors of the metal precursors mix with the co-reactant gases right before

entering the reaction chamber. The reaction chamber was kept at 160 to 200°C during the deposition. Another bubbler filled with toluene is connected in parallel with the Ni precursor bubbler for the clean-up of the flow paths before their exposure to the air during the process of refilling the precursor. The liquid mass flow controller used in the system is relatively expensive. The inner flow path of the liquid MFC is very delicate; small particles, either from the ambient or formed by the trapped precursor due to the air exposure during precursor refill could readily clog up the inner flow paths.

Figure 2.7. Schematic diagram of the reactant flow paths in a DLE-CVD system.

# 2.2.5 Characterization Methods

The sheet resistance of the as-deposited films on silicon oxide was measured by a four point probe station (Veeco Instruments; Model FPP-5000). The physical thickness of the film was measured by Field Emission Scanning Electron Microscope (FESEM; Zeiss FESEM Ultra Plus). The relative amount of metal deposited was measured by the X-ray fluorescence (XRF). The

crystalline phases were evaluated by transmission electron microscopy (TEM; JEOL 2100 TEM system). Depth profiling using X-ray photoelectron spectroscopy (XPS; ESCA Model SSX-110) was used to study the elemental composition. The surface roughness of the films was evaluated by atomic force microscopy (AFM; Asylum MFP-3D AFM system).

# 2.3 Results and Discussion

# 2.3.1 DLE CVD Process of Nickel Nitride thin films and conversion to Nickel Silicide

As mentioned previously, thermal ALD of NiN<sub>x</sub> using Ni(ipr-AMD)<sub>2</sub> and H<sub>2</sub> or NH<sub>3</sub> as a coreactant was reported by several groups. However, the growth temperature is relatively high (above 250 °C), and the growth rate is slow (< 0.5 A/cycle). In this Chapter, we discuss about the low temperature deposition of DLE-CVD of nickel nitride and nickel metal at substrate temperatures of as low as 160 °C with NH<sub>3</sub> and H<sub>2</sub>. Nickel film can be converted to nickel silicide film at 470 °C.

When using  $NH_3$  as the only co-reactant, the films contain substantial amounts of nitrogen. The XPS depth-profile in Figure 2.8 showed significant N (~20%) in the nickel nitride films.

When using  $H_2$  as the only co-reactant for the DLE-CVD nickel deposition, the growth rate is very slow at 200 °C or lower.

When  $H_2$  is used as a co-reactant along with  $NH_3$  in the process, significantly less carbon and nitrogen is incorporated in the film. For the films deposited using both  $NH_3$  and  $H_2$ , XPS depth profile studies revealed less than 2% of C and O impurities inside the film regardless of the feed ratio of the two co-reactants. Furthermore, N content is lowered to less than 5%.

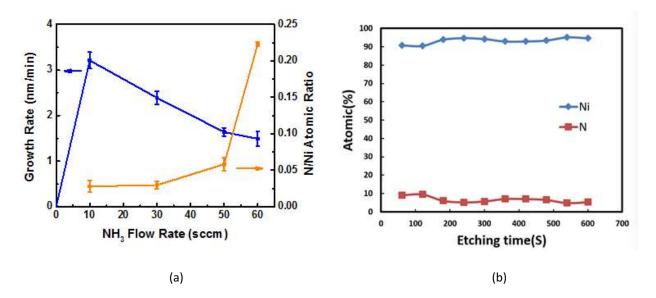

When NH<sub>3</sub> is used in addition to H<sub>2</sub> in the process, it significantly promotes the growth of nickel metal at the low temperature of 160 °C. Shimogaki and Gordon calculated the activation energy of different reactive pathways using the nickel amidinate precursor with and without NH<sub>3</sub>, and found that NH<sub>3</sub> was effective at speeding up the deposition rate.[40] Our experiments also agreed with this result. With 10 sccm of NH<sub>3</sub> and 50 sccm of H<sub>2</sub> the growth rate at 160 °C reached 3 nm/min. In contrast, no film is deposited when no NH<sub>3</sub> is used. This suggests that the NH<sub>3</sub> adsorbed on the substrate surface encouraged the chemisorption of the cobalt amidinate precursor by reaction with the NH bonds on the surface. As shown in the Fig 2.9, the deposition rate decreases as the fraction of NH<sub>3</sub> increases in the reactant gas composition. Also the C and O impurities are undetectable in the XPS depth profile when NH<sub>3</sub> and H<sub>2</sub> are 10 sccm and 50 sccm in the reactant gas. These conditions are the optimized conditions that we use in the nickel nitride deposition.

Figure 2.9 (a) Growth rate and N/Ni atomic ratio plotted versus the  $NH_3$  flow rate used during DLE-CVD process (keeping  $NH_3 + H_2$  total flow rate as 60 sccm); (b) XPS depth profile of the Ni film deposited by optimized conditions (10 sccm  $NH_3$  and 50 sccm  $H_2$  as co-reactant).

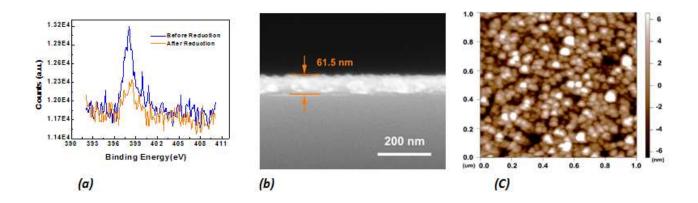

The 5% N can be further reduced by annealing the as-deposited nickel nitride with 10 sccm  $NH_3$ and 50 sccm  $H_2$  in  $H_2$  atmosphere at 160 °C without air-break after the DLE-CVD process. According to the N1s XPS spectra of the sputtered nickel nitride films (500 eV Ar+ sputtering for 480s to remove surface contaminations), the N content of Ni film is further reduced to below 0.9 at.%. To investigate the morphology of the Ni film, cross-section SEM and surface AFM images are presented in Fig.2.10, showing a thickness of 61.5 nm (20 mins deposition time) and a RMS value of 3.5nm.

# Figure 2.10. (a) N1s XPS spectrum of samples before and after reduction under H<sub>2</sub>, showing anitrogen content drop;(b)The cross section SEM image of DLE-CVD Ni film;(c) Taping-mode AFM image on the surface of Ni film.

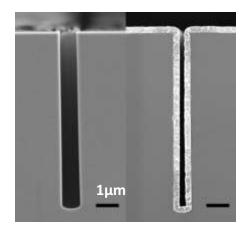

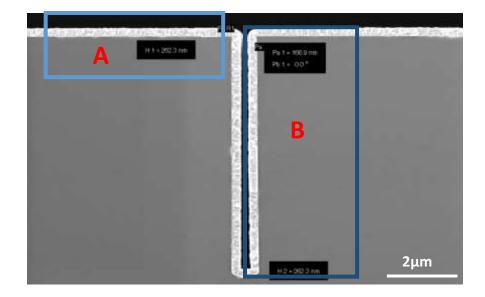

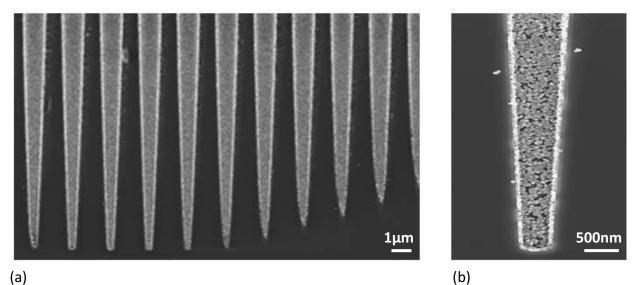

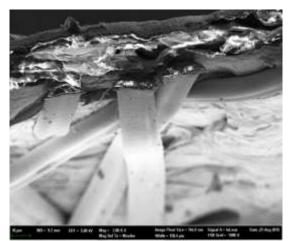

A ~40 nm thick nickel film inside a trench with aspect ratio of > 50:1 is shown in Figure 2.11. The thickness of the film at the bottom of the hole is equal to that on the top and the middle, confirming the good step coverage of DLE-CVD Nickle CVD process at 160 C with  $NH_3$  10 sccm and  $H_2$  50 sccm.

Figure 2.11. Cross-section SEM images of the Ni-coated trench sample.

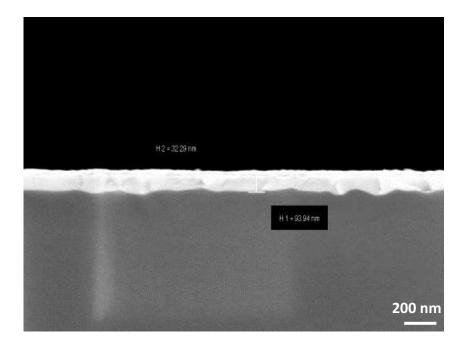

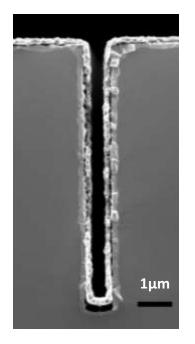

The Ni-coated trench sample was annealed in N<sub>2</sub> at 470  $^{\circ}$ C for 3 min, during which Ni silicide was formed at the interface between Ni and Si. The cross-section SEM of the same region shown in Fig. 2.12. Based on the image, approximately 93 nm Ni silicide is formed at the interface and about 32 nm of Ni residue is left on top of Ni Silicide.

Figure 2.12. Cross-section SEM images of the nickel silicide sample.

# 2.3.2 DLE CVD Process of manganese Nitride and copper Thin films

Manganese Nitride

In this chapter, by DLE-CVD method, smooth and low resistance manganese nitride with excellent conformality in a very wide range of temperature window from 130  $^{\circ}$ C to 300  $^{\circ}$ C.

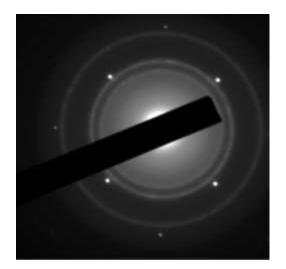

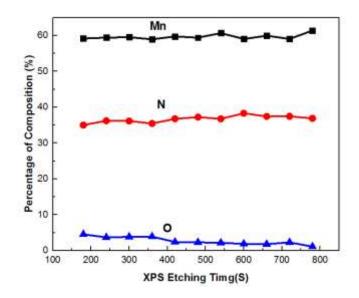

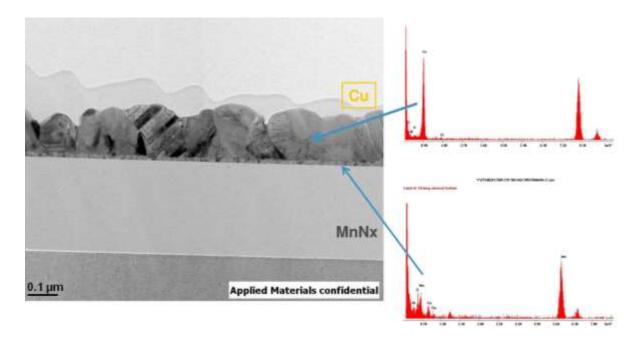

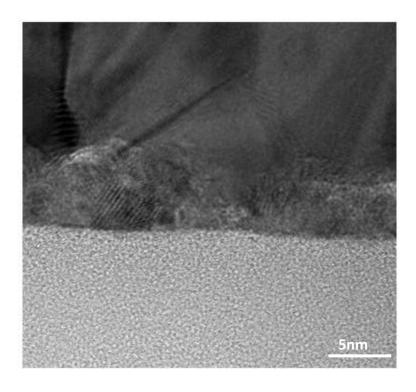

To deposit manganese nitride, ammonia was used as the only co-reactant gas, flowing at 60 sccm, combined with 5 g/h of precursor solution and 60 sccm of N<sub>2</sub> carrier gas. TEM and XRD measurements determined that the as-deposited manganese Nitride is in the phase of  $Mn_3N_2$  as shown in Fig 2.13. The TEM sample is  $MnN_x$  film as deposited on the  $SiN_x$  TEM grid with DLE-CVD process at 160 °C. The diffraction rings correspond to hexagonal  $Mn_3N_2$  (103), (110), (200). The XPS depth-profile in Fig 2.13 also showed significant N content (~35 at%) in the manganese nitride film. In addition, C was not detected by XPS inside the film since the film has less than about 1% of C which is under the detection limit of the XPS system. O was detected by XPS inside the film to be around 1.5% at.% of the film, this is probably a result of O having diffused into the film during the sample transfer from the reactor to the XPS chamber.

| d (A) | $Mn_{3}N_{2}$ (d) | Index |

|-------|-------------------|-------|

| 2.43  | 2.40              | 103   |

| 2.12  | 2.10              | 110   |

| 1.47  | 1.48              | 200   |

Figure 2.13. TEM diffraction pattern on Mn<sub>3</sub>N<sub>2</sub> (left) and their corresponding lattice spacing values calculated and compared to literature values (right).

Figure 2.14. Elemental composition of the  $Mn_3N_2$  film recorded during the XPS depth profile measurement.

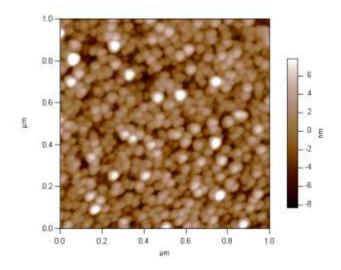

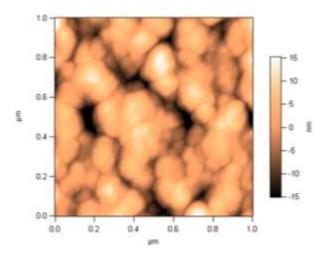

The surface morphology of a manganese nitride film was examined using the AFM and found to

be smooth with a roughness of approximately 8%.

Fig2.15. Tapping-mode AFM image on the surface of Ni film

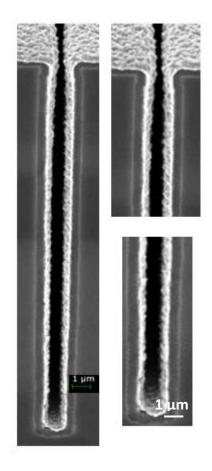

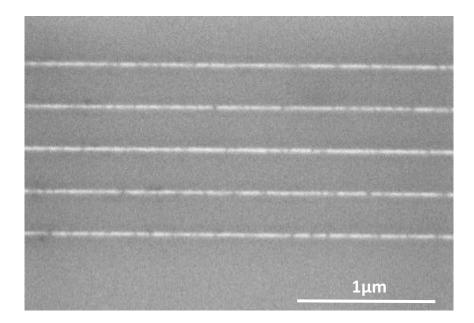

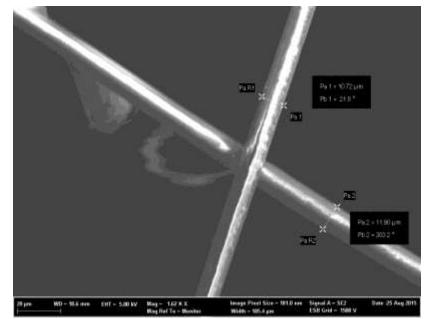

The step coverage of DLE-CVD MnN<sub>x</sub> for different growth conditions was examined by depositing MnN<sub>x</sub> on a silicon substrate containing holes with high aspect ratios. Then the coated substrate was hand cleaved to study the cross-section of the holes. The cross sectional SEM images in Fig. 2.16 shows MnN<sub>x</sub> film deposited conformally inside a hole with aspect ratio of 48:1 (170 nm diameter and 8 um depth) obtained from Tokyo Electronics. The MnN<sub>x</sub> film at the top, side wall and bottom of the feature are almost the same, showing nearly 100% step coverage.

Figure 2.16. Cross-section SEM images of manganese nitride inside a hole

#### **Growth Rate**

The delivery rate of manganese precursor solution and temperature are the two most important factors that determine the growth rate of MnN<sub>x</sub>.

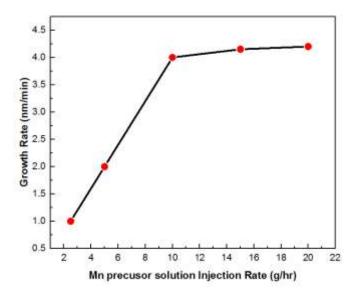

#### Impact of the delivery rate

The delivery rate of the manganese precursor solution was varied to investigate whether the deposition rate has achieved saturation. MnN<sub>x</sub> films were deposited at 160 °C with the conditions of 60 sccm of NH<sub>3</sub>, maintained at 5 torr on a thermal oxide substrate for 20 minutes. The manganese precursor solution was delivered at rates from 2.5 g/hr to 20 g/hr. Figure 2.16 shows the deposition rate of DLE-CVD as a function of cobalt precursor solution delivery rate. The deposition rate is almost saturated at the precursor solution delivery rate of 10g/hr. Increasing the manganese precursor delivery did not result to higher MnN<sub>x</sub> growth rates.

Figure 2.17. Delivery rate of manganese precursor solution and the resulting growth rate of MnN<sub>x</sub>.

#### **Temperature-dependence of Growth Rate**

#### Manganese Nitride film deposition

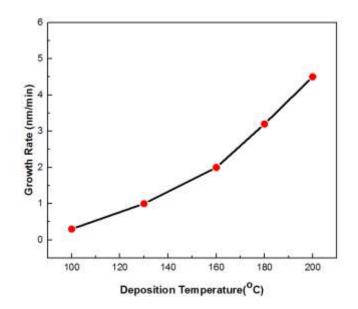

MnNx films were deposited at various temperatures of 100 °C, 130 °C, 160, 180 °C, 200 °C with NH<sub>3</sub> flow rate at 60 ccm, at 5 torr with the Mn precursor solution injection rate of 5 g/hr on thermal oxide substrates. The growth rate increases as the deposition temperature rises.

Figure 2.18. Substrate temperature of manganese precursor and the resulting growth rate of MnN<sub>x</sub>.

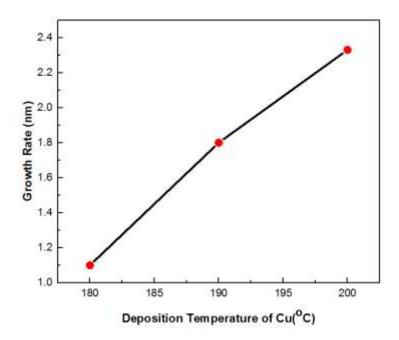

#### Copper film deposition

In this chapter, continuous and highly conformal copper-manganese films are deposited by DLE-CVD process. The vapor delivery rate from the DLE system is stable, reproducible and accurately known because the concentration of the solution and the liquid and carrier gas injection rates are known. Smooth and continuous copper films can be deposited within a temperature window of 180  $^{\circ}$ C to 200  $^{\circ}$ C. The DLE system for copper deposition used the syringe based DLE-CVD system.

To deposit copper,  $H_2$  is used as the only reactant gas for copper DLE-CVD deposition, flowing at 100 sccm. Combined with 0.1 ml/min of precursor solution and 60 sccm of  $N_2$  carrier gas, the molar percentages and partial pressures of the gas mixture introduced into the reactor were 0.2% or 0.02 Torr Cu precursor vapor, 2.8% or 0.28 Torr trihexylamine, 65% or 3.25 Torr  $H_2$  and 32% or 1.6 Torr  $N_2$ .

The resistivity of copper film deposited by DLE-CVD system was 3 µohm.cm. The surface morphology of copper was examined by AFM. The copper thin film deposited by the DLE-CVD process on the manganese nitride underlayer is fairly smooth with a root-mean-square roughness equal to 6.2% of its thickness.

Figure 2.19. 2D AFM map of Cu metal showing the very smooth films produced by the DLE-CVD Cu process.[41](collaborative work with Dr. Yeung Au)

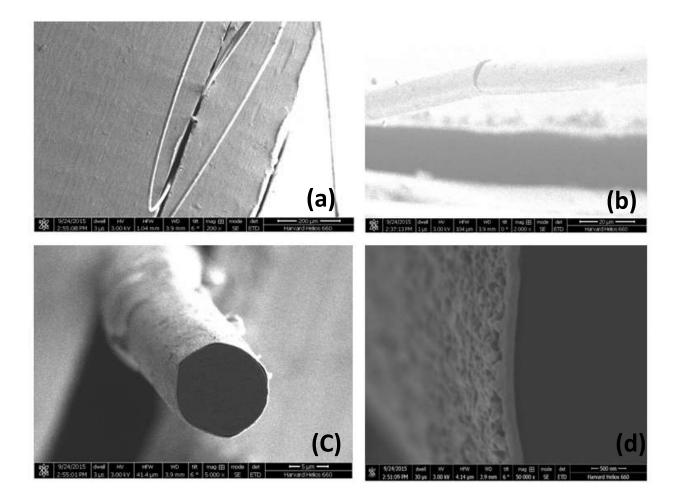

The step coverage of DLE-CVD copper for different growth conditions was examined by depositing copper on a silicon substrate with high aspect ratio trenches having  $MnN_x$  film previously deposited on it.

Then the coated substrate was hand cleaved to study the cross-section of the trenches. The cross sectional SEM images in Fig 2.18 show copper films deposited conformably inside a trench with an aspect ratio of 25:1 (0.5 um diameter and 12.5 um depth). The copper film at the top, side wall and bottom of the feature are almost the same, showing nearly 100% step coverage.

Figure 2.20. Cross-section SEM images of the Copper Trench sample

#### **Growth Rate**

The delivery rate of copper precursor solution and temperature are the two most important factors to determine the growth rate of copper film.

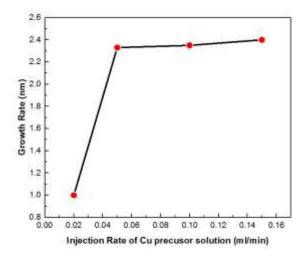

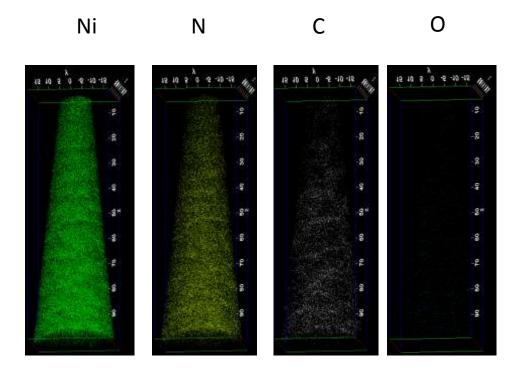

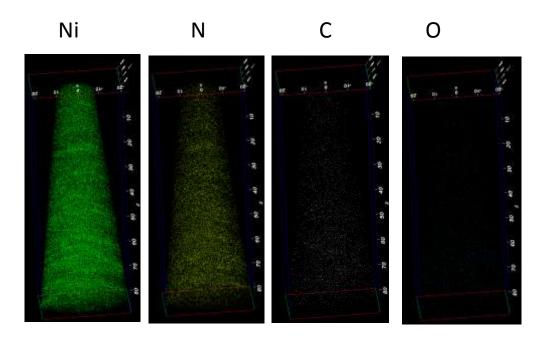

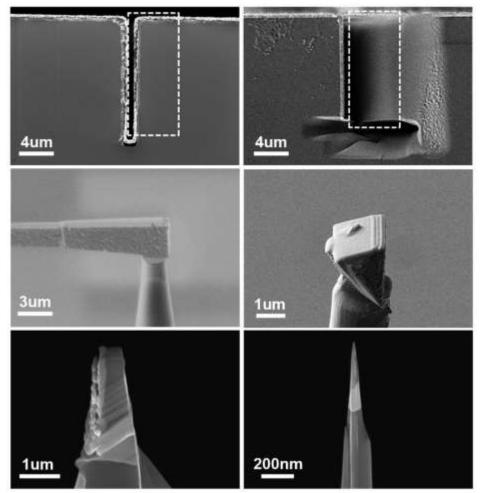

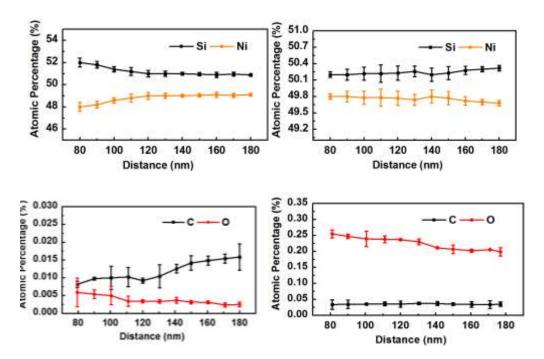

#### Impact of the delivery rate