## Toward Automatic Operating System Ports via Code Generation and Synthesis

#### Citation

Holland, David Andrew. 2020. Toward Automatic Operating System Ports via Code Generation and Synthesis. Doctoral dissertation, Harvard University, Graduate School of Arts & Sciences.

#### Permanent link

https://nrs.harvard.edu/URN-3:HUL.INSTREPOS:37365798

#### Terms of Use

This article was downloaded from Harvard University's DASH repository, and is made available under the terms and conditions applicable to Other Posted Material, as set forth at http://nrs.harvard.edu/urn-3:HUL.InstRepos:dash.current.terms-of-use#LAA

## **Share Your Story**

The Harvard community has made this article openly available. Please share how this access benefits you. <u>Submit a story</u>.

**Accessibility**

© 2020 David Andrew Holland All rights reserved.

## Toward Automatic Operating System Ports via Code Generation and Synthesis

#### **Abstract**

Porting operating systems is expensive. Recent developments in formal specifications of machine architectures and in program synthesis have made it possible to consider generating code for operating system ports rather than needing to write it by hand. Several challenges arise, the foremost being the current scaling limits of program synthesis for assembly language.

In this dissertation I take a system-level approach to generating ports of a small operating system. I present Aquarium, an ecosystem of languages and tools I designed to surround an assembly language synthesis engine. Chief among these are Grayling, a special-purpose compiler for context switch code, and Grouper, a tool implementing an approach I call *compositional code generation*, generating code in units of small synthesizable blocks. I have deployed these tools in the context of a simple though realistic operating system called Goldfish, and successfully generated working code for a number of machine-dependent operating system components.

### Contents

|   | List | stract                                | iii<br>viii<br>ix |

|---|------|---------------------------------------|-------------------|

|   | ACK  | diowiedginents                        | IX                |

| 1 | Intr | roduction                             | 1                 |

|   | 1.1  | Summary of Approaches                 | 3                 |

|   |      | 1.1.1 Scaling                         | 3                 |

|   |      | 1.1.2 Specifications                  | 4                 |

|   |      | 1.1.3 Machine Independence            | 5                 |

|   |      | 1.1.4 Generating Other Material       | 5                 |

|   |      | 1.1.5 System Design                   | 6                 |

|   | 1.2  | Contributions                         | 6                 |

|   | 1.3  | Thesis Statement                      | 7                 |

|   | 1.4  | Terminology and Notation              | 7                 |

|   | 1.5  | Document Organization                 | 8                 |

| 2 | Ope  | erating Systems Background            | 9                 |

|   | 2.1  | Terminology                           | 9                 |

|   |      | 2.1.1 CPUs vs. Cores                  | 9                 |

|   |      | 2.1.2 Mainboards and SoCs             | 10                |

|   |      | 2.1.3 Context Switching               | 10                |

|   | 2.2  | Supervisor Mode and Traps             | 11                |

|   | 2.3  |                                       | 12                |

|   | 2.4  | RAM Caches                            | 13                |

|   |      | 2.4.1 Layout ("Geometry")             | 14                |

|   |      |                                       | 14                |

|   |      |                                       | 15                |

|   |      | · · · · · · · · · · · · · · · · · · · | 16                |

|   |      | · · · · · · · · · · · · · · · · · · · | 16                |

|   |      | · · · · · · · · · · · · · · · · · · · | 17                |

|   | 2.5  | <u> </u>                              | 18                |

|   |      | • • •                                 | 18                |

|   |      |                                       | 19                |

|   |      |                                       | 19                |

|   |      |                                       | 19                |

|   |      | 2.5.5 Linux                                  | 20 |

|---|------|----------------------------------------------|----|

|   | 2.6  | The Machines in This Dissertation            | 20 |

|   |      | 2.6.1 MIPS                                   | 20 |

|   |      | 2.6.2 RISC-V                                 | 21 |

|   |      | 2.6.3 ARM                                    | 21 |

|   |      | 2.6.4 SPARC                                  | 22 |

|   |      | 2.6.5 x86                                    | 22 |

| 2 | D    | annua Carathania and Wariffantian Dadamana d | 23 |

| 3 | _    | gram Synthesis and Verification Background   |    |

|   | 3.1  | Synthesis and Specifications                 | 23 |

|   | 3.2  | Synthesis and Verification                   | 25 |

|   | 3.3  | Synthesis vs. Compilation                    | 25 |

|   | 3.4  | Synthesis vs. Superoptimization              | 25 |

| 4 | Prob | blem Analysis                                | 27 |

|   | 4.1  | Initial Requirements Analysis                | 27 |

|   | 4.2  | Initial Non-Requirements                     | 30 |

|   | 4.3  | Experience                                   | 31 |

|   |      | 1                                            |    |

| 5 | -    | narium of Languages and Tools                | 34 |

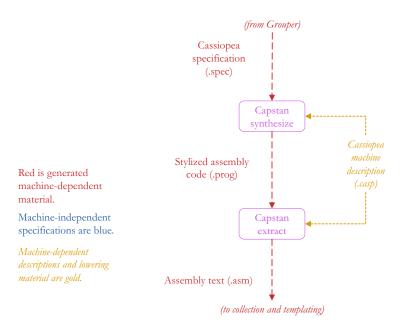

|   | 5.1  | Synthesis Core                               | 35 |

|   | 5.2  | Big Fish                                     | 36 |

|   | 5.3  | Small Fry                                    | 37 |

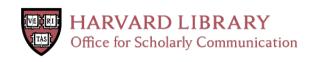

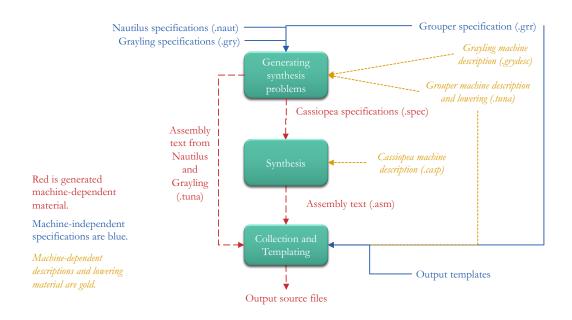

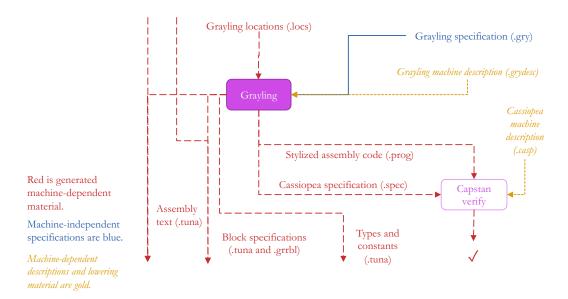

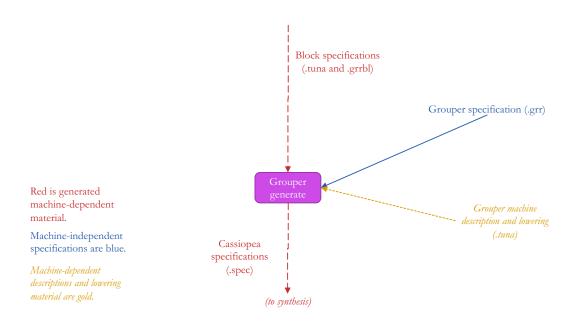

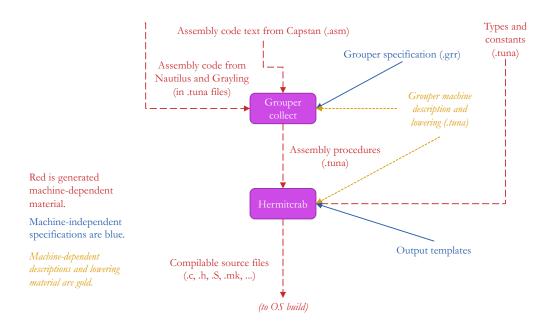

|   | 5.4  | Interactions                                 | 38 |

|   | 5.5  | Tuna Files                                   | 42 |

|   | 5.6  | Nautilus                                     | 44 |

|   | 5.7  | Hermitcrab                                   | 45 |

|   | 5.8  | Future Work                                  | 45 |

| 6 | Con  | npiling Context Operations                   | 47 |

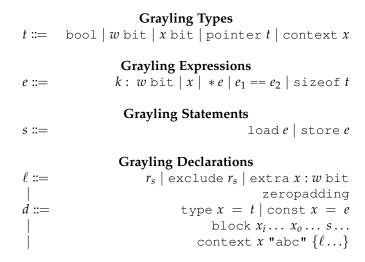

|   | 6.1  | Grayling                                     | 48 |

|   | 6.2  | Specification Language                       | 50 |

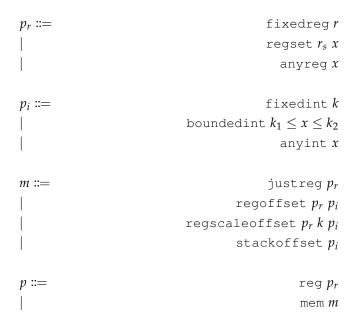

|   | 6.3  | Machine Description                          | 53 |

|   | 6.4  | Locations                                    | 58 |

|   | 6.5  | Producing Context Structures                 | 58 |

|   |      | 6.5.1 Membership                             | 58 |

|   |      | 6.5.2 Ordering                               | 59 |

|   |      | 6.5.3 Padding                                | 60 |

|   | 6.6  | Code Generation                              | 61 |

|   | 6.7  | Implementation                               | 62 |

|   | 0.7  | 6.7.1 Generating Code                        | 62 |

|   |      | 6.7.2 Generating Specifications              | 66 |

|   | 6.8  | Partial Saves in Hardware                    | 67 |

|   | 6.9  | Verifying the Output                         | 67 |

|   |      |                                              |    |

|   |      | 6.9.1   | Structure Offsets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67  |

|---|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   |      | 6.9.2   | Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 68  |

|   | 6.10 | Discus  | sion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 68  |

|   | 6.11 | Future  | e Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 69  |

|   |      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 7 |      | -       | O Company of the Comp | 70  |

|   | 7.1  |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71  |

|   | 7.2  | _       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73  |

|   |      | 7.2.1   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73  |

|   |      | 7.2.2   | Machine-Dependent Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 80  |

|   |      | 7.2.3   | , 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80  |

|   |      | 7.2.4   | Concurrency in Grouper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 81  |

|   | 7.3  | Lower   | ing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 82  |

|   |      | 7.3.1   | Refinement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 82  |

|   |      | 7.3.2   | Predicate Abstraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 84  |

|   |      | 7.3.3   | Lowering Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 87  |

|   |      | 7.3.4   | Retargeting Grouper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 87  |

|   | 7.4  | Elabor  | rating Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 88  |

|   |      | 7.4.1   | ~ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 88  |

|   |      | 7.4.2   | · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 92  |

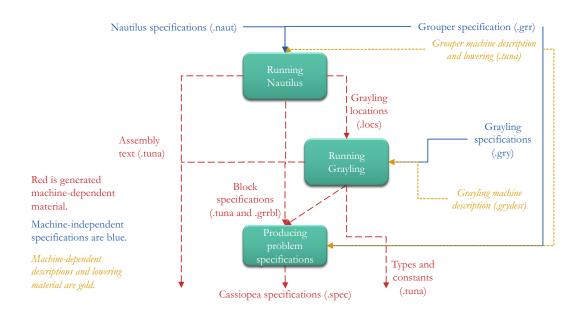

|   | 7.5  | Phases  | 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 94  |

|   |      | 7.5.1   | Prepare Phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 95  |

|   |      | 7.5.2   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 95  |

|   |      | 7.5.3   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 98  |

|   | 7.6  | Discus  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 98  |

|   |      | 7.6.1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 98  |

|   |      | 7.6.2   | 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 99  |

|   | 7.7  |         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .00 |

|   | , ., | Tuture  | , HOIR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .00 |

| 8 | Dep  | loymer  | nt and Evaluation 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 03  |

|   | 8.1  | Goldfi  | sh: A Small, Friendly OS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .03 |

|   | 8.2  | Specifi | icity and Generality in Machine-Dependent Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .05 |

|   | 8.3  | •       | sh Machine-Dependent Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|   |      | 8.3.1   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .09 |