# Minimizing NUMA Effects on Machine Learning Workloads in Virtualized Environments

### Citation

Broestl, Sean. 2021. Minimizing NUMA Effects on Machine Learning Workloads in Virtualized Environments. Master's thesis, Harvard University Division of Continuing Education.

### Permanent link

https://nrs.harvard.edu/URN-3:HUL.INSTREPOS:37367717

### Terms of Use

This article was downloaded from Harvard University's DASH repository, and is made available under the terms and conditions applicable to Other Posted Material, as set forth at http://nrs.harvard.edu/urn-3:HUL.InstRepos:dash.current.terms-of-use#LAA

# **Share Your Story**

The Harvard community has made this article openly available. Please share how this access benefits you. <u>Submit a story</u>.

**Accessibility**

## Minimizing NUMA Effects on Machine Learning Workloads in Virtualized Environments

Sean Broestl

A Thesis in the Field of Software Engineering for the Degree of Master of Liberal Arts in Extension Studies

> Harvard University May 2021

Copyright  $\bigodot$  2021 Sean Broestl

### Abstract

This thesis is an investigation into the performance ramifications of making specialized component reservations for machine learning workloads in virtualized environments. The reliance of machine learning on floating-point operations makes graphics processing units an important part of processing these workloads quickly. While virtualization is one of the most widely-used consolidation techniques used in data centers of all sizes, compatibility issues between graphics processing units and virtualization have slowed the adoption of virtualization for machine learning workloads.

To that end, this paper discusses the motivations and history behind virtualization and the application-specific acceleration devices used and how they are applied to machine learning on various public and private computing platforms. This is followed by a presentation of an experimental framework for testing the impact of controlling for non-uniform memory access when running machine learning workloads.

Using this framework, a series of experiments were performed and documented in this thesis that test multiple placement configurations for graphics processing units in a virtualized system and how throughput of data from the host system to the device was affected. Current virtualization platforms offer recommendations to use these settings, but do not talk about the specific impacts of implementing them. Based on the results of the experiments, configuration parameters and placement recommendations are presented along with information about how these settings can help optimize the machine learning pipeline and the potential pitfalls to their use.

### Acknowledgements

I offer the most sincere thanks to my thesis director Dr. James L. Frankel, whose guidance and feedback helped mold this thesis into a much greater work than I imagined it could be at the outset. Over the past nine months our regular meetings were a welcome source of both normalcy and laughter during a very difficult year for everyone. Of course, that step would not be possible without the efforts of my research advisor Dr. Hongming Wang and Dr. Sylvain Jaume, whose feedback, guidance, and persistence were instrumental in getting my idea transformed into a real proposal, and for that I am very grateful.

I also wish to thank my family, whose contributions of encouragement, assurance, and advice were oftentimes just the little nudge I needed to get through a bout of writer's block. Finally, thanks goes out to my colleagues at Brown University, who in addition to their affirmations, were able to support me with a loan of the computing resources necessary to complete this thesis.

# Contents

| Table  | e of C  | ontents                     | vi   |

|--------|---------|-----------------------------|------|

| List o | of Fig  | ures                        | viii |

| List o | of Tab  | bles                        | x    |

| Chap   | oter I. | Introduction                | 1    |

| 1.1    | l Pro   | blem Statement              | 3    |

| 1.2    | 2 Prio  | or Work                     | 5    |

| Chap   | ter II  | . Requirements              | 8    |

| 2.1    | l Hig   | h-level Requirements        | 8    |

|        | 2.1.    | 1 GPU                       | 9    |

|        | 2.1.    | 2 CPU and Hardware Platform | 10   |

|        | 2.1.    | 3 Software Requirements     | 12   |

| 2.2    | 2 Sys   | tem Components              | 13   |

|        | 2.2.    | 1 Orchestration             | 13   |

|        | 2.2.    | 2 Hypervisor                | 14   |

|        | 2.2.    | 3 GPU-backed VM instances   | 15   |

| Chapte | er III. Implementation                                      | 18 |

|--------|-------------------------------------------------------------|----|

| 3.1    | Non-Uniform Memory Access and Multi-Processor Design        | 20 |

| 3.2    | Test Environment Details                                    | 23 |

| 3.3    | IOMMU                                                       | 25 |

| 3.4    | Machine Learning Workflow Sample                            | 26 |

|        | 3.4.1 Code and Language Choices                             | 27 |

| 3.5    | Testing PCIe Performance                                    | 29 |

|        | 3.5.1 PCIe Bandwidth                                        | 34 |

|        | 3.5.2 Multiple GPU scenarios                                | 35 |

| 3.6    | Simulating non-ML workloads                                 | 36 |

| Chapt  | er IV. System Documentation                                 | 38 |

| 4.1    | Basic VM instance                                           | 38 |

| 4.2    | GPU-backed VM instances                                     | 40 |

| 4.3    | Non-GPU Load Generation                                     | 41 |

| Chapte | er V. Experimental Results                                  | 42 |

| 5.1    | Baseline Results                                            | 43 |

| 5.2    | Workload spanning multiple NUMA nodes                       | 46 |

| 5.3    | ML Workload on Mixed-use System (CPU-bound Load)            | 47 |

| 5.4    | ML Workload on Mixed-use System (CPU and Memory-bound Load) | 49 |

| 5.5    | ML Workload on Mixed-use System (Multiple NUMA-aware VMs)   | 51 |

| 5.6    | ML Workload vs ML Workload                                  | 52 |

|        | 5.6.1 Experiment Setup                                      | 52 |

|        | 5.6.2 Results                                               | 54 |

|        | 5.6.3 Results with two GPU-backed VM instances              | 55 |

|        | 5.6.4 Results with four GPU-backed VM instances             | 57 |

| Chapte | er VI. Summary and Conclusions | 64 |

|--------|--------------------------------|----|

| 6.1    | Knowledge Gained               | 64 |

| 6.2    | Configuration Recommendations  | 66 |

| 6.3    | Limitations and Known Issues   | 67 |

| 6.4    | Lessons Learned                | 68 |

| 6.5    | Future Considerations          | 70 |

| Refere | nces                           | 73 |

| Appen  | dix A. Glossary                | 77 |

| Appen  | dix B. Configuration Settings  | 82 |

| B.1    | VM Configuration               | 82 |

| B.2    | Hypervisor Configuration       | 82 |

| B.3    | Hardware Configuration         | 82 |

# List of Figures

| Figure 1  | GPU VM instance with 8 CPUs 2                               |    |  |

|-----------|-------------------------------------------------------------|----|--|

| Figure 2  | GPU VM instance with 16 CPUs, host has 40 cores (80 logical |    |  |

|           | CPUs)                                                       | 22 |  |

| Figure 3  | GPU VM instance with 24 CPUs, host has 40 cores (80 logical |    |  |

|           | CPUs)                                                       | 22 |  |

| Figure 4  | GPU VM instance with 16 CPUs and 256 GB of RAM              | 23 |  |

| Figure 5  | GPU VM instance with 24 CPUs and 256 GB of RAM              | 23 |  |

| Figure 6  | Notable python libraries used in experiment code $\ldots$   | 27 |  |

| Figure 7  | Main method spawning child processes                        | 30 |  |

| Figure 8  | Python method used to move data from system memory to GPU   | 31 |  |

| Figure 9  | Python method for moving data to main memory                | 33 |  |

| Figure 10 | Load Generator Workload Types                               | 37 |  |

| Figure 11 | Required packages for benchmark VM instance                 | 39 |  |

| 0         | Commands used to install CUDA 11 on Ubuntu 20.04            | 40 |  |

| Figure 12 | Commands used to instan CODA 11 on Obuntu 20.04             | 40 |  |

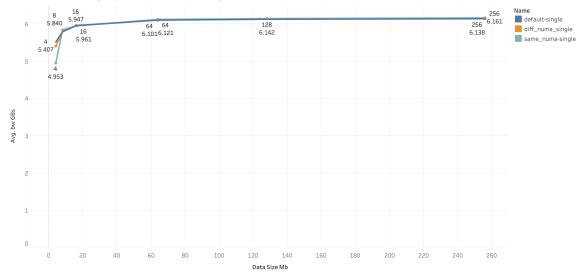

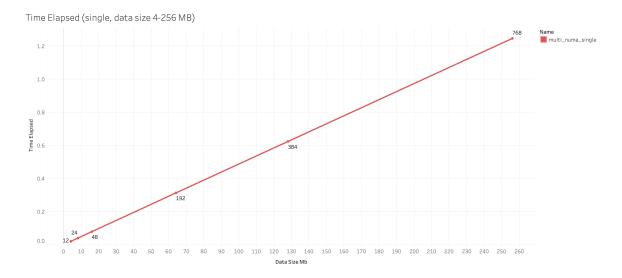

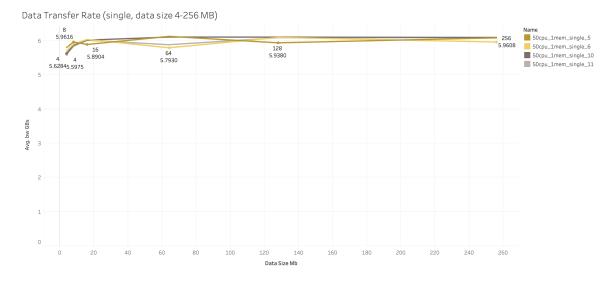

| Figure 13 | Baseline data transfer rate for single mode                 | 44 |  |

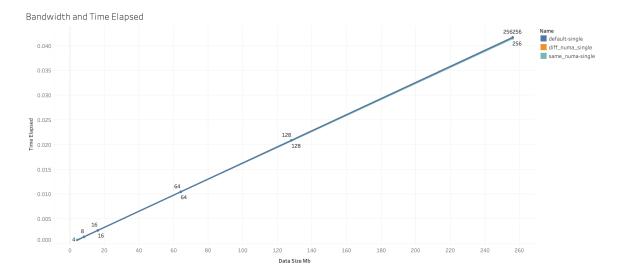

| Figure 14 | Baseline time elapsed for single mode                       | 45 |  |

| Figure 15 | Data transfer rate for single mode when VM instance sees mul-                                                              |    |

|-----------|----------------------------------------------------------------------------------------------------------------------------|----|

|           | tiple NUMA nodes                                                                                                           | 47 |

| Figure 16 | Time elapsed for single mode when VM instance sees multiple                                                                |    |

|           | NUMA nodes                                                                                                                 | 48 |

| Figure 17 | Data transfer rate sampling when loading CPU and RAM $\ . \ .$ .                                                           | 50 |

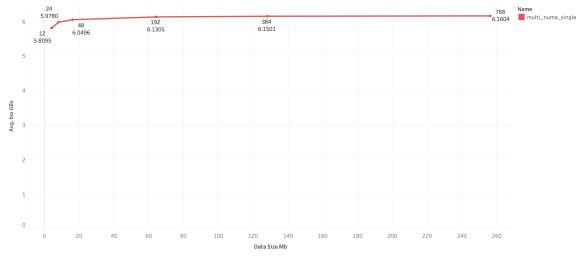

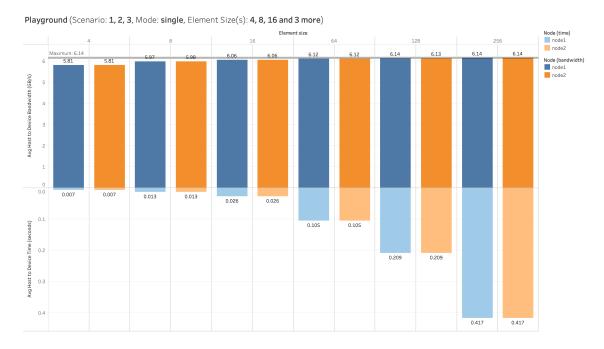

| Figure 18 | Baseline data transfer rate and time elapsed for multiple ML                                                               |    |

|           | workloads (single mode) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                     | 55 |

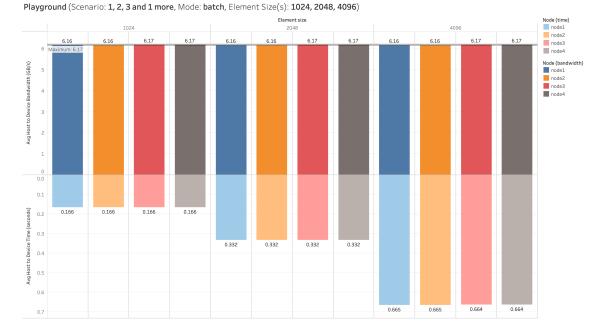

| Figure 19 | Baseline data transfer rate and time elapsed for multiple ML                                                               |    |

|           | workloads (batch mode)                                                                                                     | 56 |

| Figure 20 | Transfer rate and time elapsed for 4 GPU-backed ML workloads                                                               |    |

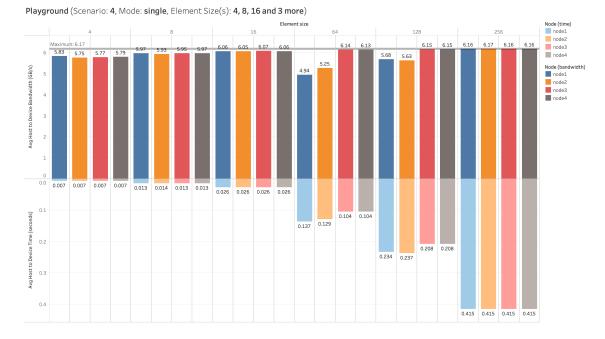

|           | (single mode), scenario 4 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                            | 58 |

| Figure 21 | Transfer rate and time elapsed for 4 GPU-backed ML workloads                                                               |    |

|           | (single mode), scenario 5 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                            | 59 |

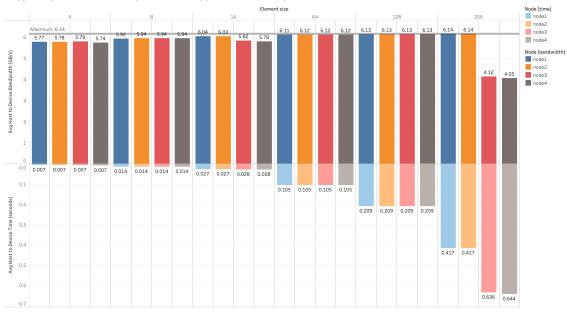

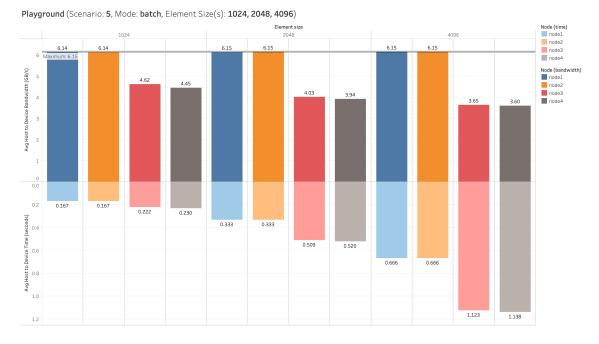

| Figure 22 | Transfer rate and time elapsed for 4 GPU-backed ML workloads                                                               |    |

|           | (batch mode), scenario $5 \dots \dots$ | 59 |

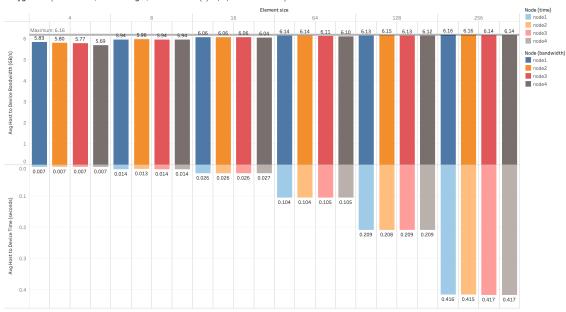

| Figure 23 | Transfer rate and time elapsed for 4 GPU-backed ML workloads                                                               |    |

|           | (single mode), scenario $6 \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                          | 61 |

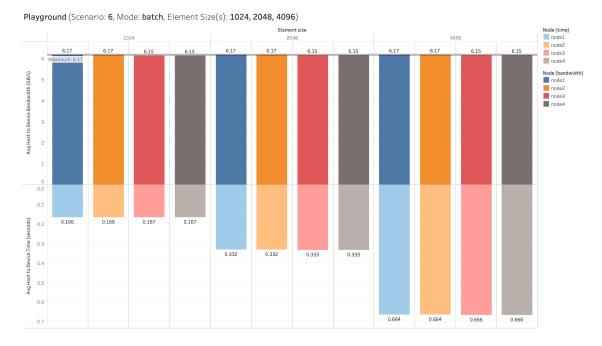

| Figure 24 | Transfer rate and time elapsed for 4 GPU-backed ML workloads                                                               |    |

|           | (batch mode), scenario $6 \dots \dots$       | 61 |

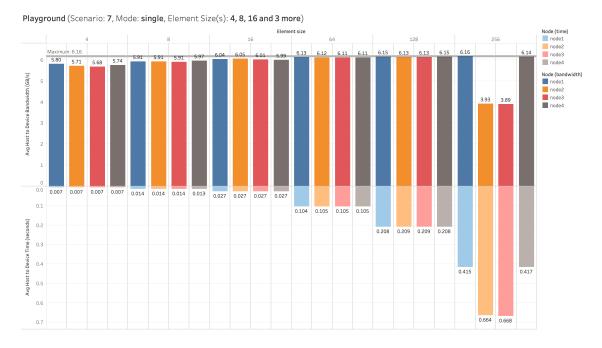

| Figure 25 | Transfer rate and time elapsed for 4 GPU-backed ML workloads                                                               |    |

|           | (single mode), scenario 7 $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                 | 62 |

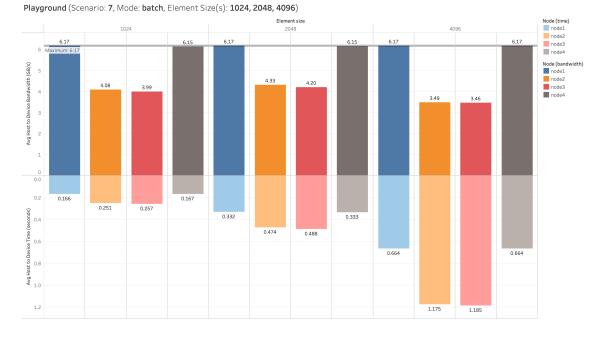

| Figure 26 | Transfer rate and time elapsed for 4 GPU-backed ML workloads                                                               |    |

|           | (batch mode), scenario $7 \dots \dots$                         | 63 |

|           |                                                                                                                            |    |

# List of Tables

| Table 1 | Version constraints for automation components                     | 14 |

|---------|-------------------------------------------------------------------|----|

| Table 2 | Version constraints for hypervisor                                | 15 |

| Table 3 | Hardware configuration for test systems                           | 24 |

| Table 4 | Command line switches for the benchmark application $\ . \ . \ .$ | 29 |

| Table 5 | ML vs. ML workload experiment scenarios                           | 53 |

# Chapter I.

## Introduction

Due to the increased utilization of machine learning in applications and the strong demands placed upon computing systems, machine learning is a driving force of innovation of computing components. Significant research goes into ways to optimize the different layers of these workloads in terms of speed, cost, algorithmic complexity, and data structure size. Machine learning, or ML for short, is a field of computing broadly referring to the use of neural network or similar algorithms that can be trained using a small initial dataset, then classify and identify data that has not been previously seen. ML workloads can utilize many or all components of the computing system, but one of the most important pieces of that system today is the electronic pathways used to move data across the system bus to a Graphics Processing Unit, or GPU, where floating point operations can be performed with a level of parallelism much greater than would be available on the CPU (Keckler et al., 2011).

This thesis will present a set of recommendations and configuration parameters that help optimize ML workloads that will be running on servers employing Virtualization. These configuration parameters will be applicable at multiple levels, both in how VM instances are sized and balanced on Hypervisor systems and how memory can be best allocated at the guest OS level.

The system bus of the x86 architecture has always been important from the

standpoint of moving data from the CPU to its various peripheral devices like storage and networking controllers. For most of its history, the Peripheral Component Interconnect Express, referred to as PCI and PCI Express bus have done a fine job of meeting the I/O needs of system components. It is the responsibility of processor developers to implement the PCI Express standard, which calls for a number of electrical lanes on the motherboard dedicated to the interface. Modern computing peripherals using the PCI Express, PCIe for short, have embraced the potential speed of this interface, bringing to market powerful high-speed devices like 40 Gigabit Ethernet adapters, non-volatile memory for fast storage, and Graphics Processing Units. PCIe slots are divided up among the limited number of electrical lanes provided by the computer system, using as few as one lane, or more commonly four, eight, or sixteen lanes. This topic is discussed in detail in Chapter 3.5.1. Today's GPUs most commonly use 16x slots in order to quickly move data to the high-performance processors and large amounts of memory located on the cards.

These cards have become so important to ML work that cloud providers like Google are taking steps to develop their own accelerators for this type of work in order to compete with GPU developers on price and performance (Jouppi et al., 2017). Cloud providers are also some of the heaviest users of virtualization technology. Virtualization is a technique in computing where a complete hardware computing system can be abstracted in software and as a result, many of these systems that were previously using an entire piece of physical hardware can be colocated on a single computer. The upside of this is that it reduces the physical footprint required to run massive computing operations while also enabling more flexible usage and payment models for only those resources that are needed for an application to run. If there is a downside, it is that all these virtual machines, or VMs, must share the limited physical resources of the computer on which they reside. The intersection of GPU use and virtualization is worth exploring in order to analyze the effects of the heavy PCIe bus consumption of GPU when applied to a shared computing model like Virtualization.

We will briefly cover some current designs in machine learning system systems as well as trends and challenges relevant to data center and cloud computing operators. This overview will present some commonly understood definitions for various jargon and official terms in the realm of system design. This introduction will serve as a way to set context for why optimizing execution environment is important to machine learning and the benefits that can be derived from doing so. We will also discuss the state of research and some prior work in this area.

Following the introductory chapter, this thesis will present some requirements relevant to both generically running ML workloads and to implement the environment used to prove the thesis. These details will include a summary of a common model used in processing of data for machine learning, as well as discussion on requirements in terms of hardware and software for that work. Before moving onto results, the implementation chapter will cover details on how experiments were run and the parameters used for each scenario.

The conclusion chapter will present sample VM configurations and code considerations to use when building ML workflows. Finally, the thesis will close with some brief discussion of some future considerations which may alter the importance of GPUs for this work in the future.

#### 1.1 Problem Statement

Not all workloads are so large as to need exclusive access to dedicated hardware and four or more GPUs. Many models and datasets exist that are smaller scale and still return useful results. For example, there are methods for training one of the most popular data sets, ImageNet, using down sampled versions of the images that produced results on par with algorithms using the full-resolution images (Chrabaszcz et al., 2017). Chrabaszcz et al.'s approach to working with a data set at a smaller scale gives support to the idea that more detail in data and training accuracy are not strictly tied to each other. Knowing this, it becomes possible to propose that the newest, fastest multiple GPU setups are not necessarily required for acceptable ML training. Another point worth considering is that GPUs are becoming popular to help speed up inference workloads on already trained models. One set of researchers recently presented research on how they used Nvidia V100 GPUs to speed up inference in COVID-19 infection simulations (Kulkarni et al., 2020). The conclusion to draw given these points is that the use cases for GPU are expanding into smaller use cases even as powerful GPUs are becoming more common. These smaller workloads are easily able to be run on virtualization platforms with a single GPU backing them, and it's worth exploring how to optimize those as well.

However, the solution isn't as simple as heading to the console of a favorite cloud provider, provisioning a VM, and training our new model. Most current configurations for GPUs on VM instances use a virtualization technique called pass-through to grant exclusive GPU access to a VM. Once pass-through is involved, it complicates the utilization of resources for the hypervisor.

The first problem is that management of a hardware component is no longer the exclusive domain of the hypervisor, and this has security, performance, and resource sharing implications. The second issue is that of Non-Uniform Memory Access, known commonly as NUMA. NUMA refers to the amount of time needed to access memory that is non-local to the processor where an instruction is being executed. Each CPU in a multi-processor system gets their own set of PCIe lanes and system RAM, and when you use pass-through the VM instance employing pass-through becomes strongly associated with one of those processors, the processor's PCIe lanes, and the processor's RAM. NUMA therefore has the potential to harm performance for the VM instance using pass-through because every memory-related operation could end up taking longer as the VM has to move data from one processor's memory to a device in another NUMA domain.

### 1.2 Prior Work

In their paper about OpenCL and CUDA performance on four different hypervisors using pass-through, Walters, et al. acknowledged that virtualization effects on NUMA is "interesting in its own right" (Walters et al., 2014). Briefly, CUDA is a programming language which uses C-style convention and is designed to make it easier to harness the power of a GPU for floating point arithmetic. Their deep dive into GPU pass-through provides sufficient evidence that it can be reliably expected to get performance approaching the levels of an OS installed on bare metal rather than a hypervisor.

Of note, in the time since Walters et al. paper was published, the hypervisor landscape has shifted quite a bit. Their research involved performance comparisons between the major hypervisors of the era — ESXi, KVM, and Xen. VMware's ESXi is still a popular choice for private data centers. Xen has faded somewhat in use — Citrix remains the primary commercial vendor supporting Xen in their Citrix Hypervisor product. KVM has a tremendous amount of momentum in 2020, with development support from Google, and an active fork used by Amazon Web Services for their Nitro hypervisor platform, (Honig & Porter, 2017), (AWS, 2020).

AWS announced the change to KVM in 2018, and Google Cloud Platform came to market with KVM as their hypervisor of choice. It can be difficult to determine quite where ESXi stands in terms of installed base and usage. As a publicly-traded company, VMware sales are a matter of public record and from all appearances, ESXi is a well-regarded hypervisor for private datacenters. Its high regard, however, has done little to improve ESXi's standing in the rankings of Hypervisors used for public cloud companies. For what it's worth, KVM is free and open-source, where as ESXi is licensed commercial software.

Denneman makes the case that in world with high-speed peripherals like GPU, PCIe devices are the primary units of data processing, (Denneman, 2020). Denneman rightly points out that in an x86 architecture, breaking NUMA locality for a VM instance means that data must traverse a central interconnect between processor/memory domains when trying to access a PCIe device owned by another processor. In the case of a system that is heavily utilized, this could become a limiting factor on performance, especially when dealing with many gigabytes or even terabytes of data. Fortunately, the bandwidth available to this central interconnect is greater than any single PCIe slot, so it may not be an issue to utilize it. The potential parallelism gains by utilizing another GPU may outweigh the costs of moving this data across the central interconnect.

Nvidia has introduced multiple solutions for virtualizing GPU access, the first being Nvidia Grid in 2013. Grid is a set of kernel modules for hypervisors and a specialized fork of Nvidia's display drivers that allowed for fractional access to a GPU, not unlike virtualizing a CPU. Cards designed for Grid, such as the Tesla M60, Tesla V100, and Tesla A100 contain multiple GPU cores on a single card, thereby routing around some issues related to low PCIe lane count in some previous CPU designs. While a promising and developing technology, much of its evolution has been focused on 3D accelerated application and desktop delivery rather than ML workload support.

A technology startup called Bitfusion (acquired by VMware in 2018) created

a GPU virtualization layer that allows for a user to split GPUs into logical blocks similarly to how CPU time can be split by a hypervisor. Bitfusion's solution was unique in the market because it not only allowed the user to slice up a GPU, but it allowed these devices to be accessed over an Ethernet transport. In other words, despite the advertised need of GPU hardware for the highest PCIe speeds available, it is conceivable that bandwidth needs can be met using a slower transport than PCIe.

# Chapter II.

### Requirements

This chapter specifies the requirements of the system.

### 2.1 High-level Requirements

This paper is primarily concerned with producing recommendations that help optimize workload placement on computing hardware that uses hypervisors. Previously, when combining older generations of processors with a hypervisor, the type of throughput and CPU utilization pattern desired for high-performance computing meant accepting trade-offs. Either the HPC-style workload wouldn't run well while general-purpose workloads did, or vice versa. Recent advances in processors from both Intel and Advanced Micro Devices (AMD) along with improvements in hypervisor software have made the general-purpose workloads and high-performance computing-style workloads much better tenants when sharing a piece of host hardware. As such, when designing and building virtualization hosts, there are several minimums that should be taken into account and are explained in more detail in this chapter.

### 2.1.1 GPU

Chapter 1.2 discussed some options for GPU virtualization or abstraction such as Nvidia Grid and VMware's Bitfusion product. These products either add a proprietary layer or shift I/O to a different part of the computer. Additionally, they add additional cost and setup complexity to a virtualized ML environment that is unnecessary. As a result, this thesis presents its solution using a pass-through configuration for the GPU due to its low cost and common deployment in the industry. This allows the VM to use the theoretical maximum performance of that specific hardware at the expense of removing the ability of another VM to be able to share that resource. Pass-through mode is a configuration option offered by all current hypervisors and needs to be employed to maximize ML workload performance. This is the method that is employed by most major cloud vendors, and as such, has the most real-world applicability.

When generating the conclusions of this paper, Nvidia GPUs were employed, specifically Nvidia Tesla M60 GPUs. The M60 is a GPU built specifically for use in hypervisor environments, as it colocates two distinct GPU units on a single PCIe slot in order to more densely pack GPUs into a single Hypervisor server. Nvidia publishes software and drivers that allow an administrator to fractionally divide the GPU core along various memory boundaries, such as 512 MB, 1 GB, 4 GB, and so on. This feature was expanded upon in later cards such as the V100, which employ a technique called multi-instance GPU (MIG), which allows an administrator to fractionally divide the GPU to a VM, container, or application instance. The card can also be addressed as a single-core GPU card with 8 GB of RAM and passed through to a VM, which is the configuration used here. Due to limitations with this line of GPU, it is not possible

to test the fractional usage features noted above as CUDA can only function with the card in a full 8 GB configuration. This limitation is due to the Tesla's use of CUDA cores rather than the Tensor cores used on more recent cards, and this limitation exists regardless of whether a pass-through or virtual GPU solution is employed.

Fortunately, GPU choice is more or less inconsequential to the methods used to reach the paper's conclusions. While library and hardware choice play a large part in the overall performance of ML workloads, here the focus is on verifying the effects of virtualization and NUMA locality when moving data across the PCIe bus. As such, there is less concern about what happens with the data once it is on the GPU and more about how fast data can be moved to the GPU. Nvidia's CUDA libraries expose a simple interface for copying data across the PCI bus from host memory to device memory. While CUDA is used here, OpenCL exposes a similar set of functionality, as does Google's TensorFlow. This mean that the methods described here could also be applied to AMD GPUs or ASICs.

### 2.1.2 CPU and Hardware Platform

While virtualization can be used in a variety of system CPU configurations, this paper is concerned primarily with applications for ML workload optimization in data center scenarios. Using advertised system sizes from major cloud providers such as AWS and Amazon as a guide it can be observed that the overwhelming majority of systems advertised for GPU utilize multi-socket systems with tens if not hundreds of cores. Large-scale systems are also an area of interest for GPU developers and cloud providers. For example, Nvidia recently entered the custom computer market with a line of data center systems packed with GPUs to do large-scale floatingpoint calculations for the data center with their DGX line of computer systems. Competitive to that approach, major cloud providers like Google and Amazon are developing their own application-specific integrated circuits to accelerate floatingpoint operations in their products.

Therefore, the recommendations of this paper are tailored around the use of multi-socket systems that employ two or more CPU sockets, high CPU core counts, and multiple PCIe interfaces. The conclusions presented here assume that processors from generations released in 2016 to present are used, such as Intel's Sandy Bridge or AMD Zen series. These CPU revisions guarantee the presence of features that are required for good performance on ML workloads and are enumerated here. First, PCIe 3.0, commonly available since 2010, is certain to be present on these platforms. PCIe 4.0 improves upon the standard, doubling the transfer rate of its predecessor, but the standard was only ratified in 2017. Peripherals using the 4.0 standard only became available in 2020. Second, these systems feature a high-speed bus interconnect between the processors which facilitates higher connectivity speeds between component devices on the PCIe bus and for processes that must cross NUMA domains. Intel's Ultra Path Interconnect and AMD's Infinity Fabric are examples of these interconnects, which has been available under various names since 2003. The speed of these devices is a contributor to the throughput that can be achieved for a workload, especially once system memory sizes start to get large enough to cross CPU memory domains.

Along with the high-speed interconnect, the system also needs to have native support for virtualization. Specifically, the processor needs to support CPU virtualization extensions like AMD-Vi and Intel VT-d, as well as memory and I/O virtualization for the PCIe pass-through features like function level reset and memory mapping. Note that while a processor may support virtualization extensions, it also needs explicit enablement in the system BIOS/EFI interface, as some vendors may not enable it by default. Without these features enabled, hypervisor software will either run poorly or not at all. Most processors released since 2008 should have these features, but the more recent the processor, the better. In the case of Intel, recent high-profile CPU cache exploits and the subsequent mitigation techniques have come with some costs to hypervisor performance under load. More recent CPU releases have lessened the impact of these exploits, but it is worthy of note since cloud and virtualization vendors who use Intel processors will still have some of these affected CPUs in their datacenters for years to come.

#### 2.1.3 Software Requirements

As it serves as the layer between the computer's hardware and the VM instances, the hypervisor plays an extremely important role in the level of performance that our VMs can achieve. Using a recent version is important so that the execution environment can make effective use of pass-through devices, large memory allocations at the hardware and VM layer, and optimizations in NUMA techniques. As discussed in earlier chapters, hypervisors passing control of devices to a VM have been around for a while. Newer GPUs can include memory banks that rival system memory and utilize low-level PCIe features. Using recent hypervisor versions ensures that there is support for these features. For example, in the test environment used here, advanced VM configuration had to be set in order to support large memory allocations on the PCIe bus. This functionality is available in KVM versions running on Linux 3.9 or higher, and on ESXi 4.0 or higher.

The VMs themselves should be built using UEFI boot and whichever drivers are provided by your hypervisor vendor to enable paravirtualized hardware. As of 2018, current versions of operating systems already include drivers or modules that allow seamless operation in a virtual environment regardless of hypervisor vendor.

The VMs built for the GPU-backed VM instances in the test environment

used in this thesis used Ubuntu Linux 20.04, though the methods and configuration presented here are OS-agnostic and should perform the same under other Linux distributions or Windows, given that similar versions of the software and drivers are employed. VMs used for load simulation used Linux and the stress-ng package due to its high flexibility in terms of targeting specific parts of the data processing path (King, 2017). Stress-ng was written with Linux in mind, though recent additions to Windows may make it possible to use for the load generation VM instances (this was not tested).

### 2.2 System Components

This section describes in detail the versions of the various components that were used to create an environment to test ML workload

#### 2.2.1 Orchestration

For provisioning both the load generation VM instances and the GPU-backed VM instances in the experiment environment, automation scripts are provided and their usage is detailed in Chapter IV. These can be used to quickly stand up the initial environment as well as supporting components like networking. Since the experiment environment involves a hypervisor, it is also an ideal target for automation of these types of operations.

For this experiment, Terraform was chosen as the automation tool (Hashicorp, 2021). Terraform is an open source infrastructure-as-code tool with commercial support from Hashicorp. It's an ideal fit for environments where building from scratch every time you want to change parameters in undesirable. Since Terraform tracks the state of the components you deploy, it is fast to quickly deploy an environment, test, and then change things and redeploy. Terraform itself consists of a few small

components, a parser for Hashicorp Configuration Language (HCL), a framework for creating, updating, and deleting the state of your infrastructure objects, and an engine for using first and third party providers to perform the actual work of creating or changing infrastructure. A provider in this context is a bundle of code which implements all the Terraform functions for create, read, update, and delete for a list of objects from a particular vendor. For provisioning the test environment used in this thesis Terraform's vsphere provider was used.

Of note, during the experimentation phase the author had a vCenter instance available for ESXi. vCenter is an enterprise-grade management product for one or more instances of their vCenter is commercial software and VMware restricts a significant portion of API functionality behind it. ESXi is available as a free version for personal use. As much as is possible, a version of the automation scripts will be available for the free edition of ESXi.

| Component        | Version        |

|------------------|----------------|

| Terraform        | $\geq v0.13$   |

| vsphere provider | $\geq$ v1.24.3 |

Table 1: Version constraints for automation components

### 2.2.2 Hypervisor

The hypervisor is an x86 architecture server with enough resources to run multiple VMs simultaneously. It must also support PCIe device pass-through so that distinct GPU cards can be reserved by distinct VMs. The experiment environment used ESXi 6.7, the most current stable release of the 6.0 branch of VMware's hypervisor. It provides an industry-standard level of performance and stability, while providing all the features needed to run the type of ML workloads that are of interest today.

| Component   | Version     |

|-------------|-------------|

| VMware ESXi | $\geq$ v6.7 |

Table 2: Version constraints for hypervisor

#### 2.2.3 GPU-backed VM instances

GPU-backed VM instances are VMs which run ML workloads on the hypervisor. As discussed in the introduction, machine learning really doesn't have many constraints on what we can try to teach a neural network to do. Specifically though, these workloads can be simplified as different implementations of neural networks that do things like object recognition, sentiment analysis, or transformation tasks.

Rather than try to figure out parameters specific to each of type of workload, this thesis concerns itself with the hardware common to the GPU processing pipeline. Certainly, if one were interested in the hyperparameters or algorithms that could best process a specific type of ML workload, there would probably have been a new paper proposing a novel solution published in the time it took to read this paragraph.

Since this experiment is interested in the NUMA effects and virtualization bus-sharing factors of multiple GPU-equipped VMs, the experiment environment will need to have at least two VMs dedicated to simulating an ML training environment. Furthermore, each GPU will need to be attached to the PCIe bus of a distinct CPU socket, and then to a VM using a specific set of CPU cores. The number of cores and the allocation from each physical NUMA domain will be changed several times in order to demonstrate the various scenarios that can occur as VM processes are scheduled. Specific configurations for this will be discussed in the implementation chapter.

The GPU-backed VM instances use a baseline of 16 virtual CPUs and a total of 256 GB of RAM to match instance sizes used by common GPU instance sizes on GCP and AWS. This CPU configuration was also chosen because the systems used for the thesis had enough physical cores that we could guarantee that a VM instance would only see a single NUMA domain. In large-scale training scenarios, more RAM may be desirable and this paper makes no specific recommendations for CPU to RAM ratios. For the sake of generating this paper's conclusions, this size made sense as an instance size larger than commonly available for desktop processors while having a RAM size that allowed for multiple GPU-backed VM instances to be loaded at once on the test hardware without resorting to memory over-commitment techniques.

Some recent Nvidia GPUs implement a technology known as NVLink, which chains together multiple GPU cards via a proprietary private bus in order to increase I/O speed and parallelism between GPUs by bypassing the PCIe bus. These cards were not taken into consideration during testing, due to their relatively high cost and lower applicability to the small-to-medium sized hypothetical ML workloads that are part of the scenario being tested for. It is the opinion of the author that NVLink is an impressive technology in terms of adding parallelism, increasing the available GPU memory space, and reducing the number of times that workloads must return to the CPU for additional data. However, this solution does not take away the fact data must still traverse the PCIe bus at least twice, once on load, and once on return of results. Therefore, it is still worth sizing VM instances in such a way as to avoid virtualization and NUMA effects, regardless of whether additions to the system bus such as NVLink are utilized.

A final consideration that is discussed briefly in the implementation chapter is that rack mount and blade server platforms can and do make use of interfaces that are uncommon in desktop and laptop systems. In particular, PCIe riser or other port multiplier solutions are used to increase the number of expansion slots, or for cooling considerations. These riser cards will make use of 32x PCI slots and divide those lanes among multiple slots. This would be unremarkable, however it does appear to interfere with the reporting of PCIe link speed by lspci tool. In the case of one of the test servers used in the experiment environment, the GPU would be reported as being plugged into a 5 GT/s slot with a 32x width. This led to some considerable investigation time to understand why the link speed was reported in this manner. The lesson learned here is that relatively uncommon hardware plus virtualization interactions can cause strange reporting errors. In some cases, verification by physical examination may be preferable.

# Chapter III. Implementation

The original goal of this thesis was to produce recommendations around building configurations for how to best generically allocate computing resources in a mixeduse data center. The author envisioned a deep-dive into virtualized system architecture and alignment of virtual CPUs against a physical architecture. This study would investigate the effects of higher CPU utilization, non-uniform memory access effects, and high VM density vs. high physical CPU use. This was driven by a need to understand how to best allocate shifting consumption of compute workloads from databases and web applications to ML and other research workloads. Historically, applications like web servers were easy to virtualize because those applications had CPU usage patterns that involved low sustained use or short bursts of high utilization.

Instead of low utilization that can be easily shifted to idle processors or even other physical nodes based on overall system load, number crunching for research and machine learning uses a constant stream of I/O from local/remote storage, to the CPU for preprocessing, then onto the PCIe bus for GPU processing. Without going into detail about the nuances of CPU scheduling, virtualization has functioned best when resource utilization is short bursts of high activity vs. sustained use. Since virtualization is a foundational technology in cloud computing and data centers, it's important to think about the impact that many VMs running at high resource utilization means for scaling and consolidation ratios in data centers.

During the period spent researching this topic, it became overwhelmingly clear that while there are projects that use CPU for ML training and inference work, a majority of this work takes advantage of the ability of GPUs to do fast floating-point arithmetic. However, this doesn't make the CPU obsolete or remove it from the ML workload equation. GPUs do one the one task of floating point arithmetic and do it extremely well, but cannot perform the common tasks expected of a computer. As the central component of a computer the CPU is required for allocating memory and moving data across the system buses to the GPU, and this vital role makes it ideal for preprocessing data. When considering the full data ingestion path and how many components are utilized, an ML workload doesn't appear to be something that should be difficult to use a hypervisor for. However, one of the most important factors for ML workloads is how much I/O the system can provide when it has to move data between system memory, GPU memory, network, and disk, all which share a common bus. That lead to the investigation of how much it matters to properly align VMs to particular CPU/Memory/PCI bus boundaries and if doing so truly provides optimization in the data center-size computing space.

A central question this thesis seeks to answer was what, if any, performance effects would be encountered due to I/O limitations on the PCIe bus and system bus. In virtualization scenarios that do not involve ML, this wasn't necessarily an issue, or at least it wasn't one to worry about over sustained periods. With the greater prevalence of GPU in servers, and not just one GPU per server, there now needs to be consideration given to what the cost will be to move data from disk, to main memory, and then onto the GPU and back. GPU and other application-specific accelerators depend on the use of 16x PCIe slots and bandwidth provided by the PCIe 3.0 and higher specifications. This places GPUs at the top of the priority chart in terms of the bandwidth they can demand from the system bus.

#### 3.1 Non-Uniform Memory Access and Multi-Processor Design

For a variety of reasons, designs for x86 processors changed in the early 2000s to place more processing cores on each physical CPU chip. These chip designs are referred to be as multi-core processors. This innovation made multi-CPU processing much more accessible by bringing a level of computing power to the desktop that was previously only possible in x86 multi-socket systems, which at the time used multiple single-core processors.

Today, desktop multi-socket processors can have as many as 10 cores per processor chip. Server-class processors are capable of having two more times that number of cores depending on CPU generation and manufacturer.

The most differentiating factor for systems with multiple processors over more common single-socket systems is that each socket gets its own set of memory pathways and system bus channels. This enables more effective density of VMs using GPUs because you can place more VMs on a system each with exclusive access to its own pass-through GPU without concerns that multiple VMs will consume all the PCIe bandwidth and slow operations for every consumer. Extra sets of PCIe lanes and memory channels come with their own set of concerns though.

Non-Uniform Memory Access is a design consideration in multi-processor system architecture that divides system memory into domains based on how close the memory is to each distinct processor. Each processor is designated as a single domain and can access its own memory without penalty. Processes running in a NUMA domain are able to access any part of the system memory, but accessing memory outside the execution domain incurs an access time penalty.

There are various implementations of NUMA depending on CPU architecture.

The major processor design companies using the x86 architecture implement NUMA using a central interconnect between all system CPUs. Intel refers to this component as the Ultra Path Interconnect or Quick Path Interconnect depending on processor generation. AMD uses a technology called HyperTransport for their interconnects.

Modern interconnect designs have greatly increased the speed of this component, but it cannot match the speed of a dedicated CPU to memory lane. NUMA designs enable a much higher density of processing power available in a single computer, though as described here there are additional parameters to take into consideration when writing software for these platform.

Multi-processor systems also get a full set of PCIe lanes allocated to each processor, greatly increasing the density of peripheral devices that can be attached to a single computer. Peripheral devices attached to a processor are also subject to the effects of NUMA in the same manner that memory is.

In a virtualized system, NUMA becomes a concern because VMs can be told that they have more than one processor and then be scheduled and executed on multiple physical CPUs when it may not be advantageous to do so. Knowing the conditions under which the hypervisor will make a VM instance aware of the host system's multiprocessor architecture is an important part of maximizing performance for a specific workload.

For this thesis, VMware's ESXi hypervisor was chosen as the platform. As an example, ESXi's rules for NUMA awareness are as follows: Any VM with an eight CPU configuration will be not be NUMA-aware, beyond that, any VM with a CPU count greater than the core count on a single physical CPU will be scheduled into multiple NUMA nodes. Figure 1 shows the output of the lscpu command on a VM instance with eight virtual CPUs.

As CPU count increases, NUMA node count for the VM instance will also

#### Figure 1: GPU VM instance with 8 CPUs

user@gpu-node01:~\$ lscpu | grep NUMA NUMA node(s): 1 NUMA node0 CPU(s): 0-7

Figure 2: GPU VM instance with 16 CPUs, host has 40 cores (80 logical CPUs)

user@gpu-node01:~\$ lscpu | grep NUMA

NUMA node(s): 1

NUMA node(cpu(s): 0-15

increase depending on the physical CPU socket and core count. If a VM can be scheduled onto a single physical CPU, ESXi will continue to constrain the VM instance to a single NUMA node. This can be validated on the test system, which has a total of two physical CPUs with 20 cores each. Note that NUMA calculations happen based on core count without hyperthreading or related thread-splitting techniques being considered. These processor features split a single CPU core into two execution threads, allowing the platform to report itself as having twice the physical cores, referred to as logical cores. To the untrained eye, this can be misleading, as other parts of the ESXi interface will report available CPUs as the value of cores \* 2 with this processor feature enabled. Figures 2 and 3 illustrate this difference.

Likewise, NUMA controls where a VM instance's RAM is allocated even if the entire RAM allocation could fit entirely in the memory banks of a single NUMA node. See 4 and 5 for examples of the allocations.

Figure 3: GPU VM instance with 24 CPUs, host has 40 cores (80 logical CPUs)

user@gpu-node01:~\$ lscpu | grep NUMA NUMA node(s): 2 NUMA node0 CPU(s): 0-11 NUMA node1 CPU(s): 12-23 Figure 4: GPU VM instance with 16 CPUs and 256 GB of RAM

user@gpu-node01:~\$ cat /sys/devices/system/node/node\*/meminfo | grep MemTotal

Node 0 MemTotal: 263948196 kB

Figure 5: GPU VM instance with 24 CPUs and 256 GB of RAM

user@gpu-node01:~\$ cat /sys/devices/system/node/node\*/meminfo | grep MemTotal Node 0 MemTotal: 131974098 kB Node 1 MemTotal: 131974098 kB

### 3.2 Test Environment Details

To test the ideas being proposed in this paper, two server-class computers with multiple GPUs were procured — A HP ProLaint DL380 Gen9 rack mount server and an HP ProLaint WS460c Gen9 blade server. Both systems meet the high-level requirements presented in chapter II, though they differ slightly in terms of CPU and GPU. System Configurations for these two systems are summarized in the following table.

The GPUs available in the test systems are not an exact match in terms of model. However, they are the same in terms of processor generation and installed RAM. Both utilize the Nvidia GM204 GPU core, which is one of the last chips to use Nvidia's Maxwell architecture. The following table summarizes the differences between the two in order to establish that the test systems are close enough to be able to consider results together.

It is worth noting that System 2 is a blade form factor, and does not use the traditional PCIe form factor for its GPUs. This server utilizes the Mobile PCI Express, which uses the acronym MXM, interface for its Tesla M6 cards. This interface

|                    | System 1                            | System 2                 |

|--------------------|-------------------------------------|--------------------------|

| CPU                | Intel Xeon(R) E5-2698 v4            | Intel Xeon(R) E5-2699 v3 |

| CPU Family         | Broadwell                           | Haswell                  |

| CPU Clock          | 2.20 GHz                            | 2.30 GHz                 |

| System RAM         | 512  GB                             | 512 GB                   |

| PCIe Revision      | 3.0                                 | 3.0                      |

| Max PCI Lanes      | 40                                  | 40                       |

| Installed GPU      | Nvidia Tesla M60                    | Nvidia Tesla M6          |

| Storage            | None installed                      | None installed           |

| GPU                | Tesla M60                           | Tesla M6                 |

| GPU Card Interface | PCI Express                         | MXM                      |

| PCIe Slot Speed    | 16x                                 | 16x                      |

| GPU Architecture   | Maxwell                             | Maxwell                  |

| GPU RAM            | $16 \text{ GB} (2x \ 8 \text{ GB})$ | 8 GB                     |

| GPU Core Type      | CUDA                                | CUDA                     |

| GPU Core Count     | 4096 (2x 2048)                      | 1536                     |

Table 3: Hardware configuration for test systems

may be unfamiliar to those who haven't worked with blade systems or PC laptops that integrate high-performance GPUs over the past decade. MXM interface slots resemble laptop RAM slots, in that it uses a flat connector with the device entering at a 45-degree angle and then lowered until the back of the card is flat against the motherboard surface. Retaining clips and multiple screws are used to keep the card in place. As it is a form-factor and not a different bus, standard PCIe slot speeds are determined by number of pins utilized. While laptops will generally only have space for a single MXM form-factor card, other devices without the same space constraints can have multiple MXM slots. Indeed, this is the case with the blade server used here, as it comes equipped with four MXM slots, all of which are populated in the test environment.

For the MXM/blade configuration, it should be stated that the Tesla M6 is one of only a few Nvidia GPUs that utilized the MXM interface and were not designated mobile GPUs intended for laptop use. The Tesla M6 was released in September 2015 and has not seen a followup since. Given the lack of new product in this line, the comparatively low core count vs the PCIe version, and the absence of other servers that include GPU using the blade form factor it can be assumed that this was not a direction the data center market decided to go. Fortunately, the test parameters as defined here are decoupled from the actual GPU performance, as we are only controlling for PCIe congestion and NUMA effects. The MXM form factor does provide us with equivalent PCIe speeds and functionality, and therefore should still be a valid test bed here.

#### 3.3 IOMMU

On the x86 platforms involving virtualization an additional system component comes into play, the input-output memory management unit (IOMMU). This interposer provides memory address virtualization and management functions for the PCIe bus. It also serves as a cache for translated addresses and a way to add a compatibility layer for devices that are not designed with virtualized environments in mind. In a hypervisor or bare-metal OS, use of the IOMMU is elective based on need. Enabling or disabling it is a configuration toggle in the kernel configuration. Use of the IOMMU is in fact a common configuration parameter when attempting to use desktop or gaming GPUs in a hypervisor environment. However, it has been shown that using the IOMMU device can cause appreciable latency for certain types of network workloads, (Neugebauer et al., 2018).

For the sake of completeness several benchmarks using this option were tested during the research phase of this thesis. In contrast to Neugebauer, there was not an observed difference in completion times of the benchmark with IOMMU disabled or enabled. This is likely a result of the NVIDIA Tesla cards in use being specifically built for use in a hypervisor environment. That said, based on other findings, it is likely a best practice to enable IOMMU only if it is required in order to successfully passthrough a GPU to a VM. Adding additional PCIe latency is obviously not optimal, even if it was not observed here.

#### 3.4 Machine Learning Workflow Sample

In order to test how both virtualization and NUMA can impact the execution of ML workloads, it's important to understand how these workloads are structured. The steps involved in a common ML workload will be summarized here.

All workloads will start with data resting on a storage volume. The closer the data is to the system bus, the better, so high-speed SSD or non-volatile memory express (NVMe) disks residing on a SATA 3.x or PCIe bus are preferred. These transports provide the highest speeds possible for data, with the lowest potential for transport latency that might be incurred by an Ethernet or fiber-based storage solution. That said, it is worth considering that because NVMe also shares the PCIe bus with other devices like Ethernet or GPU devices, that could potentially slow movement of data to a GPU depending on how the workload is structured.

Once the data is in memory, some preprocessing of the data element may be performed on the CPU for tasks that a GPU doesn't do well. Following this, data can be moved to the GPU over the PCIe bus. In the case of CUDA, which was used here, the required memory is allocated, and the object is moved from system memory across the PCIe bus into GPU memory.

Objects in memory on the GPU can then be processed by whatever GPU program is written for the workload and returned to system memory across the PCIe bus. Depending on complexity and data set size, all the objects may not fit into GPU memory at one time. In these cases, data should be moved in batches and returned to the system in batches. Figure 6: Notable python libraries used in experiment code numa==1.4.6 numpy==1.19.4 psutil==5.8.0 pycuda==2020.1

#### 3.4.1 Code and Language Choices

Fortunately, analyzing the effects of virtualization and NUMA doesn't require a replication of the entire workflow described in the previous chapter. By focusing exclusively on an area of the process that utilizes a shared system resource, we can write tests that stress that component and see which, if any, parameters can be used to balance or ensure that a chosen workload gets 100% of the resources it requests.

Before going into further detail about the testing workflow, figure 6 lists the important external libraries used in the experiment code. numpy, mp, and pycuda are core to the functionality of the code (Harris et al., 2020), (McKerns et al., 2012), (Klöckner et al., 2012). numa and psutil are helpful in data collection about where and how processes ran (Smirnov, 2020), (Rodola, 2021). This chapter will discuss the specific application and rationale for each package's inclusion.

The experiment environment skips the loading of data from disk, opting instead to use the numpy library to create in-memory numpy.float32 arrays using random data of a user-defined size at runtime. This process simulates the workflow steps where data would be loaded from disk, preprocessed by the CPU, and allocated in system memory.

numpy.float32 is a reasonable default to choose for this example. The reasons being is that numpy.float32 represents a single-precision number and is a reasonable default to choose given performance and support configurations in Nvidia's card lineup. Using double-precision numbers also requires a much larger memory footprint, resulting in longer times to transfer data to the GPU for not much benefit. There is evidence that even lower levels of precision can still yield well-trained models, and that the costs of using higher precision don't outweigh the benefits of being able to do more training operations in the same time frame (Gupta et al., 2015). In the interest of running on as many devices as possible, and avoiding unnecessary processing and memory overhead, single-precision is an ideal choice in these experiments as a reasonable trade off between the speed of lower precision, and the possibility of using higher precision as future hardware innovation allows for it.

PyCUDA uses the most recent version, 2020.1, though the functions employed here are all stable portions of the code base, and it is not expected that they will be significantly altered in the future. PyCUDA is a python interface to the CUDA API that allows the programmer to make use of the power and speed of CUDA while also maintaining the convenience, readability, and breadth of the python language. Using python as a hook into CUDA enables the programmer to make use of popular and powerful data processing libraries like matplotlib, numpy, scipy, and more while still being able to write GPU code and execute from the python environment with few speed penalties. In this manner, the example can be more relevant to how machine learning code is written now than being a one-off example.

The experiment code also uses the python multiprocessing library. This allows the user to spawn any number of worker processes to split up the data across them for movement onto the GPU. During the design phase of the experiment environment, it would sometimes be observed that a single process could not fully saturate the PCIe bus. Running multiple workers ensures that the bus is completely consumed, as well as providing flexibility in the code should it be desired to run against multiple GPUs. Multiple GPU behavior is configurable at runtime, please see chapter IV for complete instructions on how to do this. By default, the code tries to account for multiple GPUs if available and map them to workers in a round-robin fashion in order to emulate the behavior of popular libraries that take advantage of multiple GPUs like TensorFlow, though that is not a specific end goal.

Finally, the numa and psutil libraries are used to help with results collection. psutil is handy because it can provide all sorts of stats about the execution of a process. Most important here is that psutil has knowledge of what CPU a process executes on, which is important for being able to determine if a process ran in a nonlocal NUMA node. Due to the way python processes are scheduled by the OS, we can have certainty that all of a process' instructions will execute on the same CPU core, even when more than one processor is available. Since the multiprocessing library is used, it becomes even more important to track which CPU a process executes on, since child processes are likely to execute on other CPUs.

# 3.5 Testing PCIe Performance

In the benchmark code, there are a few key functions that are used to test the parts of the system that can tell us how load is being processed. This chapter will discuss specific details about the benchmark code that has been implemented.

The following table details all the switches available in the benchmark application.

| Switch             | Default | Description                                     |

|--------------------|---------|-------------------------------------------------|

| -help, -h          | N/A     | Displays the help dialog                        |

| -hwinfo DEVICE_ID  | 0       | Displays some diagnostic info                   |

| -single SIZE       | 8       | Size in MB of an element                        |

| –batch SIZE        | 512     | Size in MB of a batch of elements               |

| –elements, -e N    | 1       | Number of elements to use for –single or –batch |

| –num_devices, -d N | 1       | Number of CUDA devices to use in benchmark      |

| –iterations, -i N  | 4       | Number of iterations to run the benchmark       |

| –workers, -w N     | 1       | Number of concurrent processes to run           |

Table 4: Command line switches for the benchmark application

Figure 7: Main method spawning child processes

```

np_list = [args.single for x in range(args.elements)]

pool = Pool(processes=args.workers)

for i in range(args.iterations):

print("Run {}:".format(i))

total_size = args.single * args.elements

res = pool.map(process_single, np_list)

```

The benchmark application has three major parts: the main method which ingests the command line parameters, the data to host memory mover, and the host memory to device mover. These correspond to various parts of the ML workflow, and it makes most sense to explain them in order starting with the main method. As Table 4 illustrates, there are a number of configurable run-time behaviors for the application. The main method is responsible for ingesting the command line parameters and dispatching those to the python multiprocessing module, which determines how many processes will run the load.

Figure 7 covers the majority of the program loading logic. The application creates a python multiprocessing Pool object based on the number of workers requested. Then for the number of iterations requested, the pool will spawn the number of workers specified by the --workers flag and pass a list of elements to the pool. The pool remains as the parent process and passes each element of np\_list off to a child worker process to complete the load.

There are two ways in which to run the application code, single or batch mode. Single mode allocates and moves data once per element, while batch mode is intended to model the behavior of allocating and moving data as one large block. Moving memory in batches is the recommended method in order to optimize execution time and batch mode is implemented in a manner to mimic this behavior (Harris et al., 2020). However, due to the way the --batch switch is implemented, only a

```

Figure 8: Python method used to move data from system memory to GPU

```

```

def test_child(size):

# Init the CUDA context

cuda.init()

# Create numpy array of n size

np_array = np.random.randn(int(size * (10**6)/4)).astype(np.float32)

# Allocate memory on GPU

mem_gpu = cuda.mem_alloc(np_array.nbytes)

# Allocate memory on host

mem_host = cuda.register_host_memory(np_array)

# Copy np array to system memory

np_to_hmem(np_array,mem_host)

# Copy system memory to GPU memory

cuda.memcpy_htod(mem_gpu, mem_host)

# Clean up CUDA instance

mem_host.base.unregister()

mem_gpu.free()

```

single worker process is possible due to restrictions in how CUDA manages execution context. Reasons behind this will be explained further along in this section when analyzing the data to host memory mover. Both modes have been implemented as a way to test if batch transfers still perform better when there's contention for bandwidth on the PCIe bus.

Before explaining this piece of code, it's important to understand that CUDA does not support an execution model where CUDA is initialized in a parent process and then accessed from a child process. Therefore, all child processes must initialize their own context when they start up. This is unfortunate from the standpoint that context creation and destruction does come with a time and resource cost in order to set up and tear down. Managing context is an important part of production code for this reason, but for the purposes of this experiment, we control for it by not starting the timer until after the context creation is complete. In production code, a library such as Tensorflow or similar would use a threaded approach and shared memory.

Once CUDA is initialized, the full power of PyCUDA is available to the child

process. This function takes in the size of the desired numpy array and creates it using the numpy.randn() function and of type np.float32. As discussed in 3.4.1, float32 is the most commonly-employed precision level as well as being the one best supported by Nvidia GPUs and therefore a natural choice for the experiment. With the array created, the space required for it can be registered in memory using the cuda.register\_host\_memory()function and then copied to system memory using the np\_to\_hmem() function.

This leads to the question of why this step is needed if the numpy object already exists in memory. In order to move data across the system bus, a memory region on the GPU device must map to a block of system memory. CUDA has two techniques to accomplish this, pageable or page-locked (pinned) transfers. cuda. memcpy\_htod() permits the user to pass it a GPU memory allocation and the numpy object or a host memory allocation as the second argument. The first case executes the copy as a pageable transfer. However, in the first scenario, CUDA performs its own host memory allocation and copy to host memory anyway. With system memory allocation having a small cost in terms of execution time, it is therefore advantageous in production code to pre-allocate a block of page-locked memory and use that during ML workload execution.

For the experiment environment, the code uses the explicit allocation of memory for a page-locked transfer because it allows the isolation and timing of only the step where data is moved across the PCIe bus from system memory. Otherwise, it would be difficult to determine if latency is being encountered at the system memory or PCIe level once outside load is added to the system. In production code, this would be controlled for by designing code for the device and system RAM size and pre-allocating all the required memory ahead of time.

The code in Figure 9 just needs a brief explanation. Since the experiment code

Figure 9: Python method for moving data to main memory

```

def np_to_hmem(src, dest):

source = src.ctypes.data_as(ctypes.POINTER(ctypes.c_float))

destination = dest.ctypes.data_as(ctypes.POINTER(ctypes.c_float))

size = src.size * ctypes.sizeof(ctypes.c_float)

ctypes.memmove(source,destination,size)

```

is isolating the movement of data over the PCIe bus, the copy to system memory needs to be manually implemented. This is accomplished using the python ctypes functionality, specifically with the ctypes.memmove() function, which is required to ensure that the memory allocated by PyCUDA will match what is seen by the CUDA API when it executes. Effectively, ctypes.memmove() will populate the memory it is told to with C efficiency and ruthlessness: immediately and without regard for what is there already.

Finally, in terms of specifying --single vs. --batch, there are some implementation details that bear explaining. Single mode grants more flexibility in terms of the amount of variance between individual element size, number of workers, and number of elements. Starting the application with --single 128 -w 2 -e 100 for example, would create a list of 100 elements of 128 MB in size, use two workers, and run for one iteration (the default). Due to the limitations of this implementation in terms of using the multiprocessing library, in --batch mode, the application can only run using a single worker. This is a result of not being able to share a memory pool among child processes. When in batch mode, the worker flag is set to one, even if a larger number of workers is specified. This means that when wishing to test batch mode, it is recommended to pick a relatively high element size, say a minimum of 1 gigabyte.

#### 3.5.1 PCIe Bandwidth

PCIe bandwidth is traditionally expressed in GT/s, or gigatransfers per second. A transfer refers to the number of operations performed per second by a particular device across a data channel. While this might seem unusual for a computing device, it's important to remember that PCIe is a multi-layered standard with multiple points of interaction. The PCIe standard defines a transaction layer, a data link layer, and a physical connection layer. In other words, the maximum speed of a PCIe device is a function of its PCIe revision, and the number of PCIe lanes that a device uses.

The most important consideration for this thesis is the number of lanes that a device uses. A PCIe device will be classified as a 1x, 2x, 4x, 8x, 16x, or uncommonly, a 32x device. Each PCIe lane has two pairs of wires used for sending and receiving data, and as the number of lanes on a device increases so too does its throughput. With PCIe 3.0, each lane can operate at a transfer rate of 8 GT/s, or 2.0 GB/s total bandwidth per lane for send and receive. That is a bit of an important detail as well — bandwidth is the total data transfer for both directions, so the maximum throughput for send is 1.0 GB/s and receive is also maximum 1.0 GB/s. This works out to a specification maximum bandwidth of 15.8 GB/s in a 16x slot.

There is also transactional overhead involved with PCIe data movement. In benchmarking this during the development phase, it was observed that in general 6.1 GB/s is the average speed at which data can be sent, and 6.5 GB/s for receiving data from a PCIe device when the total data sent was greater 1024 MB. This works out to average about 12.6 GB/s total, a number that becomes more stable as the size of the data transfer increases. Results here correlate with Intel's PCI Express High Performance Reference design, which indicates that the expectation is that throughput should increase and stabilize as the size of the payload increases (Intel, 2018). Please see Chapter V, specifically the baselines chapter for a more complete picture of what this looks like.

As a final point on the PCIe specification — while the PCIe 4.0 specification has been ratified and was released in its final form in summer 2017, the first systems from AMD and Intel to use it were only released in January 2019 and mid 2020 respectively. Few GPUs support the 4.0 specification at the publishing date of this paper, and it may be a couple more years before support is widespread.

There are a few final things to say about PCIe that have been a part of the specification from its very first version. The total number of PCIe lanes that a computer has is a sum of how many lanes are provided by the CPU and how many are provided by the motherboard chipset via electrical switches. What this means is that there is a limit to how many lanes are provided for peripheral devices, and furthermore, available lanes will be divided among the various slot types. Take for example Intel's Haswell chip, which defines a maximum of 32 PCIe lanes provided by the CPU. If a motherboard vendor decides to divide the PCIe lanes in an arrangement such as 16x, 8x, 4x, 2x, 1x, 1x, the ability to have multiple GPUs running at their rated speed is limited. The PCIe specification allows for a slot to accept larger cards than actually connected lanes, and therefore it is important to validate that a card is connected to the correct slot in order to maximize its performance. In the example above, only one GPU would be able to run at the full 16x speed, and any subsequent devices added would have their throughput halved.

# 3.5.2 Multiple GPU scenarios

One of the switches for the benchmark application, -d or --num\_devices, allows the user to control the number of CUDA devices the application will use. This option is available as a convenience for environments where PCIe throughput cannot be reached with a single device. As an example, these may be environments that have PCIe 4.0, but older GPUs that are not capable of saturating the bus. When this option is in use, the application will assign GPUs to workers in a round-robin scheme. In limited testing, this functions fine and definitely ensured that the test system was always completely saturating the PCIe bus. The default is set to one, and the application by design does not respect the system environment variable CUDA\_DEVICES, which can be used to mask or enable devices as needed.

For environments that want to use a specific CUDA device, pass the argument -c cuda\_device\_id. CUDA devices are 0-indexed by the NVIDIA driver and can be identified by using the --hwinfo flag from the benchmark application. This will limit the application to using the single specific GPU, the application does not implement a way to control for more than one specific device.

## 3.6 Simulating non-ML workloads

Since the experiment environment is concerned with simulating general purpose virtualization environments, some benchmarks need to be run in an environment that has non-ML workloads running. In the interest of trying to keep the scope manageable the experiment environment does not try and set up numerous various workloads like databases or web servers. Rather, stress-ng is used to tax VMs at various CPU/memory/bus levels. These will generally try to adhere to some high-level usage patterns, such as databases having high disk I/O and memory transactions, or web servers that run at a constant CPU utilization and will be noted as such in results.

Non-ML workloads can be deployed in batches or clusters running various workloads types. Terraform can be used with the various template files provided to deploy different swarms of generic traffic nodes. Once they are provisioned, use the

| Description     | Switches                                                           |

|-----------------|--------------------------------------------------------------------|

| CPU stress only | –cpu-load 50 –cpu-load-slice 0                                     |

| Add memory      | –cpu-load 50 –vm-bytes 1G –cpu-load-slice 0 -vm 4 –cpu 24          |

| Add NUMA stress | –cpu-load 50 –vm-bytes 1G –cpu-load-slice 0 -vm 4 –cpu 24 –numa 24 |

Figure 10: Load Generator Workload Types

bash scripts to issue commands to them. Since an unknown number VM instances may be spawned for this purpose, the test automation does not depend on networking being available. Rather, all the VM instances can be controlled using an open source component written in the Go language called govc. govc is part of the govmomi library, which is an implementation of the VMware API using Google's Go language (MacEachern, 2021). govc allows the user to run commands on a VM without network access by making use of the hypervisor to guest interface via VM support tools. The bash scripts are tuned to use the Terraform outputs and dispatch commands to a group of these non-ML workloads VMs using govc.