# Advanced Metallization Processes for Complex Structures in Microelectronics by Direct-Liquid-Evaporation Chemical Vapor Deposition

Permanent link

http://nrs.harvard.edu/urn-3:HUL.InstRepos:39987890

### Terms of Use

This article was downloaded from Harvard University's DASH repository, and is made available under the terms and conditions applicable to Other Posted Material, as set forth at http://nrs.harvard.edu/urn-3:HUL.InstRepos:dash.current.terms-of-use#LAA

# **Share Your Story**

The Harvard community has made this article openly available. Please share how this access benefits you. <u>Submit a story</u>.

<u>Accessibility</u>

## Advanced Metallization Processes for Complex Structures in Microelectronics by Direct-Liquid-Evaporation Chemical Vapor Deposition

A dissertation presented

by

Jun Feng

to

#### The Department of Chemistry and Chemical Biology

in partial fulfillment of the requirements

for the degree of

#### **Doctor of Philosophy**

in the subject of

#### Chemistry

Harvard University

Cambridge, Massachusetts

June 2017

© 2017 – Jun Feng

All rights reserved.

#### Advanced Metallization Processes for Complex Structures in Microelectronics by Direct-Liquid-Evaporation Chemical Vapor Deposition

#### Abstract

With the rapid advancement of semiconductor industry, fabrications of complex microelectronic devices are going beyond the conventional planar geometries into three-dimensionality (3D). Besides, since the emerging of flexible and wearable consumer electronics, it is also desired to break the limitation of conventional rigid electronic devices and transform toward flexible devices. In order to provide fundamental frameworks for 3D electronics and flexible electronics, strategies to create complex structures at nano-/micro-scales, including interconnect architectures, need to be developed. For nano-scale high-aspect-ratio metal interconnects, great challenges are yet to be overcome because of the rigorous requirements of high-precision fabrication, high metal uniformity and conformality, as well as special liner and capping layers. Promising solutions to these challenges are offered by direct-liquid-evaporation chemical vapor deposition (DLE-CVD) technique developed in recent years. DLE-CVD is able to quantitatively deliver high-throughput precursor into deposition chambers with high controllability and vaporization efficiency, which provides high-quality metallization layers even deep inside complex structures, or on flexible polymer substrates.

In this thesis, advanced metallization processes based on DLE-CVD are described. The deposited metallic materials from these processes, including cobalt (Co), nickel (Ni),

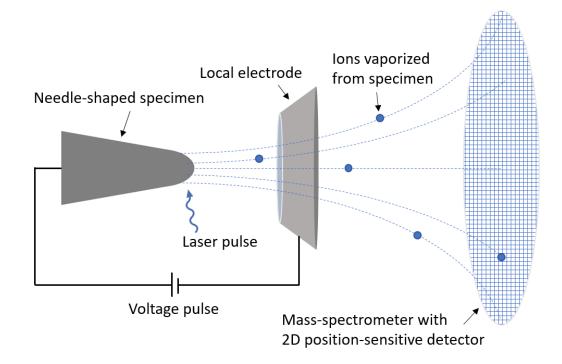

iii

nickel silicide (NiSi) and copper (Cu), are thoroughly characterized and studied by electron microscopies, elemental analysis tools, atom probe tomography (APT), etc. Applications of these metallization processes in 3D electronics are demonstrated directly on high-aspect-ratio structures fabricated by reactive ion etching (RIE) technique. Furthermore, potential utilization of DLE-CVD processes to metallize the surface of polymer fibers, which can be used as flexible interconnects, is also discussed.

Chapter 1 provides a background introduction to the basics of metallization strategies and applications, and discusses potential applications of these strategies.

Chapter 2 describes detailed methods to fabricate well-defined high-aspect-ratio structures, and introduces an intriguing self-smoothing phenomenon observed in aluminum-catalyzed silicon dioxide (SiO<sub>2</sub>) atomic layer deposition (ALD), which can be used to create smooth-wall trench structures with ultrahigh aspect ratios up to 100:1.

Chapter 3 presents in-detail study of DLE-CVD cobalt (Co), in which the deposition process of highly conformal, pure, and smooth nanocrystalline Co metal films is described. All-around encapsulation of nano-scale copper (Cu) interconnect by DLE-CVD Co is demonstrated to be an effective strategy to enhance interconnect reliability, stability, and operation life.

In chapter 4, APT technique is used to study our metallic materials deposited by DLE-CVD. Compositional and structural information are acquired with atomic resolution.

And chapter 5 explores the potential application of DLE-CVD Co as the initial metallization layer on polymer fibers, to create conductive flexible interconnects.

iv

### Table of Contents

| Chapt  | er 1                     | Introduction                                                           | 1   |

|--------|--------------------------|------------------------------------------------------------------------|-----|

| 1.1    | Me                       | tallization Processes in Modern Microelectronics                       | 1   |

| 1.     | 1.1                      | The Role of Metallic Materials in Microelectronics                     | 1   |

| 1.     | 1.2                      | Vapor Deposition Methods for Metallic Materials                        | 5   |

| 1.     | 1.3                      | Thin Film Deposition in High-Aspect-Ratio Structures                   | 7   |

| 1.2    | Dire                     | ect-Liquid-Evaporation (DLE) CVD of Metallic Materials                 | 11  |

| 1.     | 2.1                      | Concepts and Advantages of DLE-CVD                                     | 11  |

| 1.     | 2.2                      | DLE-CVD Precursors and Processes for Metal Thin Films                  | 13  |

| 1.3    | Sur                      | face Metallization of Polymer Fibers                                   | 15  |

| 1.     | 3.1                      | Conductive Polymer Fibers and Flexible Electronics                     | 15  |

| 1.     | 3.2                      | Surface Metallization Methods for Polymeric Materials                  | 15  |

|        |                          |                                                                        |     |

| Chapt  | er 2                     | Self-Smoothing Al-Catalyzed SiO $_2$ ALD for Smooth-Wall Vertical Tre  | nch |

| Struct | ures                     | with Ultrahigh Aspect Ratios                                           |     |

| 2.1    | Intr                     | oduction                                                               | 18  |

| 2.2    |                          | rication of High-Aspect-Ratio Structures by Reactive Ion Etching (RIE) |     |

| 2.2    |                          | Catalyzed SiO <sub>2</sub> ALD on High-Aspect-Ratio Structures         |     |

|        | .3.1                     | Al-Catalyzed SiO <sub>2</sub> ALD Process and Smoothing Mechanism      |     |

|        | .3.2                     | Smooth-Wall Ultrahigh-Aspect-Ratio Trench Structures                   |     |

| 2.4    |                          | nclusions                                                              |     |

| 2.1    | 001                      |                                                                        |     |

| Chapt  | er 3                     | DLE-CVD of Nano-Crystalline Co Metal for Nanoscale Cu Interconne       | ect |

| Encap  | sulat                    | ion                                                                    | 37  |

| 3.1    | Intr                     | oduction                                                               | 37  |

| 3.2    | 3.2 Experimental Methods |                                                                        | 40  |

| 3.3    | Cha                      | aracterizations of Nano-Crystalline Co Thin Films                      | 44  |

| 3.3.1  |                          | Growth Characteristics                                                 | 44  |

| 3.3.2  |                          | Composition of DLE-CVD Co                                              | 48  |

| 3      | .3.3                     | Crystallinity and Morphology Studies of DLE-CVD Co                     | 49  |

| 3.4    | Eval   | uation of DLE-CVD Co as Liner Material for Cu Interconnects             | 54  |

|--------|--------|-------------------------------------------------------------------------|-----|

| 3.     | 4.1    | Co Liner Against Cu Diffusion                                           | 54  |

| 3.     | 4.2    | All-Around Encapsulation of Nano-Scale Cu Wire with DLE-CVD Co          | 56  |

| 3.5    | Cond   | clusions                                                                | 59  |

|        |        |                                                                         |     |

| Chapte | er 4   | Atom Probe Investigations of DLE-CVD Metals                             | 60  |

| 4.1    | Intro  | oduction                                                                | 60  |

| 4.2    | APT    | of DLE-CVD Co Metal for Compositional Studies                           | 62  |

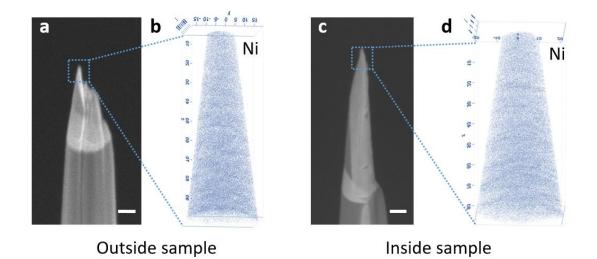

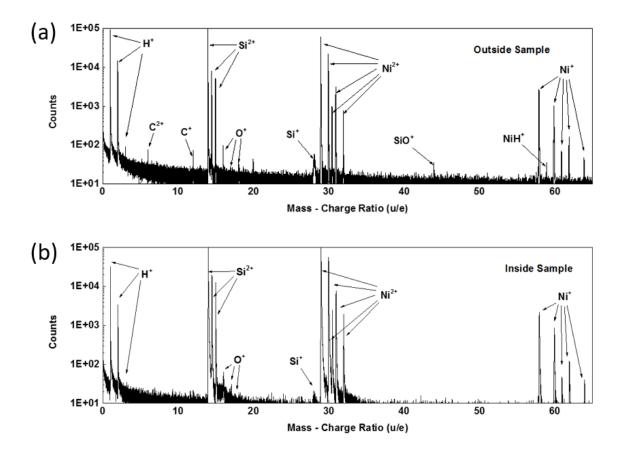

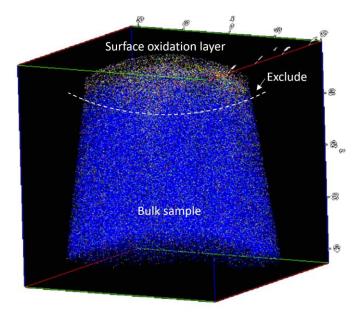

| 4.3    | APT    | of Ni and NiSi from Deep Inside of High-Aspect-Ratio Trenches           | 67  |

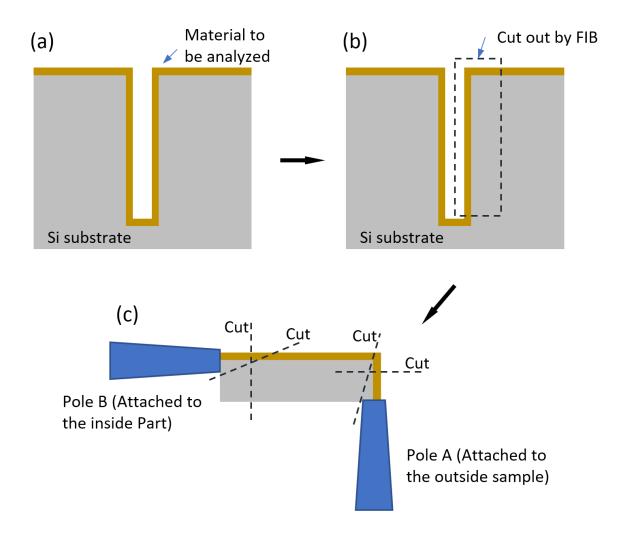

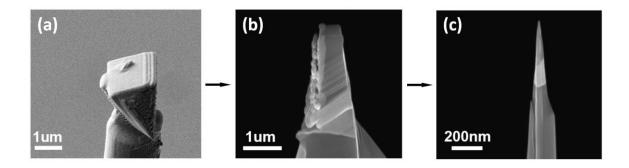

| 4.     | 3.1    | Ni and NiSi Sample Acquisition from Deep Trench Structures              | 67  |

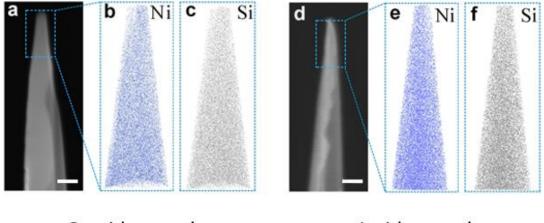

| 4.     | 3.2    | APT Parameters and Reconstruction Results of Ni and NiSi                | 71  |

| 4.4    | Cond   | clusions                                                                | 76  |

|        |        |                                                                         |     |

| Chapte | er 5   | Surface Metallization of Polymer Fibers for Flexible Electronics        | 77  |

| 5.1    | Intro  | oduction                                                                | 77  |

| 5.2    | Adva   | antage of DLE-CVD for the Surface Metallization of Polymer Fibers       | 78  |

| 5.3    | Expe   | erimental Details                                                       | 79  |

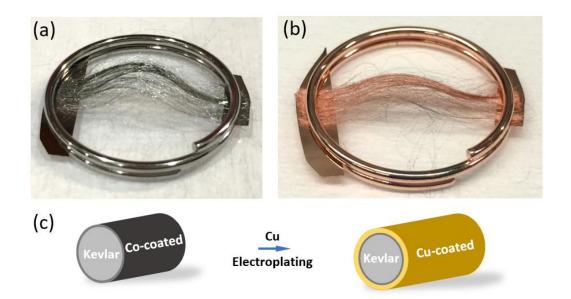

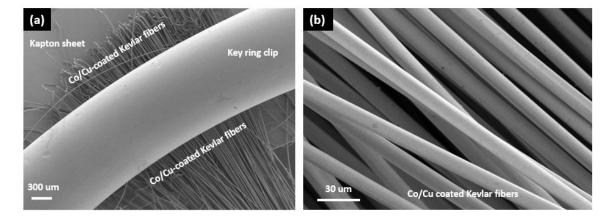

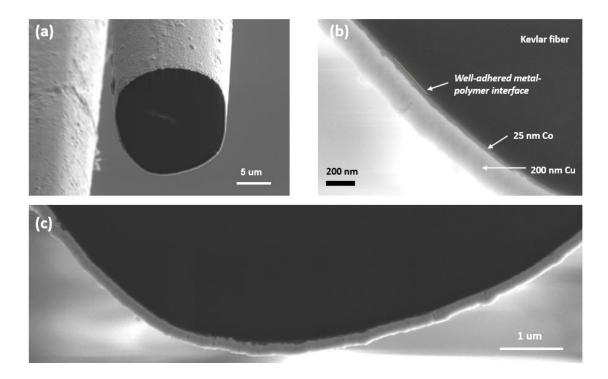

| 5.4    | DLE-   | -CVD Metallization on Kevlar Fibers and Its Challenges                  | 80  |

| 5.5    | Elec   | troplating on DLE-CVD Co Seeded Kevlar Fibers                           | 85  |

| 5.6    | Dem    | nonstration of Conductivity and Flexibility of Metallized Kevlar Fibers | 92  |

| 5.7    | Con    | clusions                                                                | 94  |

|        |        |                                                                         |     |

| Refere | ence   |                                                                         | 95  |

|        |        |                                                                         |     |

| Appen  | idix A | Co/W DLE-CVD Reactor Operation Procedures                               | 106 |

| Appendix B | Ni DLE-CVD Reactor Operation Procedures     | 106 |

|------------|---------------------------------------------|-----|

| Appendix C | Cu/Mn DLE-CVD Reactor Operation Procedures1 | 06  |

#### Acknowledgements

I would like to express my earnest gratitude to everyone who accompanied me in the journal toward today, the past five years at Harvard were so enjoyable and memorable with all your help, support, friendship, and love.

I would like to first thank my advisor, Professor Roy G. Gordon, who had been extremely supportive, enlightening and understanding during my doctoral studies. Roy is more than a great scientist, but also a great educator, since he always teaches us the way to learn, besides what to learn. He taught me that, as scientists, we should work on what we want and need, rather than on what we can do. His proactive attitude and restless efforts toward building a better world with science and technology, has been giving us the best motivation to improve ourselves. It is my greatest honor to have Roy's support and guidance in my research career.

I hope to thank my committee members, Professor Donhee Ham at Harvard University, and Professor Karen Gleason at Massachusetts Institute of Technology. I was in Donhee's class on electronics five years ago, and learned lots of fundamental knowledge that was frequently used in my research later on. Donhee is very supportive to students and gave me many helpful suggestions in all of my annual GAC meetings in the past five years. Professor Karen Gleason is an extraordinary scientist on CVD and polymer chemistry. Karen is very patient and knowledgeable, and always willing to provide guidance on both research and career developments. She also has been one of my GAC members for three years, and it is my honor to have her in my committee.

I also want to thank all Gordon Group members. Our best administrator Teri Howard, our talented postdocs, Dr. Luke Davis, Dr. Sang Bok Kim, Dr. Eugene Beh, and two of my best friends who recently received their new prefix, Dr. Xiabing Lou and Dr. Chuanxi Yang. All other members, Danny Chua, Lauren Hartle, Rachel Heasley, Lu Sun, Ashwin Jayaraman, Robert Gustafson, Xizhu Zhao, Liuchuan Tong, Aykut Aydin, Kaixiang Lin, Christina Chang and Xian Gong. I want to specifically thank my desk mates Liuchuan and Xian, who have been my best buddies whatever I do, wherever I go. I need to extend my gratitude to all my other friends at Harvard, all of them are the ones who made my life here so colorful and pleasant.

Finally and most importantly, I have to thank my families, my father Dezheng Feng, my mother Yuanhong Wang, and my fiancé Yafang Yang. It is their love that has been the best and strongest courage for me to face any difficulties in life.

Jun Feng Cambridge, Massachusetts June 22, 2017

#### Chapter 1 Introduction

#### **1.1** Metallization Processes in Modern Microelectronics

#### **1.1.1** The Role of Metallic Materials in Microelectronics

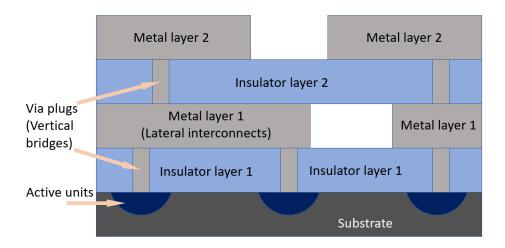

As modern semiconductor devices scale toward the sub-10-nm regime, advanced microelectronic processes require highly efficient integration of multiple functioning parts, including semiconductor channels, insulating layers and metal interconnects.<sup>1-2</sup> In complex microelectronic architectures, active components (transistors, memory cells, sensors, etc) are usually at nano-scale sizes. However, practical applications of these components require intermediate "bridges" to enable access to the small units by larger-scale interfaces. Therefore, multiple layers of interconnects, from the smallest local interconnects to the largest global interconnects, are needed in semiconductor devices. Moreover, since more and more active components are being integrated into smaller areas, it is becoming increasingly challenging to fabricate the "roads" to enable communications among individual functioning units in the extremely complex microelectronic architectures.<sup>3-4</sup> In this regard, metallic material materials that can efficiently conduct electrons are required, for both the "bridges" to grant vertical accessibility and the "roads" to provide lateral interactions among units, as schematically illustrated in Figure 1.1.

Since IBM and Intel first introduced the replacement of aluminum with copper for microelectronic interconnects, tremendous efforts have been put on the developments of copper metallization processes.<sup>5</sup> The lower electric resistivity of copper (16 nOhm  $\cdot$  m)

compared with that of aluminum (28 nOhm · m) makes it possible to achieve faster, smaller and denser microprocessors, because less material is needed for interconnects transporting the same amount of electric current, thus improving the overall efficiency.<sup>6</sup> However, the introduction of copper into microelectronic devices also brought many new challenges, especially the issues caused by the high migration and diffusion rates of copper atoms.<sup>7</sup>

Figure 1.1. Illustration of the functions of different layers of metal interconnects

To overcome this issue, it is important to effectively separate or block copper atoms away from any diffusion-sensitive areas.<sup>8</sup> Tantalum (Ta) and tantalum nitride (TaN) have been widely used in modern microelectronic systems as diffusion barriers to prevent copper atoms from penetrating into dielectric layers or semiconductor channels.<sup>9</sup> Many other metallic nitride materials including titanium nitride (TiN), tungsten nitride (WN), manganese nitride ( $MnN_x$ ), and cobalt nitride ( $CoN_x$ ) are also being developed as copper barriers for better semiconductor device life time and reliability.<sup>10-12</sup>

Another challenge for copper interconnect technology is that copper does not form Ohmic contact with silicon, which is due to the misalignment between the work function of copper and the fermi level of silicon.<sup>13</sup> Thus, intermediate metallic materials are needed to connect silicon semiconductor devices with upper-level copper interconnects. Metal silicides, including nickel silicide (NiSi), cobalt silicide (CoSi<sub>2</sub>), titanium silicide (TiSi<sub>2</sub>) and platinum silicide (PtSi), are introduced between metal interconnects and active semiconductor contact areas.<sup>14</sup> For example, in order to form ohmic contact to silicon, titanium silicide can be formed at the silicon surface by depositing a thin layer of titanium metal onto the contact area, followed by 700~850 °C annealing.<sup>15</sup> However, it remains a challenge to controllably form high-quality, low-resistance, and conformal silicide at lower temperatures that are compatible with current semiconductor manufacturing processes.

For the connection between silicide contacts and vias, tungsten (W) plug processes have been developed in current technologies for both front-end and back-end metallization processes as the metal filling.<sup>16</sup> At the 14 nm technology node and beyond, the critical dimension (CD) of contact is less than 25 nm, and could only incorporate about 3 nm of tungsten metal as the plug material.<sup>17</sup> However, tungsten plug filling requires a wetting layer for better nucleation because tungsten does not nucleate well on silicon surfaces.<sup>18</sup> With only a few nanometers of tungsten, it is a great challenge to

form uniform and continuous thin film material for plugs. Also, the conductivity of tungsten dramatically increases as the size shrinks due to surface scattering of electrons.<sup>19</sup> Therefore, cobalt thin film processes have been developed recently to replace tungsten, since cobalt does not require special wetting layer to form continuous film on silicon-based surfaces, and has higher conductivity when fabricated into ultra-small interconnects.<sup>20</sup>

Beyond the plug materials, intermediate and global interconnects are mostly micrometer-scale copper metal wires encapsulated by barrier and liner layers.<sup>21</sup> In modern microelectronic system, these larger interconnects form extremely complicated three-dimensional (3D) architecture and require highly conformal coating of metal materials into high-aspect-ratio structures.<sup>22</sup> Of note, gas phase metal coating techniques usually have low deposition rates, thus giving unfavorably low productivity. To increase efficiency, it is a common strategy to utilize a vacuum-deposited metal thin film as seed layer, then use electroplating to fill up the interconnects.<sup>23</sup> Therefore, it is crucial to develop highly conformal metal seed layer deposition processes to enable electroplating on complex 3D interconnect architectures. Besides, the design and fabrication of vertical metal interconnects also requires proper insulating and barrier layers, which are also parts of the great challenges for the advancement for copper interconnect systems.

Overall, metallic materials are crucial parts for semiconductor devices, which enable the access and utilization of ultra-small active units, and comprise the complex

electronic communication architectures within the devices. In the past decades, although substantial advancements have been achieved with copper interconnect technology, challenges remain for the realization of better-performance, higher-density, and higher-efficiency electronic devices in the future.

#### **1.1.2** Vapor Deposition Methods for Metallic Materials

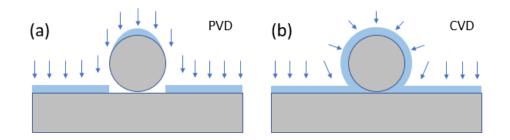

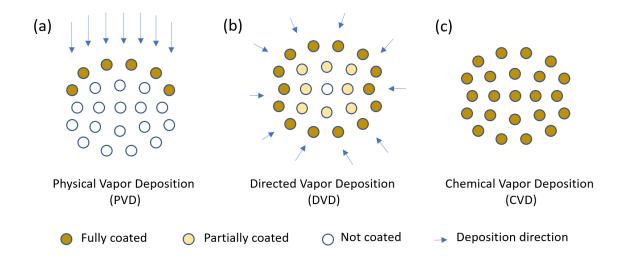

Metallic materials can be deposited from vapor by either physical methods or chemical methods. In physical vapor deposition (PVD) methods, materials are directly vaporized by heat (thermal evaporation), laser (pulsed layer deposition), electron beam (e-beam evaporation), or ion/plasma bombardment (sputtering), and then re-condense onto the sample substrates.<sup>24</sup> Since PVD methods directly take out materials from a metal target source and deposit them into thin films, the chemical composition of deposited film can be usually guaranteed by the purity of target sources, and the deposition rate can also be readily controlled by the intensity of excitation (temperature, e-beam current, laser intensity, etc.).<sup>25</sup> In this regard, PVD offers high controllability and good reproducibility, as well as high deposition rates, which are all very favorable for production-level industrial applications. However, for those applications that need to use uncommon materials, it may be difficult and cost-ineffective to make the target source for PVD processes. Moreover, PVD processes are not capable of conformal coating, which substantially limits their applications when it comes to the coating of complex structures.<sup>26</sup>

On the other hand, chemical vapor deposition (CVD) is a coating technique by inducing chemical reactions on sample surfaces to form desired materials. Unlike PVD processes, which only use one source material, CVD processes usually involve two or more source materials called precursors.<sup>27</sup> For example, tungsten nitride (WN) can be deposited by introducing gas-phase tungsten fluoride (WF<sub>6</sub>) and ammonia (NH<sub>3</sub>) together into deposition chamber at the same time.<sup>28</sup> By proper process development, the chemical deposition reactions can be set to only take place on sample surfaces to produce thin films, rather than to produce powders with gas-phase reactions.<sup>29</sup> Since CVD processes are surface-dependent, this technique can produce highly conformal coatings even in very high-aspect-ratio structures, which can hardly be achieved with conventional PVD methods.<sup>30</sup> Figure 1.2 shows the difference in the coating characteristics between PVD and CVD processes. Also, for those materials that are difficult to be made into PVD targets, CVD is also a practical alternative. Generally, CVD offers highly conformal and uniform coatings of a large variety of chemical compounds, which is highly favorable for the manufacturing of modern 3D microelectronic systems.<sup>31</sup> However, CVD processes usually have lower deposition rates, higher process temperature, and sometimes lower-purity thin films compared with PVD methods. Therefore, there are still many challenges in the development of advanced CVD processes for practical industrial applications.

Figure 1.2. Difference between the deposition characteristics of (a) PVD and (b) CVD.

#### 1.1.3 Thin Film Deposition in High-Aspect-Ratio Structures

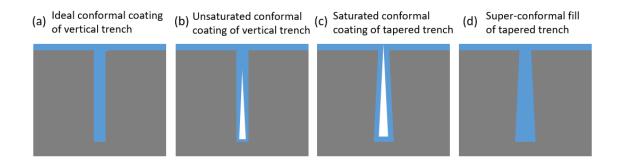

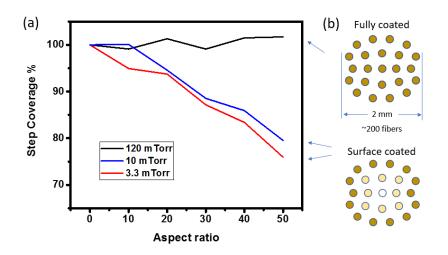

As discussed in previous context, CVD processes offer the feasibility of depositing thin films into complex structures. Nevertheless, proper designing of CVD processes is still required to realize the coating of structures with super-high aspect ratios.<sup>32</sup>

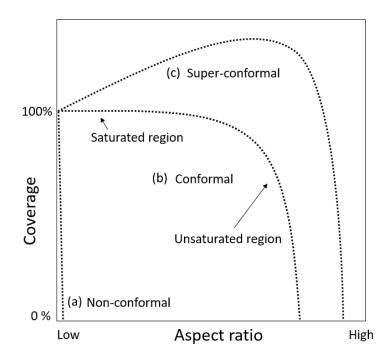

Figure 1.3. Different filling behaviors with different conformal coating processes. (a) Ideal fill of an ideally vertical trench; (b) Partial fill of a vertical trench by unsaturated conformal deposition process, leaving a void in the trench; (c) Partial fill of a tapered trench with sloped side walls by saturated conformal deposition process, leaving a void in the trench; (d) Complete super-fill of a trench with sloped side walls by superconformal deposition process. Microscopically, conformal coating can be achieved on nonplanar substrates either when the adsorbed precursor molecules can diffuse laterally on sample surfaces, or when the precursors have low sticking coefficients and tend to re-emit into the gas phase.<sup>33-34</sup> The prerequisite for conformal coating by either mechanism is that precursor molecules need to physically diffuse deep into any complex structures, e.g. holes or trenches. When the precursor concentration is not high enough to saturate all sample surface, step coverage will gradually decrease as the aspect ratio increases, thus causing a tapered deposition profile, which we here define as an unsaturated region as shown in Figure 1.3(b) and Figure 1.4(b).<sup>35</sup>

Figure 1.4. Illustration of different step coverage behaviors of non-conformal,

conformal, and super-conformal thin film deposition processes.

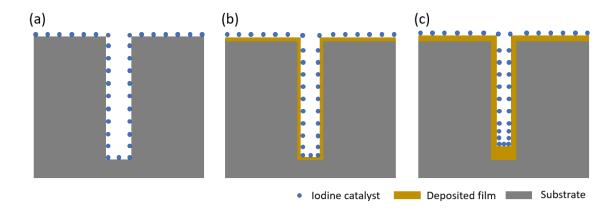

Practically, it is highly challenging to fully saturate entire sample surfaces and create identical thickness at all aspect ratios. Therefore, super-conformal deposition processes (as depicted in Figure 1.3d and Figure 1.4c) were developed in recent years to achieve complete fills of trench or hole structures. There are generally two strategies for super-conformal coating: 1. Introducing a catalyst that can accelerate deposition rate at the bottom of a trench;<sup>36</sup> 2. Special designing and utilizing the diffusivity difference of co-reactants to kinetically increase growth rate at the deeper parts of a trench or hole.<sup>32</sup>

With the catalyst method, a special chemical needs to be introduced into the deposition chamber prior to the deposition process. For example, ethyl iodine can

catalyze the Cu and Mn CVD processes with amidinate precursors.<sup>11</sup> As shown in Figure 1.5, iodine concentration keeps increasing at the bottom of the trench as the deposition continues, thus further increasing the growth rate at the bottom of high-aspect-ratio structures.

With regard to the kinetic designing method for the implementation of superconformal coating, no additional chemical need to be introduced into the deposition process. However, this method has very specific requirements for the selection of precursors. For example, super-conformal MgO growth can be realized with Mg(DMADB)<sub>2</sub> and H<sub>2</sub>O precursor, because of their competitive adsorption behaviors on sample surfaces, as well as their difference in diffusivities, which are all hard requirements on the physical properties of the precursor, limiting its applications with wider variety of precursors for different purposes.<sup>32</sup>

Conformal and super-conformal thin film deposition techniques are highly important for future developments of advanced microelectronics, because higherdensity package of semiconductor devices require the incorporation of functional materials onto three-dimensional frameworks with high aspect ratios.<sup>37-38</sup> However, currently developed conformal and super-conformal metal deposition processes are very limited. Many available processes either requires expensive apparatus or are unable to fulfill requirements (conformality, purity, deposition rate, etc.) for cuttingedge electronic devices manufacturing applications. Further scientific and technological developments in conformal coating techniques in complex structures are needed for the

design and fabrication of next-generation electronics. In chapter 2 of this thesis, a superconformal self-smoothing Al-catalyzed SiO<sub>2</sub> ALD process is described, and used to fabricate smooth-wall trench structures with ultrahigh-aspect-ratio structures.

#### 1.2 Direct-Liquid-Evaporation (DLE) CVD of Metallic Materials

#### 1.2.1 Concepts and Advantages of DLE-CVD

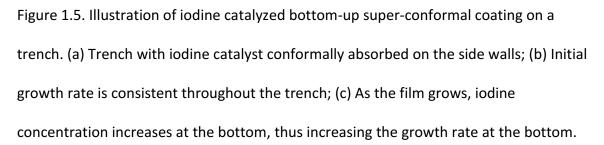

Direct-liquid-evaporation chemical vapor deposition (DLE-CVD) is a CVD process with DLE precursor delivery system. In contrast to conventional CVD with bubbler sources of vapor, liquid precursor solutions in DLE-CVD systems are stored unheated and directly injected into the heated evaporation region.<sup>39</sup> The DLE process heats a precursor only very briefly, thereby avoiding decomposition that can occur when a conventional bubbler is heated for long time, decreasing unwanted carbon or organic contamination in the films. Moreover, the precursor delivery rate of DLE-CVD is controlled by the very stable injection rate of a liquid precursor or a precursor solution, instead of the variable precursor vapor pressure found in conventional bubblers.<sup>40</sup> These features of DLE-CVD enable formation of films with much higher conformality and better reproducibility than conventional CVD systems.

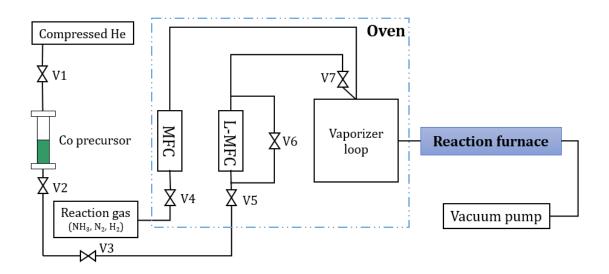

As illustrated in the diagram shown in Figure 1.6, precursor solution of DLE-CVD is stored outside of an oven, and delivered into the deposition chamber after evaporating in a heated vaporization loop. The precursor delivery rate is stably controlled and measured by a liquid mass flow-controller (MFC) immediately before it flows into the

vaporization loop. With this design, precursor delivery rates of DLE-CVD are not limited by precursor vapor pressures like traditional CVD is. Therefore, precursors in a DLE-CVD deposition chamber can reach much higher gas-phase concentrations and saturate all surfaces in complex structures, minimizing the growth rates difference at positions with different aspect-ratios.<sup>41</sup>

Figure 1.6. Diagrams showing the design difference between the precursor delivery

systems between (a) conventional CVD and (b) DLE-CVD system.

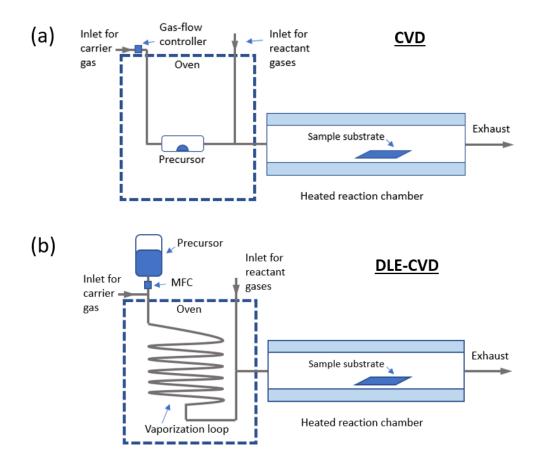

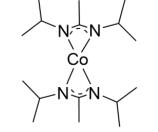

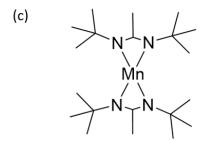

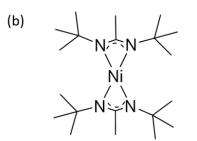

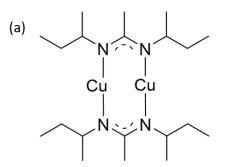

#### 1.2.2 DLE-CVD Precursors and Processes for Metal Thin Films

In our previous works, four metal DLE-CVD processes have been developed with four different precursors, which are summarized in Figure 1.7. So far, all precursors used for our DLE-CVD depositions are metalorganic compounds with acetamidinate legends. At room temperature, these precursor compounds are all solids. Precursor solutions are made by dissolving solid-state precursors in inner organic solvents, like tetradecane and trihexylamine. These solvents are chosen because they have vapor pressure similar to the precursors, and does not decompose or interact with precursors or other co-reactants during the deposition processes.<sup>42</sup>

(a)

N,N'-(diisopropylacetamidinate) Cobalt(II)

N,N'-(ditertbutylacetamidinate) Manganese(II)

N,N'-(ditertbutylacetamidinate) Nickel(II)

N,N'-(diisobutylacetamidinate) Copper(I) dimer

Figure 1.7. Precursors used in our developed DLE-CVD processes.

For cobalt, nickel and copper metal depositions, we used tetradecane as the solvent and performed vaporization at 150 °C under vacuum of 5 to 30 Torr. Deposition chamber temperatures were set to be in the range 180 ~ 280 °C, while the actual sample holder is heated to be 5 ~ 15 °C higher than the chamber temperature by an embedded heater, in order to form thin films on sample surfaces rather than the chamber wall. Deposition pressure is controlled and maintained at 5 ~ 30 Torr by a butterfly valve, with continuous flows of carrier gas and co-reactant gases. Copper amidinate precursor has high reactivity directly with hydrogen, but nickel and copper amidinate precursors require the introduction of a certain amount of ammonia to deposit a metal film. The process for manganese metal deposition is mostly the same as that of copper, but with slightly higher chamber temperature (230 ~ 300 °C), indicating that the manganese amidinate precursor has slightly lower reactivity with hydrogen than the copper precursor.<sup>43</sup>

Overall, in order to develop DLE-CVD processes for different kinds of metal materials, proper designing and selection of solvent, vaporization temperature, substrate temperature, deposition pressure, and co-reactant gas flows are highly important. In chapter 3 of this thesis, detailed studies of Co DLE-CVD parameters and deposition characteristics will be discussed. Also, in chapter 4, atom probe tomography (APT) characterizations are used to study the thin films deposited by DLE-CVD processes at atomic resolution.

#### **1.3** Surface Metallization of polymeric materials

#### **1.3.1** Conductive Polymer Fibers and Flexible Electronics

While silicon-based electronics revolutionized information carriers by steering away from papers toward flat displays, it also sacrificed the mechanical flexibility and robustness of the traditional media.<sup>44</sup> In this regard, flexible electronics is emerging as a solution to bring back the advantageous features of paper materials.<sup>45-46</sup> In addition to the complex interconnecting architectures as silicon-based electronics requires, flexible electronics further demands high flexibility and mechanical strength of its interconnects.<sup>47-49</sup> Several potential strategies to fabricate flexible interconnects have been reported in recent years, including carbon nanotube yarns,<sup>50</sup> reduced graphene oxide fibers,<sup>51</sup> silver nanowire coatings,<sup>52</sup> conducting polymers,<sup>53</sup> and metallization of polymer fibers,<sup>54</sup> etc. Among these strategies, direct surface metallization of commercial polymer fibers offers the advantage of higher scaling-up feasibility, and better inheritance of the well-established mechanical performance of polymer cores.<sup>55</sup> Nevertheless, it remains a great challenge to develop efficient metallization methods for the formation of uniform and smooth all-around coatings on densely packed fiber yarns or threads.

#### **1.3.2** Surface Metallization Methods for Polymeric Materials

To achieve high-quality surface metallization of insulating polymer fibers, extensive studies have been conducted on polymer surface processing and metal deposition techniques.<sup>56-57</sup> Of note, fibers are high-aspect-ratio structures morphologically, which brings the need of conformal coating methods, rather than traditional anisotropic deposition techniques like thermal evaporation and sputtering.<sup>58</sup> Electroless deposition and other solution deposition methods were widely used for metallization of insulating objects, but liquid-phase methods usually either require toxic chemical solutions or produce relatively weakly adhered metal/polymer interfaces, which is not favorable for industry-scale flexible electronic applications.<sup>59</sup>

Figure 1.8. Deposition characteristics of PVD, DVD and CVD on a bundle of polymer fibers from a cross-section view.

Another commercialized coating method for fiber structures is directed vapor deposition (DVD), which can make near-conformal metal depositions onto thick fiber

(>100 um diameter) arrays with large fiber-to-fiber spacing (>1 mm).<sup>60</sup> Whereas for the metallization of smaller fibers with higher densities, i.e. higher aspect-ratios, DVD method still could not achieve satisfying results.<sup>61</sup> In this regard, chemical vapor deposition (CVD) of metal is a possible technique to accomplish the challenge of all-around coating of fibers, since it provides highly conformal and high-quality coatings even in very high-aspect-ratio structures.<sup>62</sup>

Figure 1.8 illustrates different gas-phase deposition characteristics of PVD, DVD, and CVD on fiber bundles from a cross-section view. Although CVD is a highly promising technique to create high-quality coatings on fibers, traditional CVD metal depositions require either high temperature (>200 °C) or result in inadequate step coverage in complex structures with higher than 10:1 aspect ratios.<sup>63</sup> Therefore, further development of CVD metal deposition technique is needed to bring CVD to practical use for polymer fiber metallization applications. In chapter 5 of this thesis, we report the utilization of DLE-CVD technique for the metallization of polymer fibers and fiber bundles, as well as the characterizations of coated fibers and their potential applications in flexible electronics.

### Chapter 2 Self-Smoothing Al-Catalyzed SiO<sub>2</sub> ALD Process for Smooth-Wall Vertical Trench Structures with Ultrahigh Aspect Ratios

#### 2.1 Introduction

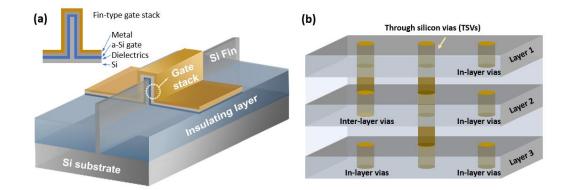

In modern ultra-large-scale integrated (ULSI) architectures, blocks with different functionalities are connected three-dimensionally. Thus, semiconductor devices and interconnects must be made inside structures with high aspect ratios.<sup>64-65</sup> For example, fin-type field-effect transistors (Fin-FET) with high-aspect-ratio silicon fins need conformal coating of dielectrics, amorphous silicon (a-Si) gate, as well as the metal contacting with a-Si gates, as illustrated in Figure 2.1(a). Also, in multi-layer electronics, long through-silicon vias (TSVs) with ultra-small diameters are necessary to form contact with silicon devices on the substrate, as in Figure 2.1(b).<sup>66</sup> All these architectures require proper designing and fabrication of complex high-aspect-ratio structures.

Figure 2.1. (a) Schematic illustration of conformal gate stack coating applied on Fin-FETs; (b) Vertical vias, including through silicon vias (TSVs), formed inside high-aspect-ratio hole structures in multi-layer silicon devices.

In traditional semiconductor industry, 3D high-aspect-ratio interconnects are very difficult to process because of the anisotropic nature of industrially available physical vapor deposition techniques.<sup>67</sup> Moreover, to achieve 3D microelectronic architectures, complex structures need to be fabricated on silicon substrates. In manufacturing, these structures can serve as the template for the formation of high-aspect-ratio metal interconnects. While in research and development, these structures can be used as test structures to evaluate step coverage of a conformal deposition technique like DLE-CVD.

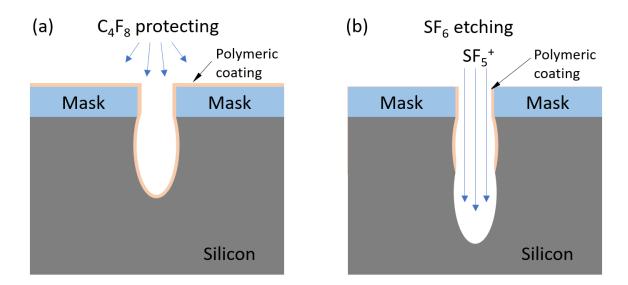

There are many strategies to fabricate high-aspect-ratio structures on silicon substrates.<sup>68</sup> For example, uniform vertical trenches with aspect ratio as high as 16:1 can be fabricated by a metal-assisted chemical etching (MaCE) method.<sup>69</sup> This method involves a wet chemical etching process with HF-H<sub>2</sub>O<sub>2</sub> and pre-patterned gold thin film catalyst. The gold catalyst increases the etching rate at Au-Si interface, thus resulting in vertical trenches after a certain amount of time. However, this method cannot remove the gold catalyst at the bottom of the trench, and involves wet chemistry that may not be compatible with other microelectronic fabrication processes. Another strategy is the Bosch-type deep reactive ion etching (DRIE). The DRIE process is conducted under vacuum, with pulsing gases alternating between C<sub>4</sub>F<sub>8</sub> and SF<sub>6</sub>.<sup>70</sup> C<sub>4</sub>F<sub>8</sub> provides a conformal protective coating, then a vertically accelerated SF<sub>5</sub><sup>+</sup> ion beam is applied to bombard the bottom of the trench. After repeating the two steps for certain number of cycles, a deep trench structure with a desired high aspect ratio can be achieved.

Although this method requires complicated RIE apparatus, it provides better controllability than wet chemical methods.

As illustrated in Figure 2.2, the Bosch-type RIE mechanism creates trench structures by forming small scallops stepwise, which introduces intrinsic roughness to the side wall. These scallops are usually at the scale of tens of nanometers, which is smaller than the size of previous interconnect vias. However, when ultrafine vias smaller than 20 nm are needed in current and future electronics, these scallops will be a concern.

To crease smoother side walls, we used an Al-catalyzed  $SiO_2$  atomic layer deposition (ALD) process to smoothen these scallops. Interestingly, at the scale of 50-100 nm, the Al-SiO<sub>2</sub> ALD process exhibits a self-smoothing effect, which is similar to the super-

conformal behavior as discussed in Chapter 1 Figure 1.4 and Figure 1.5. This superconformal coating phenomenon is not common for ALD processes because ALD is a selflimited conformal process, which maintains the substrate morphology during the deposition process. Therefore, an investigation into this phenomenon has high scientific significance, and may create new methods to process complex high-aspect-ratio structures with the benefit of this self-smoothing effect.

In this chapter, various kinds of high-aspect-ratio structures are produced by lithography and RIE processes. parameters and methods for these processes are discussed in-detail. An Al-catalyzed SiO<sub>2</sub> ALD process is used to coat the etched structures to further increase their aspect ratios, as well as to smoothen the side walls. To evaluate the self-smoothing effect of Al-catalyzed SiO<sub>2</sub> ALD, special structures with controlled scallop patterns are fabricated as test structures. A possible mechanism for the self-smoothing effect is also proposed to explain the process.

#### 2.2 Fabrication of High-Aspect-Ratio Structures by Reactive Ion Etching (RIE)

To fabricate high-aspect-ratio test structures, proper patterning of silicon substrates is needed to create masks for the RIE process. Usually, photoresist and e-beam resist can be directly used as a "soft mask", while in some cases where higher etching selectivity is required, SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub> are used as "hard masks".<sup>71</sup>

Photolithography can produce micron-scale patterning in a short period of time, while e-beam lithography can produce nanometer-scale patterning but with longer

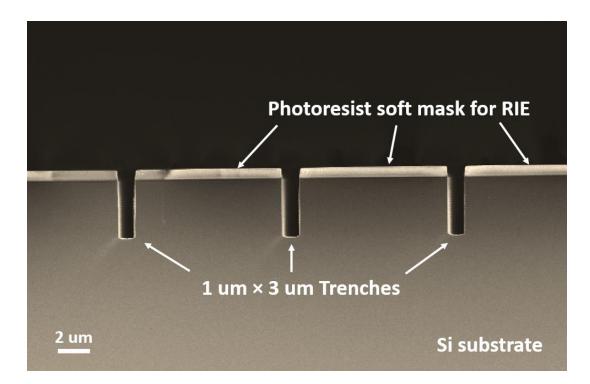

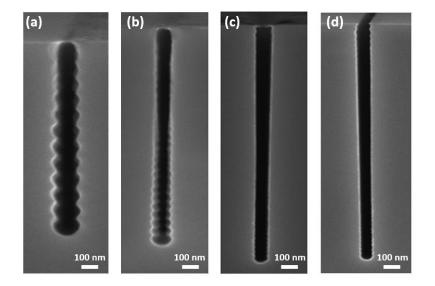

process times. For initial RIE process development, we used e-beam lithography to create well-defined trench patterns with PMMA resist (Figure 2.3 shows an example of photoresist soft mask for RIE process). It is noted that a proper e-beam exposure time (thus a better-defined pattern profile) is important to achieve smooth trench profiles. As shown in Figure 2.4, when the e-beam resist is over-dosed or under-dosed, irregular scallops or tapering effect were observed. Our best results were obtained with 700 uC/cm<sup>2</sup> dosage and 500 nm 950PMMA C4 e-beam resist.

Figure 2.3. Using photoresist as soft mask for RIE etching process.

Figure 2.4. Trench structures that were patterned by different e-beam exposures with 200 nm 950PMMA C4 e-beam resist. (a) 500 uC/cm<sup>2</sup>; (b) 600 uC/cm<sup>2</sup>; (c) 700 uC/cm<sup>2</sup>; (d) 800 uC/cm<sup>2</sup>;

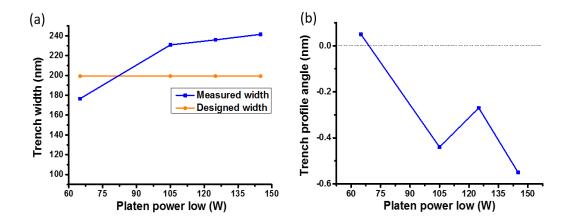

Figure 2.5. Platen power test. (a) Trench widths at middle depth with different platen powers; (b) Trench profile angles with different platen powers. All other parameters at kept the same for these tests: temperature (10 °C), etching cycle (1s  $C_4F_8$ , 1.2s  $SF_6$ , 30 loops), and 700 uC/cm<sup>2</sup> e-beam exposure dosage;

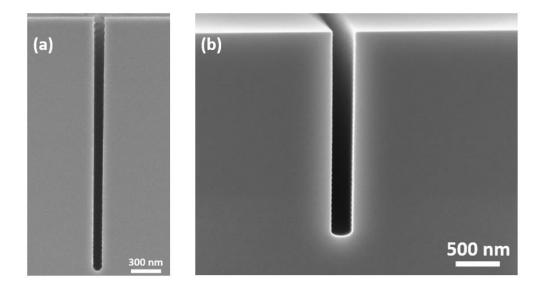

There are many RIE process parameters that have substantial impact on the etching results, including pulse numbers, platen power, and temperature, etc. We used slightly lowered temperature (10 °C) in RIE process for all our samples to avoid thermal diffusion of SF<sub>6</sub> which may reduce directional selectivity. Platen power is defined as the amount of power that SF<sub>5</sub><sup>+</sup> ions can obtain from the vertical bias applied to accelerate the ions. To study the effect of platen power on etched trench profile, we etched four samples with different platen powers, as shown in Figure 2.4. Generally, higher platen power leads to wider and more sloped trench (Plotted quantitatively in Figure 2.5). The best results were obtained with roughly 75 W lower limit and 140 W higher limit for platen power. Finally, with the optimized conditions, a 25:1 trench with slightly tapered side wall is demonstrated in Figure 2.6(a), while a 10:1 trench with perfectly vertical side wall is shown in Figure 2.6(b).

Figure 2.6. Trenches fabricated with optimized RIE processes. (a) 30:1; (b) 10:1.

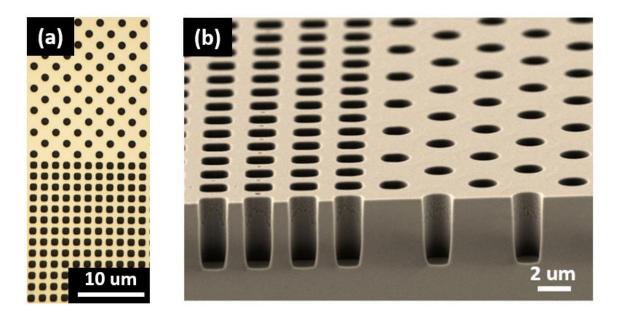

To scale up the trench fabrication with photolithography, we used a design with arrays of holes, in which holes with different diameters and pitch sized are included, as shown in Figure 2.7. An interesting phenomenon observed on this sample is that the shapes of holes vary in blocks with different hole densities, even though the shapes of photoresist mask are perfectly circular. In our observation, the hole shape can remain circular at up to 8 holes/100 um<sup>2</sup>, but become more square-like when the density reaches 32 holes/100 um<sup>2</sup>. This is possibly due to a proximity effect during the RIE process, similar to the proximity effect known in e-beam lithography processes.<sup>72</sup>

Figure 2.7. (a) Top-down optical image of the hole structures; (b) Cross-section SEM of the hole structures fabricated by photolithography and RIE process.

#### 2.3 Al-Catalyzed SiO<sub>2</sub> ALD on High-Aspect-Ratio Structures

#### 2.3.1 Al-Catalyzed SiO<sub>2</sub> ALD Process and Self-Smoothing Mechanism

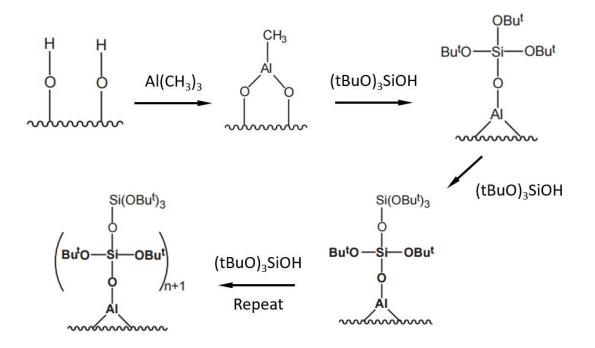

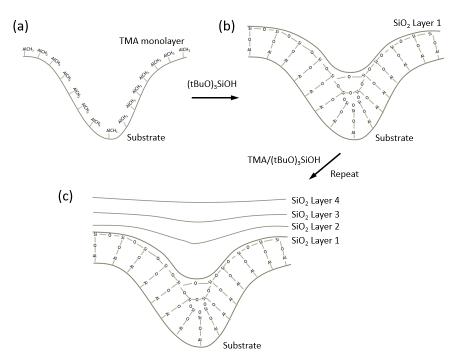

The Al-catalyzed SiO<sub>2</sub> ALD process was developed in our group in 2002, and has been put into wide use in various kinds of commercial ALD systems as a standard highefficiency SiO<sub>2</sub> deposition process.<sup>73-74</sup> As illustrated in Figure 2.8, this process involves two steps: The first step is exposing the sample surface to trimethylaluminum (TMA) vapor to form a monolayer terminated with -AlCH<sub>3</sub> groups, which is the same chemical process as in regular Al<sub>2</sub>O<sub>3</sub> ALD; The second step is introducing large or multiple doses of *tris*(*tert*-butoxy) silanol precursor onto the -AlCH<sub>3</sub> terminated surface to form silicon dioxide layers on top of it.

Figure 2.8. Al-catalyzed SiO<sub>2</sub> ALD process diagram.<sup>73</sup>

Figure 2.9. Al-catalyzing mechanism for Al-SiO<sub>2</sub> ALD process.<sup>73</sup>

Although the first step is a regular self-limited ALD process, the second step is not self-limited. After forming the first layer of -Al-O-Si(OtBu)<sub>3</sub>, the silanol precursor dosed onto the sample surface will keep reacting at the bottom Al-O-Si area and form long chains of Al-O-(Si-O)<sub>n</sub>, as shown in Figure 2.9. With the Al-catalyzing mechanism, the Al-SiO<sub>2</sub> process can happen much faster (>1 nm/cycle) than conventional ALD (~0.1 nm/cycle).

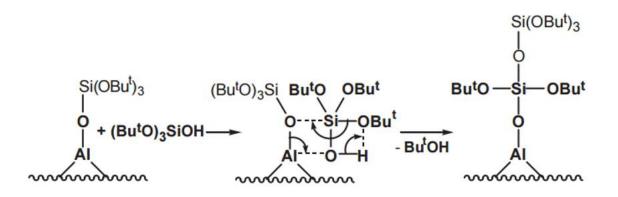

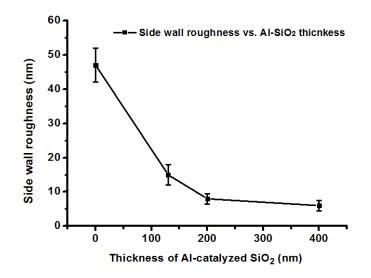

By doing Al-SiO<sub>2</sub> deposition on a zig-zag rough surface, we found that this ALD process can smooth out the rough surface as demonstrated in Figure 2.10. After deposition of ~130 nm Al-SiO<sub>2</sub>, the roughness (defined as the average height difference between the bottom to apex of the zig-zag texture) of patterned Si test substrate decreased from ~47 nm to ~15 nm (68 % decrease). We call this phenomenon the selfsmoothing effect of Al-catalyzed SiO<sub>2</sub> ALD. This effect can be observed when doing deposition onto surfaces with 20 ~ 200 nm features.

Figure 2.10. 130 nm of Al-catalyzed SiO<sub>2</sub> ALD thin film deposited onto a Si substrate with zig-zag textures on the surface, reducing the surface roughness (average peak to valley depth) 68 % from ~47 nm to ~15 nm, showing self-smoothing effect.

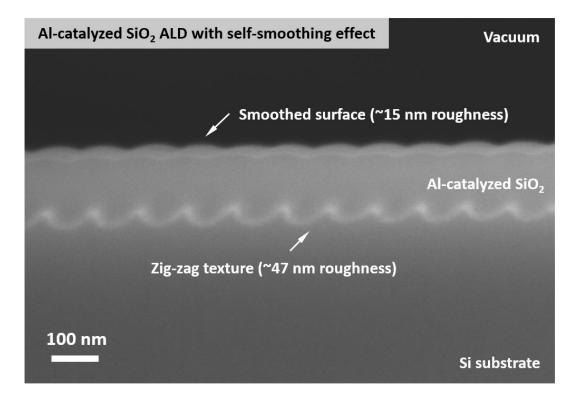

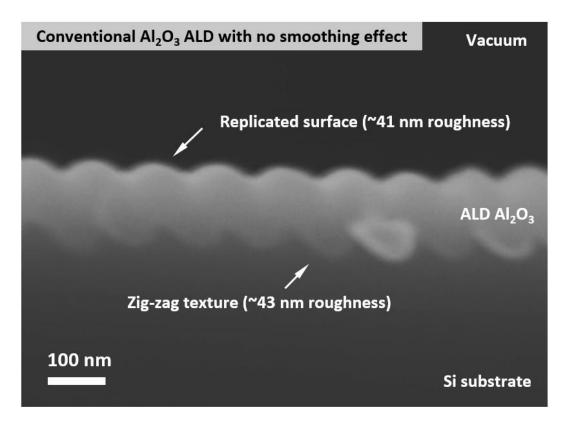

As a control experiment, we performed conventional  $AI_2O_3$  ALD with trimethylaluminum (TMA) precursor on the same sample surface. During the deposition process, substrate temperature was set to 250 °C, base pressure was 200 mTorr, and carrier gas flow is 20 sccm of N<sub>2</sub>. A cross-sectional SEM image of the resulting sample is shown in Figure 2.11. After coating the surface with ~130 nm by conventional  $AI_2O_3$  ALD, the zig-zag morphology was mostly maintained (< 5 % roughness change from 43 nm to 41 nm), indicating that this process is a strictly self-limited conformal ALD process that replicates the initial morphology of samples.

Figure 2.11. 130 nm of conventional  $Al_2O_3$  ALD (with TMA precursor) deposited onto a Si substrate with zig-zag textures on the surface, creating a mostly replicated surface with less than 5 % change in surface roughness from ~43 nm to ~41 nm.

To better understand the Al-SiO<sub>2</sub> deposition process, we propose two possible mechanisms for the self-smoothing effect. The first proposed mechanism is "concave filling", as illustrated in Figure 2.12. Al-catalyzed SiO<sub>2</sub> ALD process produces polymer-like

chains of SiO<sub>2</sub> in each cycle. When performing this deposition on a concave substrate, those SiO<sub>2</sub> chains in the valley tend to touch each other and crosslink some of the chains. Therefore, the film near the bottom of a valley will be slightly thicker than the film deposited on planar surfaces. After repeating the process for multiple layers, the valley will be gradually filled up from the bottom and smooth out the surface. This mechanism is based upon a nanometer-scale perspective (each SiO<sub>2</sub> chain formed in an Al-SiO<sub>2</sub> ALD cycle is usually 1~5 nm), which can explain that the phenomenon is mostly easily observed on substrates patterned with 20 ~ 200 nm features.

Figure 2.12. The proposed "concave filling" mechanism scheme. (a) A concave surface with a monolayer of TMA precursor attached; (b) Formation of long vertical  $SiO_2$  chains on each Al site, causing the chains near bottom to touch and terminate each other; (c) After repeating the process, the surface gradually becomes smoother.

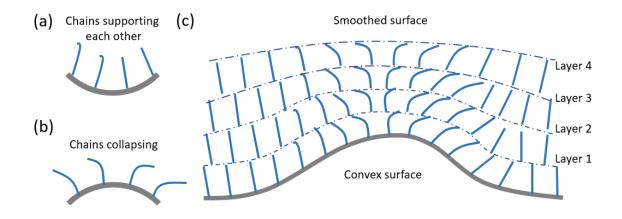

Figure 2.13. The proposed "convex collapsing" mechanism for the self-smoothing effect of Al-catalyzed SiO<sub>2</sub> ALD process. (a) SiO<sub>2</sub> chains support each other when deposited onto a concave surface; (b) SiO<sub>2</sub> chains are easier to bend and collapse when formed on a convex surface due to the lack of support from surrounding chains; (c) Illustration of the overall smoothing effect after repeating the process for multiple layers.

Another possible explanation is the "convex collapsing" mechanism. In the Alcatalyzed ALD process, long SiO<sub>2</sub> chains will have a certain degree of flexibility because each chain starts growth from a single Al center and extends upward, which is similar to the growth process of nanowires.<sup>75</sup> When formed on a concaved surface, the chains tend to mechanically support each other, and maintain a vertical growth behavior, as shown in Figure 2.13(a). However, when it comes to the scenario on a convex surface as in Figure 2.13(b), SiO<sub>2</sub> chains are growing without as much mechanical support from the surrounding chains. Thus, the chains formed on convex surfaces tend to bend and collapse, resulting in a slightly thinner film near the apex of a convex surface than the film deposited on planar surfaces.

Figure 2.13(c) schematically illustrates the smoothing process by this mechanism, in which the top layers of the deposited film are getting flatter and flatter than the original convex substrate surface. This mechanism is based on molecular-scale processes, and can explain how the Al-catalyzed SiO<sub>2</sub> ALD is different from normal ALD processes. For example, in Al<sub>2</sub>O<sub>3</sub> ALD process, TMA precursors are small enough to form a compact monolayer, and all active sites formed on both concave and convex sample surfaces have the same density, maintaining the same growth rate, thus the highly conformal deposition characteristics.

The overall self-smoothing phenomenon of Al-catalyzed SiO<sub>2</sub> may be caused by the combination of both "concave filling" and "convex collapsing" mechanisms. In short, the growth on lower parts of a rough sample surface is filled up faster than planar parts due to the geometry-induced crosslinking at the bottom, while the growth on higher part of a rough surface is slower because of the bending proneness of less-supported SiO<sub>2</sub> chains near peak areas. These mechanisms provide a qualitative explanation to the self-smoothing effect; however, more quantitative and thorough investigations are needed to better understand the process in the future.

#### 2.3.2 Smooth-Wall Ultrahigh-Aspect-Ratio Trench Structures

As mentioned in the discussion of RIE mechanism in Figure 2.2, the Bosch RIE process intrinsically produces small scallops along the side wall of etched structures. Utilizing the self-smoothing effect of the Al-catalyzed SiO<sub>2</sub> ALD process, we can fabricate high-aspectratio structures with highly smooth side-walls. Of note, deposition of a conformal thin film in a trench can produce an even higher overall aspect ratio, because the process reduces the coated trench width while keeping trench depth the same. As a result, the aspect ratio can be readily controlled by changing the thickness of a deposited Al-SiO<sub>2</sub> film, which may be a benefit for industrial applications.

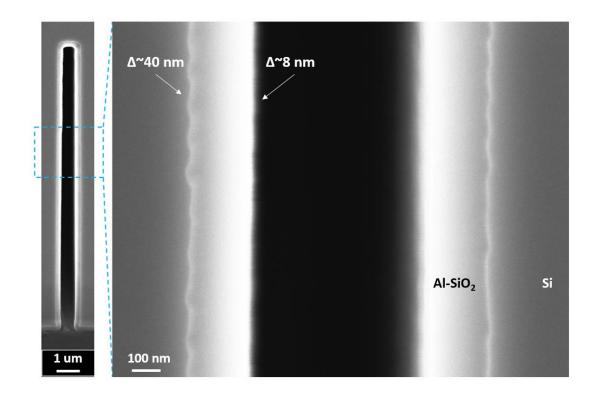

Figure 2.14. Al-catalyzed SiO<sub>2</sub> ALD reducing the side wall roughness of a rough-wall Si trench with 12:1 aspect ratio from  $\sim$ 40 nm to  $\sim$ 8 nm.

To demonstrate the application of Al-SiO<sub>2</sub> ALD for making smooth-wall, high-aspectratio structures, we fabricated Si trenches with rough side walls as test structures, and coated them with Al-SiO<sub>2</sub> ALD. In all these experiments, we used 250 °C substrate temperature, 200 mTorr base pressure, 4:1 silanol to TMA dosing ratio and 20 sccm N<sub>2</sub> carrier gas. Figure 2.14 shows the fabricated Si trench with ~40 nm surface roughness (average peak to valley depth). After coating the trench with 200 nm Al-SiO<sub>2</sub> ALD, the variation reduced substantially to ~8 nm.

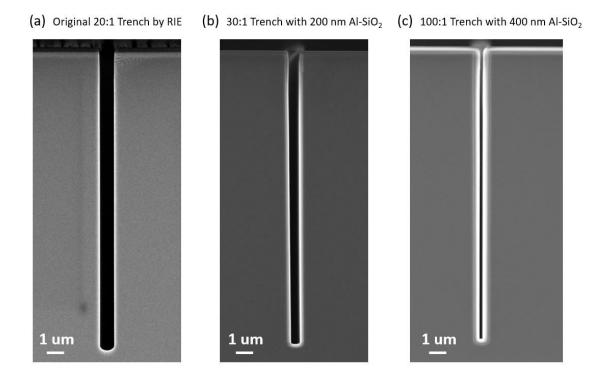

Figure 2.15. (a) Rough-walled Si trench with 18:1 aspect ratio fabricated by RIE process; (b) 30:1 aspect-ratio Si trench with smoothed wall by depositing 200 nm Al-SiO<sub>2</sub>; (c) 100:1 aspect-ratio Si trench with smoothed wall by depositing 200 nm Al-SiO<sub>2</sub>. Here we also demonstrate that highly controllable smooth-walled trenches with increased ultrahigh aspect ratios can be fabricated. Figure 2.15(a) shows an 18:1 aspect-ratio Si trench fabricated by RIE process, which has a ~40 nm side wall roughness. After depositing 200 nm Al-catalyzed SiO<sub>2</sub> ALD thin film onto the trench, the side wall roughness reduced to ~8 nm, and aspect ratio increased to 30:1, as in Figure 2.15(b). Further deposition of a total of 400 nm Al-SiO<sub>2</sub> gives a ~6 nm side wall roughness and an ultrahigh 100:1 aspect ratio, as presented in Figure 2.15(c). Al-SiO<sub>2</sub> thickness dependence of the trench side wall roughness is plotted in Figure 2.16. Of note, the trench width of the final 100:1 trench is highly uniform throughout the entire structure, indicating that this method is promising for the fabrication of smooth-wall, complex structures with even higher aspect ratios.

Figure 2.16. Trench side wall roughness versus the thickness of coated Al-SiO<sub>2</sub>. The error bar indicates the deviation of peak-to-valley depth of each scallop on trench side wall.

#### 2.4 Conclusions

In this chapter, we described fabrication processes to make smooth-wall, high-aspectratio structures based on reactive ion etching (RIE) and a self-smoothing Al-catalyzed SiO<sub>2</sub> deposition method. The Bosch RIE process is a highly effective and controllable way to create trench structures with desired width and depth, but it introduces intrinsic side wall roughness due to its cycling etching mechanism. As a solution to this issue, Alcatalyzed SiO<sub>2</sub> deposition can reduce the side wall roughness of these structures by at least 68 %, while conventional Al<sub>2</sub>O<sub>3</sub> ALD of similar thickness brings less than 5 % roughness decrease on the same structure. Moreover, coating a specific thickness of Alcatalyzed SiO<sub>2</sub> can controllably increase the overall aspect ratio of the fabricated structures up to at least 100:1. These studies provide strategies to develop evaluation platforms to study conformal thin film deposition processes, and provide methods to create high-quality complex structures for three-dimensional architectures with ultrahigh aspect ratios. Such structures could enable the production of future semiconductor electronics or optical devices.

# Chapter 3 DLE-CVD of Nano-Crystalline Cobalt Metal for Nanoscale Copper Interconnect Encapsulation

#### 3.1 Introduction

Continued progress in the downsizing of microelectronic devices has brought great challenges in many fields, especially interfacial engineering and interconnect fabrication at nanometer scales.<sup>76-77</sup> As a critical part of transmitting signals among microelectronic units, metal interconnect architectures have been calling for exponentially increased integration density and complexity in the past decades.<sup>78</sup> One of the greatest obstacles limiting the industry from further scaling down copper (Cu) interconnects, which is the most widely used interconnect material, is the electromigration (EM) and diffusion of Cu.<sup>3, 79-80</sup> Various barrier, liner and capping layers for Cu interconnects have been reported in the effort to stabilize Cu atoms by suppressing their diffusion and migration, including SiNx, SiCN and transition metal nitrides.<sup>81-83</sup>

However, when it comes to a 22 nm technology node and below, dimensions of interconnects are already less than the mean free path (MFP) of Cu (~40 nm), while Cu metal conductivity decreases exponentially as it shrinks in size below MFP due to surface and grain boundry scattering.<sup>84-86</sup> As a result, by adding several nanometers of a low conductivity tantalum nitride barrier layer (~10<sup>6</sup> S/m) onto Cu (5.96 × 10<sup>7</sup> S/m), the effective width of a Cu wire would be decreased by 10 - 20 %, thus drastically decreasing the overall conductivity of the nanoscale interconnects.<sup>87-88</sup> Therefore, a

high-conductivity metallic material with Cu stabilization functionalities is needed for further-down-sized microelectronic interconnects.

Cobalt (Co) and Co alloys are known as effective capping layers that are capable of suppressing surface electromigration of Cu at macroscopic scales.<sup>89-90</sup> Furthermore, since Co has a high bulk metallic conductivity of 1.60 × 10<sup>7</sup> S/m and an estimated MFP of only ~16 nm at room temperature, it is emerging as a promising candidate for advanced Cu liner/capping layers.<sup>91-92</sup> Traditionally, Co metal was deposited by PVD methods that do not have the capability of coating inside high-aspect-ratio structures.<sup>93</sup> Thus, metal-organic chemical vapor deposition (MOCVD) with cobalt carbonyl precursors [e.g., Co<sub>2</sub>(CO)<sub>8</sub>] was introduced for better conformality.<sup>94</sup> However, cobalt carbonyl precursors have poor thermal stability and narrow practical deposition temperature windows, and usually lead to a rough film with surface roughness rms greater than 2.2 nm.<sup>95</sup> Recently, our group reported novel direct-liquid-evaporation chemical vapor deposition (DLE-CVD) methods for metal and metal nitride thin films, which provided the feasibility to create higher-quality Co films over a wide range of deposition temperatures.<sup>39, 42</sup>

When a precursor is vaporized from a conventional bubbler, the actual rate of vapor delivery is subject to many variables, including drifts in the bubbler temperature, the amount of precursor remaining in the bubbler, and thermal decomposition during long times at high temperatures. In contrast, precursors in DLE-CVD systems are stored at room temperature, such that thermally-induced decomposition is negligible. The

residence time of the precursor vapor in the heated evaporation region is also very short, minimizing the decomposition of the precursor during the vaporization. The precursor delivery rate is stably controlled and measured by a liquid flow-controller immediately before it flows into the evaporation region.<sup>96</sup> In making nanoscale metal interconnects, it is critical to have precise control over all deposition processes in order to guarantee reliability and reproducibility. For liners and capping layers of copper interconnects, it is particularly important to design deposition conditions that create continuous and pinhole-free films with nano-sized crystallinity for blocking the diffusion of copper.<sup>97</sup>

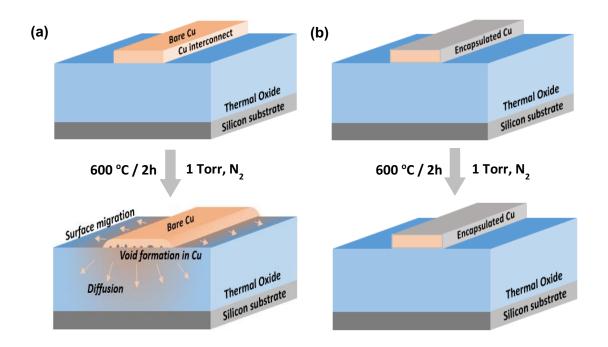

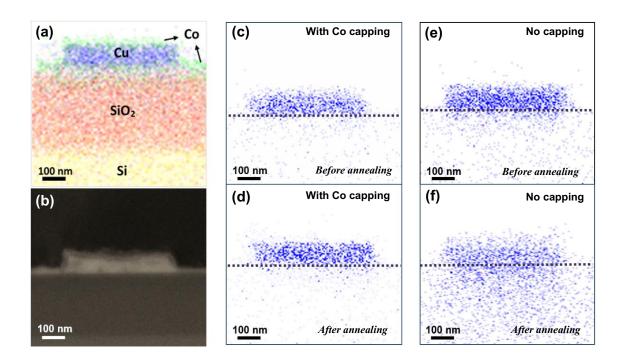

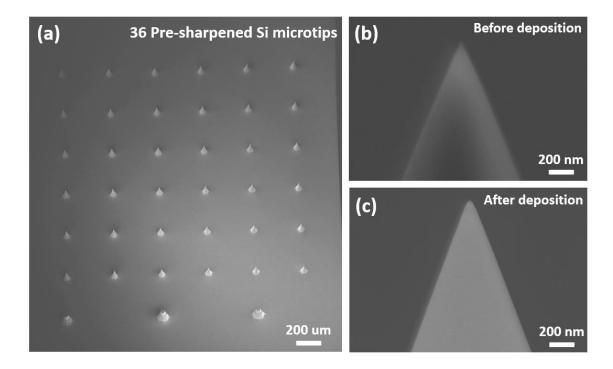

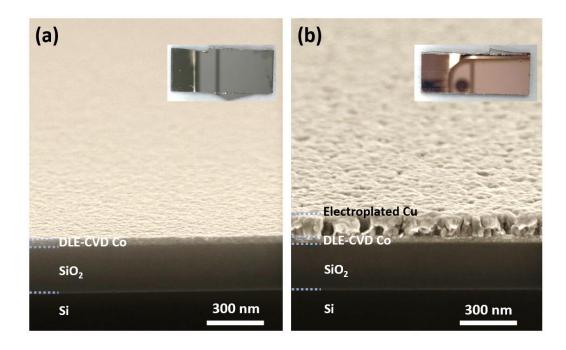

In this chapter, we use nanoscale elemental imaging and electrical measurements to demonstrate that precisely controlled DLE-CVD of Co metal films is a promising liner and capping layer for nanoscale Cu interconnects. Narrow Cu wires encapsulated allaround by DLE-CVD Co were fabricated as illustrated in Figure 3.1. In-depth study of temperature-dependent deposition characteristics and atom probe tomography (APT) analysis are conducted to understand better the kinetics of DLE-CVD Co growth and its atomic-scale morphology. Morphological studies showed that our DLE-CVD Co forms a smooth nanocrystalline film with a grain size of ~10 nm and surface roughness rms of ~0.9 nm. Electrical measurements on microcapacitors show that Cu is effectively blocked from diffusing into the SiO<sub>2</sub> dielectric layer by our DLE-CVD Co.

This work provides direct evidence that encapsulating nanoscale Cu interconnects with nanocrystalline DLE-CVD Co can substantially improve its stability and suppress

diffusion of Cu atoms, paving the way for improved Cu interconnects in advanced microelectronics.

Figure 3.1. Schematic illustration of preventing the diffusion and deterioration of nanoscale Cu interconnects by DLE-CVD Co encapsulation. (a) Bare Cu interconnect; (b) Cu interconnect with DLE-CVD Co encapsulation.

#### 3.2 Experimental Methods

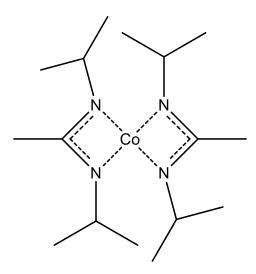

The precursor used in this work is a cobalt amidinate, bis(N,N'-

diisopropylacetamidinato) cobalt(II) (Figure 3.2), which has been reported previously.<sup>39,</sup>

<sup>43</sup> Tetradecane (Millipore Sigma Chemical Co.) was distilled from sodium to remove

moisture before use. All chemical operations were conducted in a glove box with a nitrogen atmosphere. Cobalt precursor solution was prepared by dissolving 5 g of Co precursor in 50 ml of tetradecane.

Figure 3.2. Co precursor for DLE-CVD Co depositions. Name: bis(N,N'diisopropylacetamidinato) cobalt(II).

The CVD of Co is conducted with a home-made direct-liquid-evaporation (DLE) system (Figure 3.2). During the deposition process, a precisely controlled precursor solution flow (12 wt% in tetradecane) is injected into and vaporized in a heated vaporization loop, in which a constant 100 cubic centimeters per minute (sccm) of N<sub>2</sub> is flowing as a carrier gas. Then the precursor vapor is mixed with 100 sccm purified ammonia (NH<sub>3</sub>) and 100 sccm hydrogen (H2) as co-reactant gases, and delivered into a preheated deposition chamber (16-inch long and 1.25-inch diameter) with an 11 inch × 1.25 inch semi-cylindrical sample holder inside. The total pressure in the reactor chamber is also regulated and maintained at 10 Torr, in which the partial pressures of  $NH_3$ ,  $H_2$  and  $N_2$  all equal 3.23 Torr. The Co precursor partial pressure varied from 0.02 Torr to 0.08 Torr in this work. Based on the calculation of reaction zone volume and flow rates, it takes roughly 13 s for a precursor molecule to be delivered across the reaction zone on statistical average.

Figure 3.3. DLE-CVD Co System Diagram.

In order to evaluate the copper barrier performance of DLE-CVD Co, a p-type silicon chip with 50 nm thermal oxide layers was coated with 10 nm DLE-CVD Co at 200 °C followed by 50 nm PVD Cu, then annealed at 600 °C for 1 hour under 1 Torr of flowing N<sub>2</sub>. After annealing, the Cu and Co films were removed by wet etching to fabricate micro-capacitors. 50 um x 50 um square-shaped Au electrodes were then fabricated by standard photolithography, metallization and lift-off process. For comparison, nonannealed samples were also fabricated into micro-capacitors. The micro-capacitors were measured by a probe station with a Keysight E4980A precision LCR meter. Capacitance versus voltage (C-V) characteristics were measured at 2 MHz with a sweep rate of 0.2 V/s. All measurements started at positive 5 V and scanned from positive bias toward negative bias.

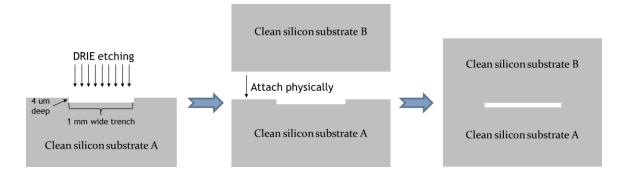

The cross-sectional morphology of the films was visualized with a Zeiss Ultra Plus field-emission scanning electron microscope (FE-SEM), from which the thickness of each film was measured. A Zeiss Ultra55 with EDAX detector was used to acquire EDAX mapping images. The depth-profile elemental analysis was carried out by Thermo Scientific K-Alfa X-ray photoelectron spectroscopy (XPS). A JEOL 2100 transmission electron microscope was used to study microscopic crystallography for which the samples were prepared onto a TEM grid with an ultrathin silicon nitride membrane. Xray diffraction patterns were acquired by a Bruker D2 Phaser. Surface morphology of the films was analyzed by atomic force microscopy (AFM) (Asylum Model MFP-3D AFM system). Step coverage evaluation of DLE-CVD Co was conducted on a planar trench structure. The fabrication process for the planar trench test structure will be discussed in the next section. Nanoscale Cu lines for the demonstration of Co encapsulation were patterned by an Elionix F-125 ultra-high precision electron beam lithography system, and metallized by electron beam evaporation of Cu.

#### 3.3 Characterizations of Nano-Crystalline Cobalt Thin Films

#### 3.3.1 Growth Characteristics

For better understanding of the deposition process of DLE-CVD cobalt metal, we conducted a series of temperature-dependent studies. In all depositions, co-reactant gas flows are set to be 100 sccm  $NH_3$  and 100 sccm  $H_2$ , and the precursor solution concentration is fixed at 12 wt%, which were evaluated to be the best conditions for high conformality and smoothness according to our previous report.<sup>39</sup>

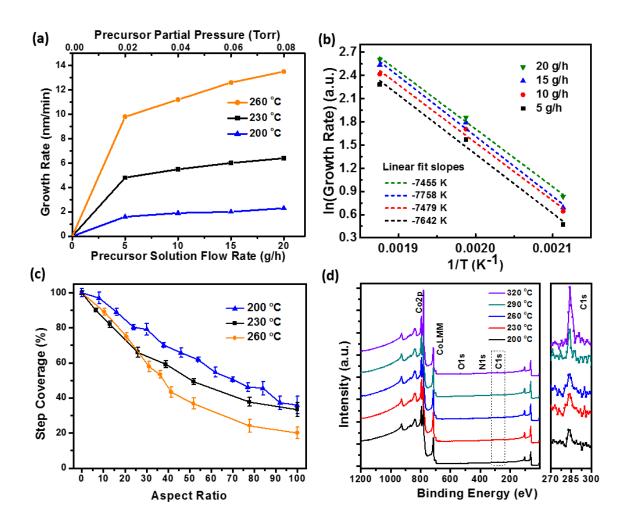

Figure 3.4(a) plots the growth rates of DLE-CVD Co versus precursor solution flow rates at different temperatures. The results show that our deposition process is highly controllable by precisely setting precursor flow rates and temperatures. A lower temperature with a lower flow rate is suitable for nano-scale applications such as local interconnect and nanoscale capping layer, while a higher temperature with higher flow rate is favorable for larger-scale coatings such as intermediate and global interconnects in 3D microelectronics.<sup>81</sup> By plotting the natural logarithm of growth rate versus the reciprocal of temperature as shown in Figure 3.4(b), we calculated the activation energies of Co deposition processes with different precursor flow rates based on the Arrhenius' equation. Activation energy of the Co DLE-CVD deposition process is estimated to be  $63.1 \pm 1.2$  kJ/mol on silicon substrates, which is in accordance with previous reports on thermal oxide substrates.<sup>98-99</sup>

Figure 3.4. (a) Precursor flow-dependent growth rate plot at different deposition temperatures; Total pressure is 10 Torr in all experiments; (b) Arrhenius plots and linear fits at different precursor flow rates; (c) Step coverage along a horizontal trench test structure; (d) XPS survey scans of DLE-CVD Co samples deposited at different temperatures; the boxed region is the C1s peak, which is magnified on the right side.

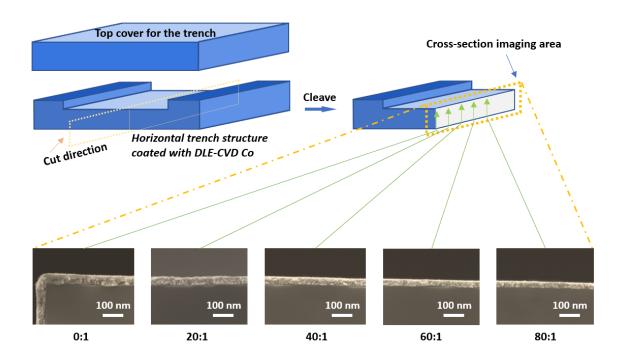

Figure 3.5. Schematic flow chart (cross-section view) of the fabrication process of

horizontal trench test structures on which step coverage evaluation for our DLE-CVD Co

deposition process is conducted.

Figure 3.6. Cross-section SEM image of the planar trench test structure.

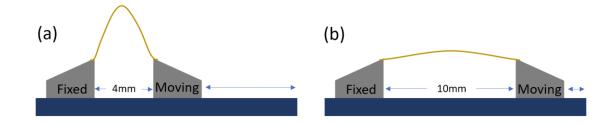

To demonstrate the step coverage of our DLE-CVD Co films, we developed a parallel trench structure with an ultrahigh aspect ratio as a test platform, as illustrated in Figure 3.5. In the fabrication process, a flat silicon chip was first coated with 2 um of positive photoresist as a soft mask, and patterned with 500 um wide 0.5 cm long exposed lines

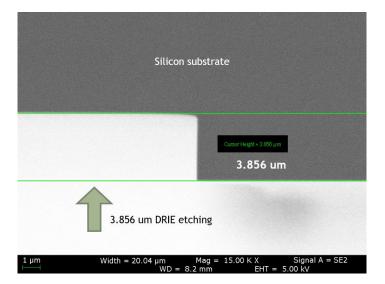

by photolithography. A 500 um wide, ~3.86 um deep shallow trench (Figure 3.6) was created by a Bosch-type deep silicon reactive ion etching (DRIE) process with SF<sub>6</sub> and  $C_4F_6$  gases, and thoroughly cleaned afterwards. Finally, the chip was physically capped with another flat silicon chip to cover part of the 0.5 cm length, leaving one end exposed as the opening of the parallel deep trench.

Figure 3.7. Schematic illustration of the assessment of step coverage on the horizontal trench test structure. The test structure was coated with DLE-CVD Co, then cleave along the direction of the horizontal trench. Then cross-section SEM imaging at different depth with different aspect ratios were conducted and measured thickness of Co layer. The DLE-CVD Co sample shown in the images was deposited at 200 °C.

Co films were then deposited on the test structure by DLE-CVD at various temperatures at a constant precursor flow rate of 5 g/h. Cross-section SEM images were acquired to measure film thickness at different depths (as in Figure 3.7), showing that our 200 °C film has over 95 % step coverage at a 10:1 aspect ratio, and maintains 50 % step coverage even at a 70:1 aspect ratio. Moreover, based on the results shown in Figure 3.4(c), 230 °C and 260 °C films both have over 90 % step coverage at a 10:1 aspect ratio, and maintain 50 % step coverage at 60:1 and 35:1 aspect ratios, respectively.

#### 3.3.2 Composition of DLE-CVD Co

In addition to high deposition rate and high conformality, low impurity level, e.g., low carbon level, is also required for intermediate and global level interconnects because carbon content can decrease the conductivity of metal interconnects, thus increasing the energy consumption of overall device.<sup>12, 67</sup> X-ray photoelectron spectra (XPS) of DLE-CVD Co samples deposited at different temperatures are provided in Figure 3.4(d). All spectra are taken after 100 s of 100 eV Ar<sup>+</sup> sputtering to remove surface contamination. Substantial amounts of C (>5 at%) are only observed in the samples deposited at above 290 °C. Samples deposited at temperatures up to 230 °C show less than about 1 at% of C contamination. To estimate the impact of C content on DLE-CVD Co, we measured the conductivity of Co films with different C contents, which is discussed in the supporting information Table 3.1. The results show that the resistivity substantially increased when

the C content rose above 2 at%, indicating that the DLE-CVD Co films deposited at lower than 230 °C (< 1 at% carbon shown by XPS) will be more promising to achieve better performance as interconnect materials.

| Deposition Temperature (°C) | 200 | 230 | 260 | 290 |

|-----------------------------|-----|-----|-----|-----|

| Carbon Content (at%)        | < 1 | < 2 | 5   | 15  |

| Resistivity (µOhm∙cm)       | 25  | 30  | 100 | 195 |

Table 3.1. Resistivity of DLE-CVD Co with different carbon contents

## 3.3.3 Crystallinity and Morphology Studies of DLE-CVD Co

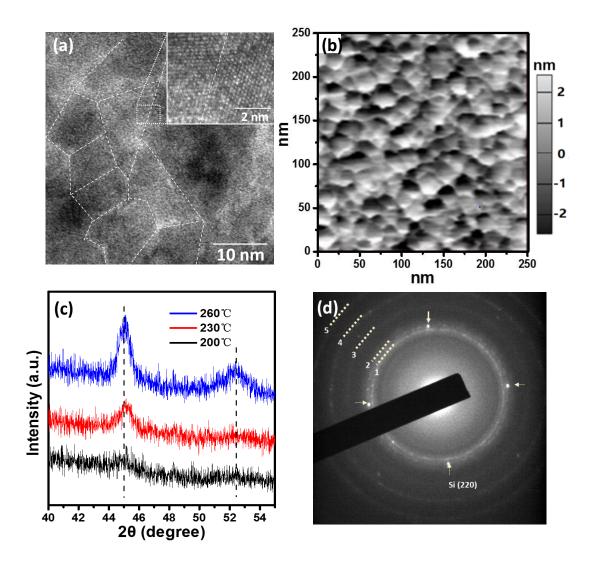

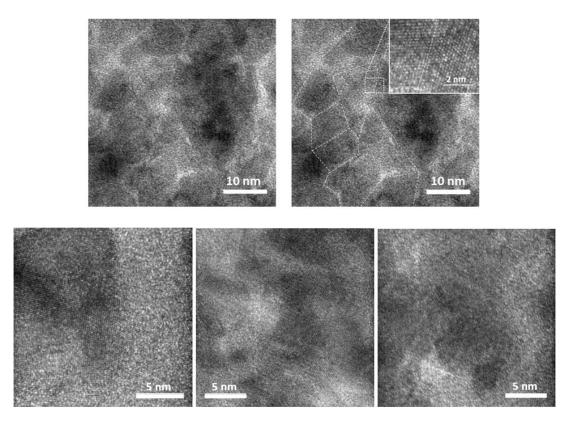

For Cu liner/capping layer applications, it is important to develop nanocrystalline Co films to ensure smooth surface coverage of Cu wires. APT results demonstrate the ultrahigh purity and uniformity of our 200 °C DLE-CVD Co film, but do not provide information about microscopic surface morphology and crystallography. To study these characteristics, we performed transmission electron microscopy (TEM) and atomic force microscopy (AFM) imaging on the 200 °C sample. TEM image shown in Figure 3.8(a) reveals that the film is a nanocrystalline material with a grain size of around 10 nm. High-resolution imaging of lattice alignments at the grain boundary is included as the inset of Figure 3.8(a). More high-resolution TEM images are also provided in Figure 3.9. Tapping-mode AFM surface scan (Figure 3.8b) shows a rms surface roughness of ~0.9 nm, indicating that our DLE-CVD process produces highly smooth Co metal film.

Figure 3.8. (a) TEM image showing the grain distribution of DLE-CVD Co deposited at 200 °C; (b) Tapping-mode AFM image of DLE-CVD Co deposited at 200 °C; (c) XRD pattern of DLE-CVD Co deposited at different temperatures, showing peak broadening at lower temperatures due to the formation of nanocrystallines; (d) ED pattern of DLE-CVD Co deposited at 200 °C, in which the 4 marked dots belong to Si (220) reference.

Figure 3.9. High-resolution TEM images of DLE-CVD Co deposited in 200 °C. Top two images show crystal domains without and with dashed lines as indicators of domain boundaries; Bottom three images are additional high-res TEM images in nearby areas.

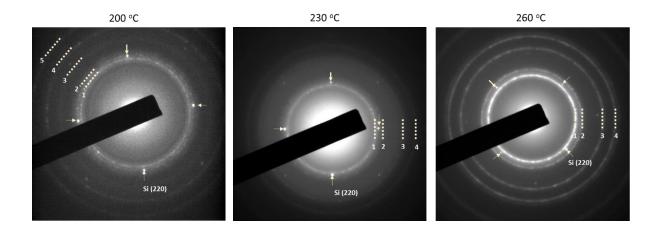

X-ray diffraction (XRD) patterns of samples deposited at different temperatures (Figure 3.8c) reveal that with lower deposition temperatures, the DLE-CVD Co tend to form smaller-sized nanocrystals. Figure 3.8(d) presents the electron diffraction (ED) pattern of the 200 °C DLE-CVD Co sample, in which five major rings are observed. More ED patterns for DLE-CVD Co samples deposited at 200 °C, 230 °C and 260 °C are also presented in Figure 3.10.

Figure 3.10. Electron Diffraction patterns for DLE-CVD Co samples deposited at different temperatures.

Based on these ED results, experimental and theoretical lattice parameters are summarized in Table 3.2 (200 °C), Table 3.3 (230 °C) and Table 3.4 (260 °C). Therefore, in Figure 3.8(d), ring 2 and ring 3 belong to hcp-Co (JCPDS 71-4239), ring 4 and ring 5 belong to fcc-Co (JCPDS 15-0806), and both phases contribute to the appearance of ring 1. Those results reveal that our 200 °C DLE-CVD Co film is a mixed phase of fcc-Co and hcp-Co, which is in accordance with our previous report.<sup>39</sup> When higher deposition temperatures are applied, only fcc-Co phase is observed. We hypothesize that the competing growth between hcp-Co (low-temperature phase) and fcc-Co (hightemperature phase) induced lattice frustration and suppressed the growth of larger crystals, producing nanocrystalline films, which are favorable for Cu liner/capping applications.<sup>100-101</sup> Table 3.2. Theoretical and experimental lattice parameters for a 200 °C DLE-CVD Co film from TEM electron diffraction results. The indices of planes (hkl) and interplanar spacings (d) are from the reference crystal structures of fcc-Co (JCPDS Card No.15-0806), hcp  $\alpha$ -Co (JCPDS Card No. 71-4239).

|     | Theoretical value |      |           | Experimental value |                      |                  |        |

|-----|-------------------|------|-----------|--------------------|----------------------|------------------|--------|

|     | FCC β-Co          |      | Ηср α- Со |                    | Temperature = 200 °C |                  |        |

| No. | hkl               | d(A) | hkl       | d(A)               | Ring no.             | Calculated d (A) | error  |

| 1   | 111               | 2.05 | 002       | 2.03               | 1                    | 2.0679           | 0.87%  |

| 2   |                   |      | 101       | 1.92               | 2                    | 1.9071           | -0.67% |

| 3   |                   |      | 102       | 1.48               | 3                    | 1.5307           | 3.43%  |

| 4   | 220               | 1.25 |           |                    | 4                    | 1.2636           | 1.09%  |

| 5   | 311               | 1.07 |           |                    | 5                    | 1.0998           | 2.79%  |

Table 3.3. Theoretical and experimental lattice parameters for a 230 °C DLE-CVD Co film from TEM electron diffraction results. The indices of planes (hkl) and interplanar spacings (d) are from the reference crystal structures of fcc-Co (JCPDS Card No.15-0806)

|     | Theoretical value |      | Experimental value   |                  |        |  |

|-----|-------------------|------|----------------------|------------------|--------|--|

|     | FCC β-Co          |      | Temperature = 230 °C |                  |        |  |

| No. | hkl               | d(A) | Ring no.             | Calculated d (A) | error  |  |

| 1   | 111               | 2.05 | 1                    | 2.0523           | 0.11%  |  |

| 2   | 200               | 1.77 | 2                    | 1.7884           | 1.04%  |  |

| 3   | 220               | 1.25 | 3                    | 1.255            | 0.40%  |  |

| 4   | 311               | 1.07 | 4                    | 1.0676           | -0.22% |  |

Table 3.4. Theoretical and experimental lattice parameters for a 260 °C DLE-CVD Co film from TEM electron diffraction results. The indices of planes (hkl) and interplanar spacings (d) are from the reference crystal structures of fcc-Co (JCPDS Card No.15-0806)

|     | Theoretical value |      | Experimental value   |                  |       |  |

|-----|-------------------|------|----------------------|------------------|-------|--|

|     | FCC β-Co          |      | Temperature = 260 °C |                  |       |  |

| No. | hkl               | d(A) | Ring no.             | Calculated d (A) | error |  |

| 1   | 111               | 2.05 | 1                    | 2.0523           | 0.11% |  |

| 2   | 200               | 1.77 | 2                    | 1.8355           | 3.7%  |  |

| 3   | 220               | 1.25 | 3                    | 1.259            | 0.72% |  |

| 4   | 311               | 1.07 | 4                    | 1.0863           | 1.52% |  |

## 3.4 Evaluation of DLE-CVD Co as Liner Material for Cu Interconnects

#### 3.4.1 Co Liner Against Cu Diffusion

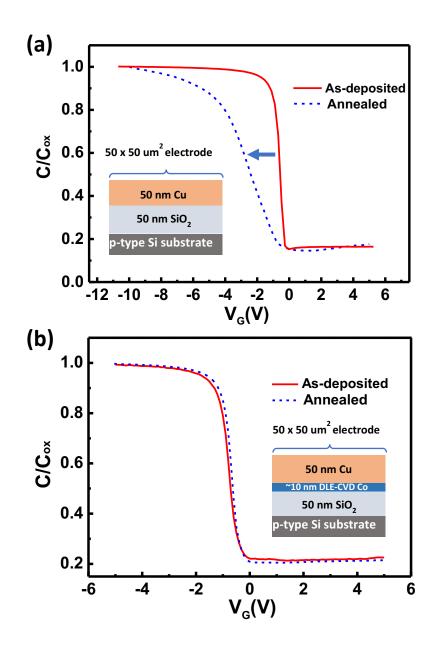

Based on the Co-Cu phase diagram, Co and Cu do not diffuse into each other at temperatures below 700 K, and only partially intermix at temperatures up to 1000 K from the thermodynamic point of view.<sup>102</sup> With high conformality, uniformity and smoothness, our nanocrystalline Co films have appropriate properties to be used as an effective copper barrier and capping layer for Cu interconnects in microelectronics.<sup>92, 103</sup> In order to evaluate the copper barrier performance of our DLE-CVD Co, capacitancevoltage (C-V) characteristics of Cu/Co/SiO<sub>2</sub>/Si and Cu/SiO<sub>2</sub>/Si systems were studied both before and after annealing at 600 °C. Fabrication details of the micro-capacitors are described in the experimental section.

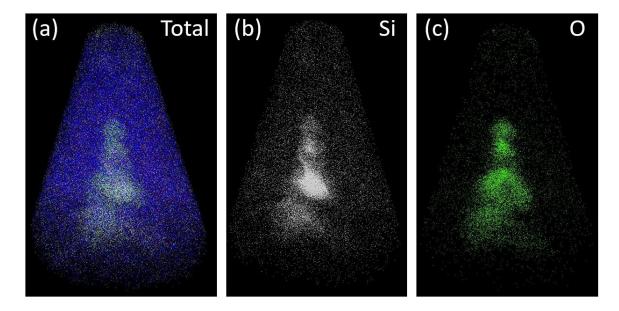

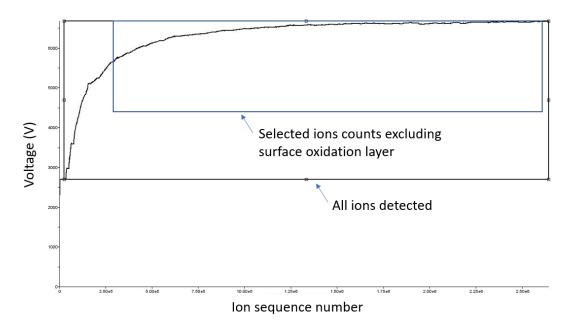

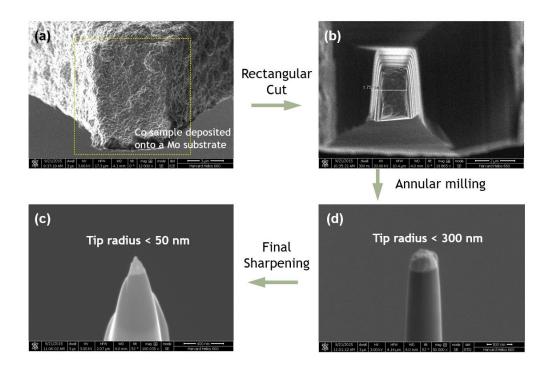

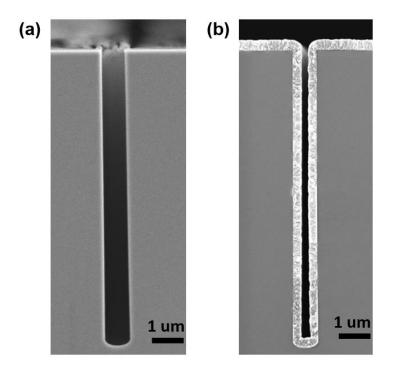

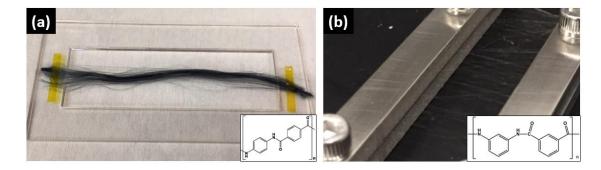

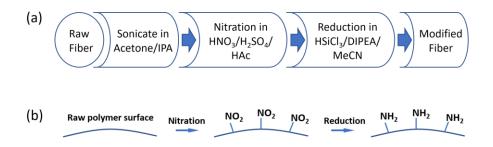

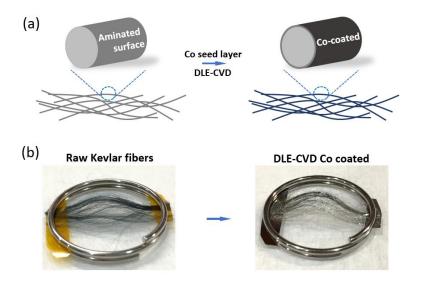

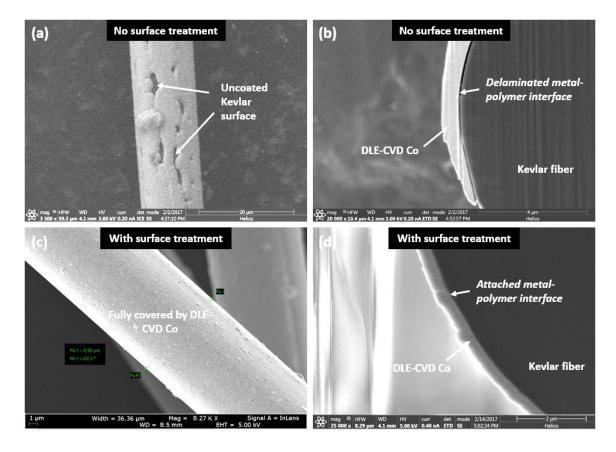

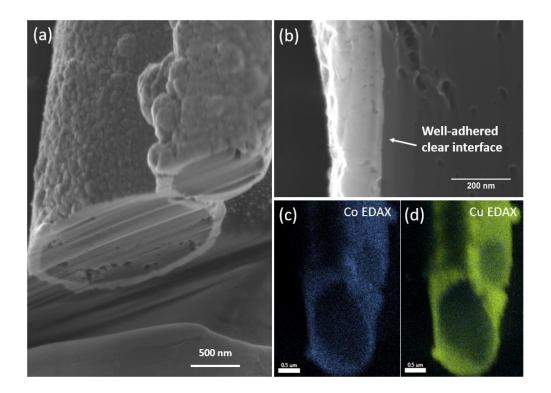

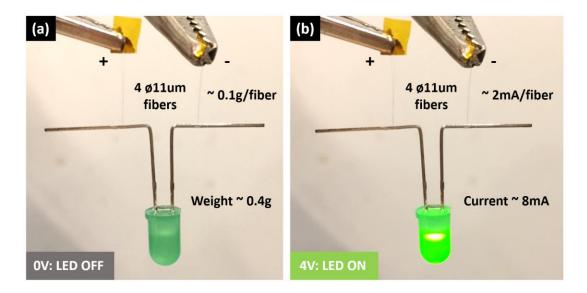

Figure 3.11. C-V measurements on microcapacitor structures for the evaluation of Cu blocking capability. (a) Cu/SiO<sub>2</sub>/Si system, showing ~2 V shift to the negative side; (b) Cu/Co/SiO<sub>2</sub>/Si system, showing no observable shift of C-V curve. All measurements started at positive 5 V and scanned from positive bias toward negative bias.